概述

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

并行接口包括兩種數字編碼方式:帶符號數signed與無符號數unsigned。本文還將介紹使用不同編碼方式的ADC與DAC時需要注意的問題。

接口協議

以ADI公司的32M、8位ADC芯片AD9280和125M、8位DAC芯片AD9708為例(這是淘寶上最容易買到的AD/DA模塊)。

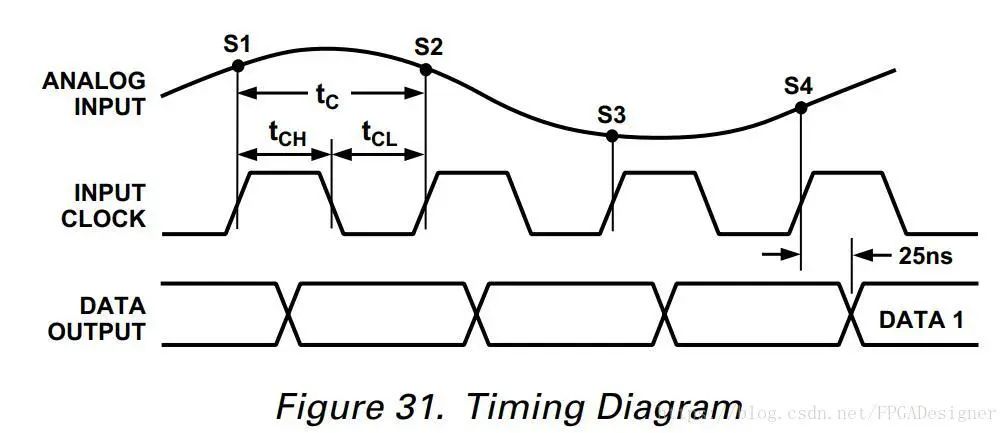

AD9280的時序圖如下:

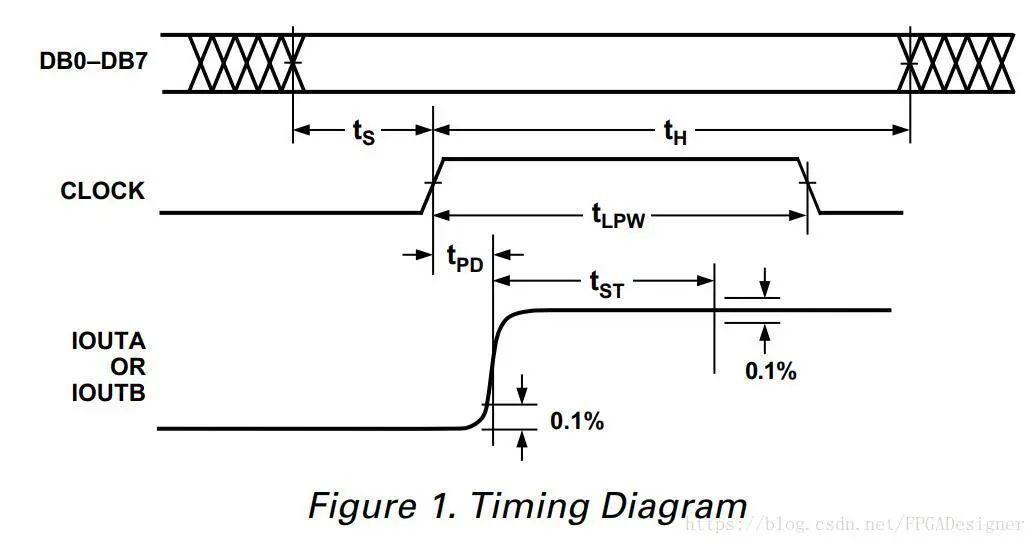

AD9708的時序圖如下:

由時序圖可知,AD9280在每個輸入clock的上升沿對輸入的模擬信號做一次采集,采集數據由數據總線data輸出;AD9708也是在每個輸入clock的上升沿讀取數據總線DB0-DB7上的數據,將其轉換為相應的電流IOUTA/IOUTB輸出。

這兩個芯片的管腳雖然很多,但大多數都是與硬件設計有關。其實幾乎所有的并行ADC和并行DAC與FPGA之間的接口只有一條時鐘線與一組數據總線,數據總線的位寬即為ADC/DAC的位數。每個時鐘周期ADC都會完成一次采集(DAC完成一次輸出),因此時鐘頻率也就是ADC和DAC的采樣頻率。

FPGA設計

并行ADC和DAC的接口時序驅動非常簡單,只要利用Quartus或Vivado自帶的時鐘管理IP核生成預期采樣頻率的時鐘信號,驅動時鐘線,從數據總線上讀出或寫入數據即可。

比如下面的代碼實現了將ADC采集到的數據再通過DAC輸出

`timescale 1ns / 1ps

//-----------------------------------------------

// 將ADC采集到的數據通過DAC輸出

//-----------------------------------------------

module adda_test

(

input clk,

output daclk,

output [7:0] dadata, //DA data

output adclk,

input [7:0] addata //AD data

);

PLL PLL_inst

(

.clk_in1(clk), // IN

// Clock out ports

.clk_out1(adclk), // OUT 32Mhz

.clk_out2(daclk), // OUT 32Mhz

// Status and control signals

.reset(1'b0), // IN

.locked()

);

assign dadata = addata;

endmodule

上述代碼中實例化了一個PLL IP核產生ADC和DAC所需頻率的時鐘,Quartus中該IP核叫做“PLL”,Vivado中該IP核叫做“Clocking Wizard”。

為了保證DAC輸出與ADC采集到的信號相同,將兩者時鐘頻率設置相同,且連接二者的數據總線。上述代碼可以使用開發板和AD/DA模塊進行實際測試。

編碼方式問題

上文用到的AD9280和AD9708都是無符號數編碼,而我們知道無論是Vivado還是Quartus中大多數的IP核采用的都是帶符號數二進制補碼的編碼方式,這就導致ADC/DAC的數據總線不能與IP核接口直接對接,必須做一定的轉換處理。

考慮到上述數字系統的特點,市場上也存在不少以帶符號數二進制補碼接口的ADC/DAC,比如65M、12位ADC芯片AD9226。如果使用這種編碼方式的芯片,數據總線就可以直接與IP核接口對接,不需要做特殊處理。

但是,我們總會不可避免的遇到類似這樣的情況:

1. ADC或DAC是無符號數編碼,而設計中需要使用一些帶符號數接口的IP核;

2. ADC是帶符號數編碼,而設計中僅需獲取測量值,并不需要與其它帶符號數接口的模塊對接。

當遇到情況1時,需要進行無符號數編碼與帶符號數編碼之間的轉換。將ADC采集到的8位無符號數轉換為帶符號數補碼形式的代碼如下:

/**** 將addata轉化為帶符號二進制補碼形式 ****/

reg [7:0] ad_data;

always @ (posedge clk or negedge rst_n)

if (!rst_n) ad_data <= 8'd0;

else ad_data <= addata - 128;? ? //AD9280采集輸入

將帶符號數補碼轉換為8位無符號數通過DAC輸出的代碼如下:

/**** 將dadata轉化為無符號數形式 ****/

reg [7:0] da_data;

always @ (posedge clk or negedge rst_n)

if (!rst_n) da_data <= 8'd0;

else da_data <= dadata + 128;? ? //AD9708輸出

當遇到情況2時,需要將不易直接觀察的帶符號數補碼形式轉換為帶符號數原碼形式,使其更加直觀。代碼如下:

always @(posedge ad_clk) //AD9226采集

if(ad_ch1[11]==1'b1) begin //如果是負電壓

ch1_reg<=12'hfff - ad_ch1 + 1'b1;

ch1_sig <= 45;? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //'-' asic碼

end

else begin

ch1_reg<=ad_ch1;

ch1_sig<=43;? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //'-' asic碼

end

轉換的依據是一個簡單的運算關系:“補碼的整數值”+“原碼絕對值的整數值”=2^B,B為位寬。比如帶符號數原碼1110的補碼為1010:1110取絕對值0110為6;1010為10,二者加起來為2^4=16。

上述代碼便是利用了這個運算關系。為了節省位寬,先用12’hfff減掉補碼,再加1,達到同樣的效果,得到帶符號數原碼的絕對值。根據符號位便可以知道這個原碼的正負情況。

原文標題:FPGA學習—并行ADC與DAC

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1638文章

21856瀏覽量

609695 -

adc

+關注

關注

99文章

6579瀏覽量

547118 -

dac

+關注

關注

43文章

2330瀏覽量

192367

原文標題:FPGA學習—并行ADC與DAC

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的ARM并行總線設計與仿真分析

請問如何使用fx3芯片來對FPGA進行并行配置?

fpga基礎篇(二):三大并行結構

請問是否有并行ADC或并行DAC接口卡讓我能夠使用FX2 FMC連接器連接到FPGA板?

FPGA電源設計在并行工程中的應用

如何使用FPGA驅動并行ADC和DAC芯片,使用不同編碼方式的ADC與DAC時的注意事項

評論