FPGA可重構(gòu)技術(shù)就是通過上位機(jī)控制在FPGA運(yùn)行過程中加載不同的Bitstream文件,F(xiàn)PGA芯片根據(jù)文件內(nèi)的不同邏輯將內(nèi)部的資源全部或部分進(jìn)行重新配置以達(dá)到多種功能任務(wù)動(dòng)態(tài)切換的目標(biāo),從而提高了使用FPGA進(jìn)行開發(fā)的靈活度。

FPGA芯片本身就具有可以反復(fù)擦寫的特性,允許FPGA開發(fā)者編寫不同的代碼進(jìn)行重復(fù)編程,而FPGA可重構(gòu)技術(shù)正是在這個(gè)特性之上,采用分時(shí)復(fù)用的模式讓不同任務(wù)功能的Bitstream文件使用FPGA芯片內(nèi)部的各種邏輯資源,使得同一個(gè)邏輯電路在不同時(shí)間段上加載不同的功能模塊。從時(shí)間軸上看,系統(tǒng)的每一項(xiàng)任務(wù)功能在FPGA芯片上依次執(zhí)行,系統(tǒng)的整體功能全部得以實(shí)現(xiàn)。從局部看,F(xiàn)PGA只執(zhí)行了一項(xiàng)小任務(wù),而從整體看,F(xiàn)PGA完成了整個(gè)系統(tǒng)任務(wù)。使用一塊FPGA芯片完成了需要多塊FPGA芯片的任務(wù),由此可見FPGA內(nèi)部資源的利用率得到很大提升。

FPGA上的可重構(gòu)技術(shù)根據(jù)FPGA芯片內(nèi)部的不同結(jié)構(gòu)可以分為兩種,分別是動(dòng)態(tài)可重構(gòu)和靜態(tài)可重構(gòu)。如果FPGA芯片是常規(guī)的SRAM結(jié)構(gòu),那么它只能做到靜態(tài)可重構(gòu),重構(gòu)過程必須首先發(fā)送中斷指令停止正在運(yùn)行的程序,之后再把全新的Bitstream文件加載到FPGA上。而如果FPGA芯片是特殊結(jié)構(gòu),那么它就可以進(jìn)行動(dòng)態(tài)可重構(gòu),重構(gòu)過程可以在FPGA運(yùn)行時(shí)期進(jìn)行,動(dòng)態(tài)可重構(gòu)不但可以在系統(tǒng)運(yùn)行時(shí)期隨時(shí)改變模塊參數(shù),甚至可以在系統(tǒng)運(yùn)行時(shí)期在FPGA內(nèi)部的可重構(gòu)區(qū)域動(dòng)態(tài)重構(gòu)電路邏輯。

FPGA的動(dòng)態(tài)可重構(gòu)又可以分為動(dòng)態(tài)全局可重構(gòu)和動(dòng)態(tài)局部可重構(gòu)。動(dòng)態(tài)全局可重構(gòu)是指上位機(jī)給FPGA芯片加載一個(gè)全新的配置文件,而這個(gè)配置文件包含了新的任務(wù)需求所要涉及的整片F(xiàn)PGA內(nèi)所有資源,從而實(shí)現(xiàn)FPGA重新配置,上一個(gè)任務(wù)實(shí)現(xiàn)的所有邏輯電路將全部消除。在重構(gòu)操作執(zhí)行前,首先在外掛存儲(chǔ)器中加載多個(gè)不同任務(wù)需求的配置文件,同時(shí)每個(gè)配置文件中都包含該任務(wù)所需要涉及的FPGA芯片全部邏輯資源。正是因?yàn)槊恳粋€(gè)配置文件都包含了整塊FPGA芯片的所有資源,所以動(dòng)態(tài)全局可重構(gòu)只能從外掛存儲(chǔ)器中選擇將一個(gè)配置文件加載到FPGA芯片中。當(dāng)這個(gè)配置文件對(duì)應(yīng)的任務(wù)結(jié)束后,再選擇另一個(gè)新的配置文件加載到FPGA芯片中,通過不同配置文件的分時(shí)加載實(shí)現(xiàn)系統(tǒng)功能任務(wù)的切換。

這種動(dòng)態(tài)全局可重構(gòu)的實(shí)現(xiàn)方式比較容易,只需要在配置文件中寫入該功能任務(wù)所包含的FPGA全部資源,但是這種實(shí)現(xiàn)方式因?yàn)榘抠Y源而導(dǎo)致文件較大,配置的時(shí)間也就相應(yīng)變長。尤其是在兩個(gè)功能任務(wù)對(duì)應(yīng)的邏輯電路相差不大的配置文件先后進(jìn)行重構(gòu)時(shí),本可以只改變相差部分的邏輯電路,卻要對(duì)FPGA芯片內(nèi)部的全部資源重新進(jìn)行改變。

相比于動(dòng)態(tài)全局可重構(gòu),動(dòng)態(tài)局部可重構(gòu)具有更大的靈活性。它只需要針對(duì)兩個(gè)功能需求之間不同的部分邏輯功能生成配置文件,并加載到FPGA中指定的可重構(gòu)區(qū)域進(jìn)行重新配置,而在FPGA中指定的靜態(tài)區(qū)域中的邏輯電路并不需要發(fā)生改變。假設(shè)一個(gè)系統(tǒng)要先后切換兩個(gè)功能,而這兩個(gè)功能需要使用4個(gè)配置文件。其中功能1需要使用配置文件1、配置文件2和配置文件3,功能2需要使用配置文件1和配置文件4。由于配置文件1在功能1和功能2中都需要,因此首先向FPGA的靜態(tài)區(qū)域加載兩個(gè)功能都需要的配置文件1,然后在可重構(gòu)區(qū)域加載配置文件2和配置文件3。功能1運(yùn)行結(jié)束后切換成功能2,由于配置文件1在功能2中仍然需要,因此在動(dòng)態(tài)局部可重構(gòu)中只需要將之前加載到FPGA可重構(gòu)區(qū)域的配置文件2和配置文件3對(duì)應(yīng)的邏輯電路消除,重新加載配置文件4生成對(duì)應(yīng)的邏輯電路就可以完成功能2的運(yùn)行。在兩個(gè)功能切換的過程中配置文件1所在的靜態(tài)區(qū)域并沒有發(fā)生改變。

動(dòng)態(tài)局部可重構(gòu)因?yàn)橹恢貥?gòu)部分區(qū)域,所以配置文件中的重構(gòu)內(nèi)容也相應(yīng)變小,重構(gòu)時(shí)間也隨之縮短。但是動(dòng)態(tài)局部可重構(gòu)的難點(diǎn)在于靜態(tài)區(qū)域和可重構(gòu)區(qū)域的大小劃分是否可以滿足系統(tǒng)功能要求、分別處在兩個(gè)區(qū)域的模塊之間如何進(jìn)行通信以及如何在可重構(gòu)區(qū)域進(jìn)行合理的布局布線。因此使用動(dòng)態(tài)局部可重構(gòu)的實(shí)現(xiàn)過程相對(duì)復(fù)雜。

審核編輯 :李倩

-

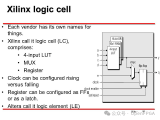

FPGA

+關(guān)注

關(guān)注

1638文章

21883瀏覽量

610732 -

芯片

+關(guān)注

關(guān)注

459文章

51824瀏覽量

432139 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7594瀏覽量

165664

原文標(biāo)題:學(xué)點(diǎn)不一樣的技術(shù):FPGA可重構(gòu)技術(shù)——FPGA芯片

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預(yù)測......

fpga和cpu的區(qū)別 芯片是gpu還是CPU

大多數(shù)FPGA的程序存儲(chǔ)器(FLASH)為什么都放在外面呢?FPGA的主要應(yīng)用

FPGA驅(qū)動(dòng)AD芯片之實(shí)現(xiàn)與芯片通信

FPGA與ASIC的區(qū)別 FPGA性能優(yōu)化技巧

FPGA基礎(chǔ)知識(shí)及設(shè)計(jì)和執(zhí)行FPGA應(yīng)用所需的工具

固化FPGA配置芯片的方式

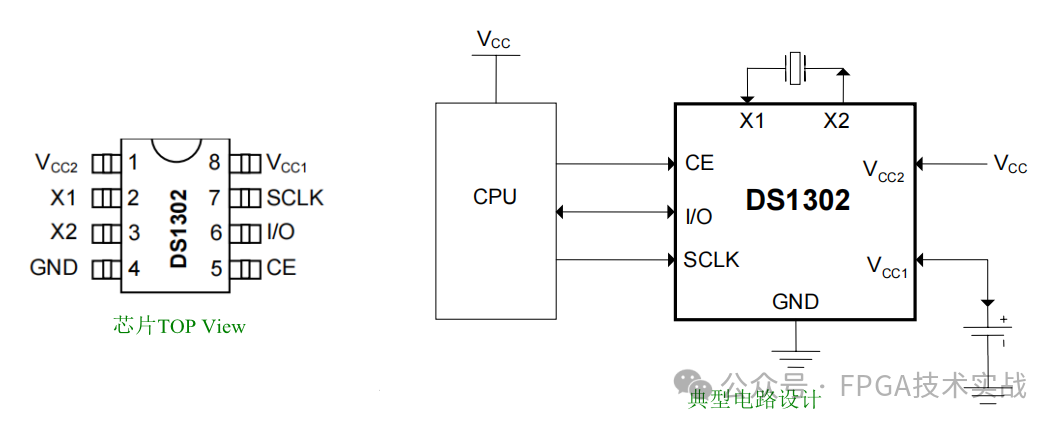

DS1302芯片與FPGA之間SPI通信原理

FPGA技術(shù)的主要應(yīng)用

如何快速入門FPGA

如何快速入門FPGA?

Xilinx FPGA的約束設(shè)置基礎(chǔ)

評(píng)論