本文描述了有限狀態機的基礎知識,并展示了在 Verilog 硬件描述語言中實現它們的實用方法。

有限狀態機,簡稱 FSM,是硬件和軟件系統中最普遍的操作模型之一。幾乎每個有用的數字系統都可以定義為有限狀態機,因此最好盡可能多地了解這種有用的系統模式。

數字電路中的有限狀態機

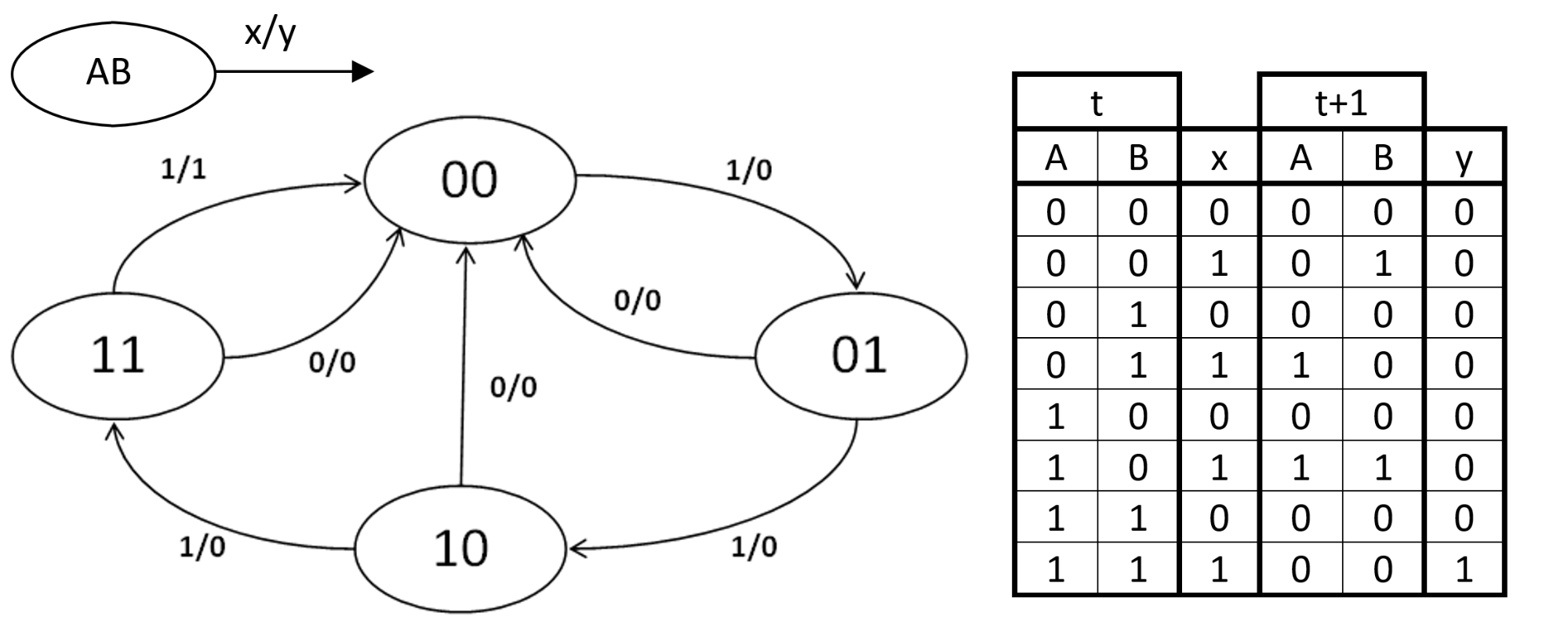

有限狀態機有多種描述方式,但最流行的兩種是狀態圖和狀態表。兩種表示的示例如圖 1 所示。

圖 1.顯示為狀態圖和狀態表的 FSM。左上角的圖例顯示了狀態變量 A 和 B,以及輸入 x 和輸出 y。

請注意,這個 FSM 有一個輸入信號 x 和一個輸出信號 y,這使它成為一個Mealy 狀態機。此 FSM 可以通過數字設計課程中教授的傳統方法來實現,該方法圍繞為實現狀態變量的觸發器生成激勵邏輯。該邏輯是根據所選觸發器類型的激勵表設計的,即 SR、D、JK 或 T。

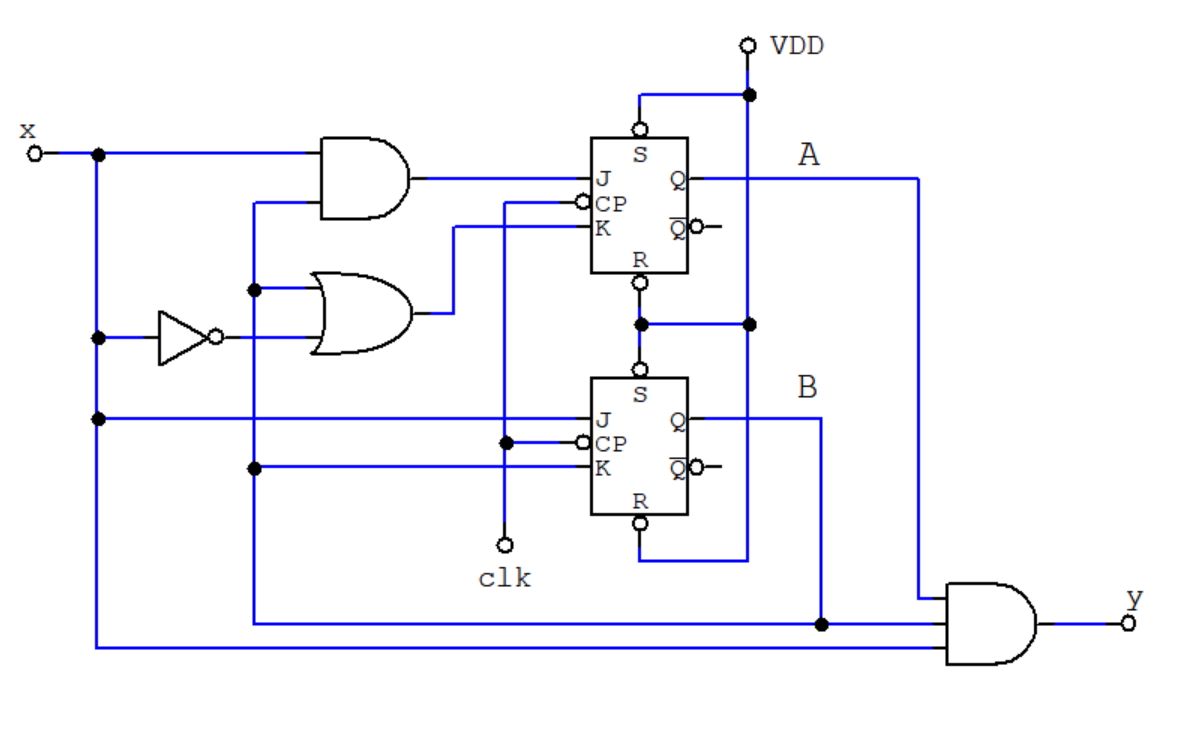

當我們將此技術應用于圖 1 中的 FSM 時,我們會得到以下實現的某個版本。

圖 2.使用 JK 觸發器的示例 FSM 的實現。

有關狀態機的更多信息,您可能需要閱讀 David Williams的文章在 VHDL 中實現有限狀態機。

Verilog 如何提供幫助

那么,如果您想在 Verilog 中實現如圖 1 所示的狀態機,該怎么做呢?Verilog 應該在設計過程的哪個階段接管?

雖然可以 手動設計整個系統,一直到圖 2 中的示意圖,然后用 Verilog 編寫代碼,但這并不是解決問題的最流行的方法。更糟糕的方法是描述原理圖中的每個門,包括構成觸發器的門!如果您在門級別描述所有內容,您的系統可能會 以某種方式工作,但這沒有給編譯器留下空間來優化您的設計以滿足您的實際 需求,這可能更關注時序和功率,而不僅僅是正確性。

請記住:使用硬件描述語言的原因是為了利用您將使用的綜合編譯器,并且像任何編譯器一樣,您給予它的自由度越大,您就越有可能產生最佳實現。

所以一個聰明的起點是狀態表。您只需指示 Verilog 機器在每個狀態下應該做什么,而不是使用哪個門或觸發器。

在 Verilog 中,狀態機的一個出色構造是Case 語句。每個案例的主體都應該檢查狀態變量及其期望的行為。下面的一段代碼展示了這個結構。

case (state)

STATE_0: // Code for State 0

STATE_1: // Code for State 1

// ...

STATE_N: // Code for State N

endcase

因此,通過我們的示例,這是圖 1 所示狀態機的實現。請注意,輸出 y 是一個組合函數。

module MyFSM(

input clk,

input x,

output y);

reg [1:0] state;

assign y = state[1] & state[0] & x;

always @ (negedge clk)

case (state)

2'b00: state <= x?2'b01:2'b00;

2'b01: state <= x?2'b10:2'b00;

2'b10: state <= x?2'b11:2'b00;

2'b11: state <= 2'b00;

endcase

endmodule

-

Verilog

+關注

關注

28文章

1351瀏覽量

110100 -

狀態機

+關注

關注

2文章

492瀏覽量

27541

發布評論請先 登錄

相關推薦

有限狀態機的建模與優化設計

VHDL有限狀態機設計-ST

初學者對有限狀態機(FSM)的設計的認識

如何使用FPGA實現序列檢測有限狀態機

基于事件驅動的有限狀態機介紹

基于事件驅動的有限狀態機介紹

一個基于事件驅動的有限狀態機

如何在Verilog中創建有限狀態機

如何在Verilog中創建有限狀態機

評論