逐次逼近寄存器模數轉換器 (SAR-ADC) 通常是中等分辨率應用的首選架構。市場上的 SAR 產品可以在高達幾兆赫茲的最大采樣率下運行。然而,設計人員將其應用需求與速度慢得多的 SAR-ADC 相匹配,以努力降低成本和布局問題。在市場上,SAR-ADC 的分辨率范圍從 8 位到 18 位。

這種類型的設備外形小巧,功耗低,這對于電池供電的應用至關重要。在本文中,我們研究了 SAR-ADC 的內部工作原理和轉換器的驅動器要求。

SAR-ADC 的工作原理

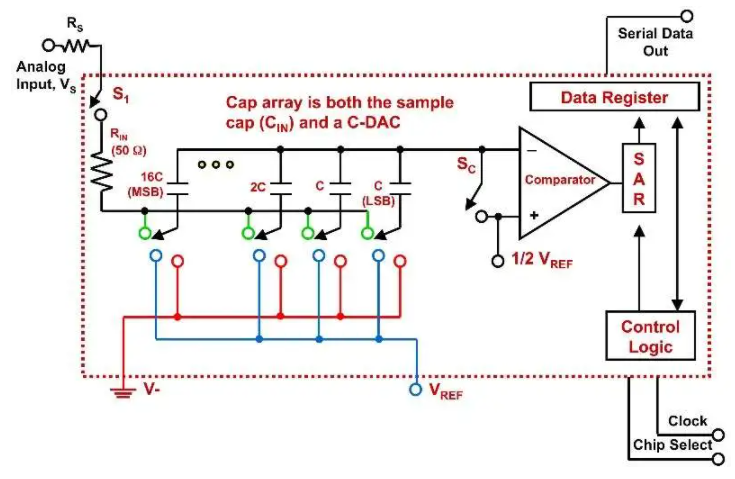

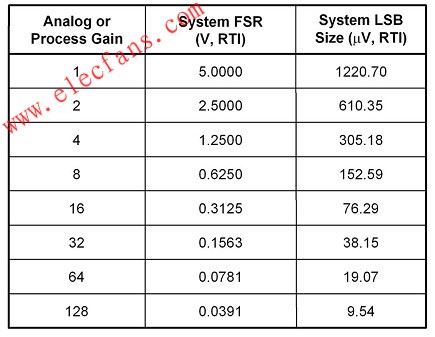

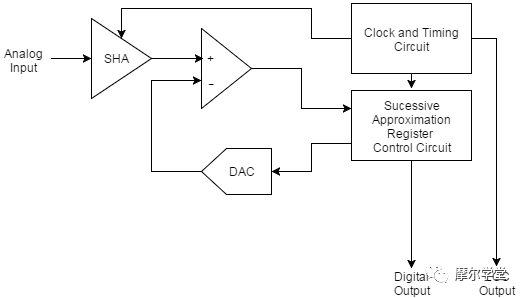

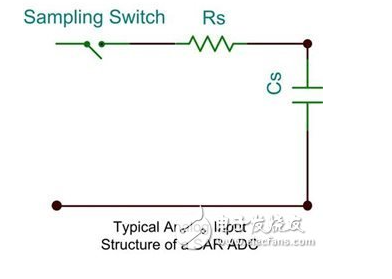

SAR-ADC(圖 1)捕獲模擬電壓信號,將該信號轉換為數字字。模擬信號由外部采樣/保持設備或 SAR-ADC 的內部采樣/保持功能捕獲。SAR-ADC 將此輸入電壓與轉換器外部或內部參考電壓 (VREF) 的已知部分進行比較。該基準設置轉換器的滿量程輸入電壓范圍。現代 SAR-ADC 使用電容式數模轉換器 (C-DAC) 來連續比較位組合并將適當的位設置或清除到數據寄存器中。

圖 1. 這是現代 SAR-ADC 16 位轉換器的內部采樣機制模型。在 VS 處獲取信號后,片選從高電平變為低電平并打開輸入開關 (S1)。

在 SAR 轉換器的輸入端,輸入信號首先經過一個開關。請注意,閉合開關會產生與電容陣列串聯的開關電阻 (RIN)。這些電容器的頂部連接到比較器的反相輸入。底部可以連接到輸入電壓、電壓參考 (VREF) 或接地 (V–)。最初,底部連接到輸入信號 VS。一旦電容陣列完全獲取輸入信號,輸入開關 (S1) 打開,轉換器開始轉換過程。

在轉換過程中,MSB 電容器的底部連接到 VREF,而其他電容器連接到 V–(或系統接地)。這個動作在所有電容器之間重新分配電荷。比較器的反相輸入根據電荷平衡上下移動電壓。如果 SC 上的電壓大于 VREF 的一半,則轉換器將“0”分配給 MSB,并將該值從串行端口發送出去。如果該電壓小于 VREF 的一半,轉換器從串行端口發送一個“1”,轉換器將 MSB 電容器連接到 V–。在 MSB 分配之后,此過程對 MSB-1 電容器重復。請注意,圖 1 未顯示 MSB-1 電容器,但其值為 8C。

發生 SAR-ADC 轉換過程所需的時間包括采集時間和轉換時間。在整個轉換過程結束時,SAR-ADC 進入睡眠模式。

驅動您的 SAR-ADC

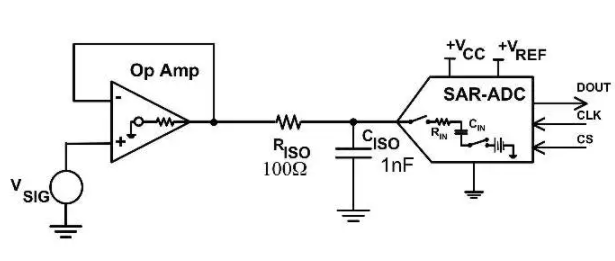

圖 2中優化的 ADC 驅動器電路 使用運算放大器 (op amp) 將 SAR-ADC 與高阻抗輸入源 VSIG 分離。以下 R/C 低通電路(RISO 和 CISO)執行返回運算放大器并轉發到 SAR-ADC 的功能。RISO 通過將放大器的輸出級與 CISO 隔離來保持放大器的穩定。CISO 為 SAR-ADC 提供了一個近乎完美且穩定的輸入源。該 CISO 跟蹤電壓的輸入信號,并在轉換器的采集時間內提供適當的 SAR-ADC 電荷。

圖 2. SAR-ADC 應用設計需要一個驅動電路(運算放大器、RISO 和 CISO),以確保 ADC 在轉換器的采集期間具有穩定的輸入信號。

在設計 SAR-ADC 電路時,首先要確定輸入信號的帶寬和滿量程范圍。然后,您選擇的 SAR-ADC 應該與每個 nyquist 的輸入信號帶寬相匹配。該轉換器還應具有適合您系統的分辨率。在本設計中,關鍵的 SAR-ADC 規格是電容陣列的累積值 CIN(相當于 SAR-ADC 的輸入電容)、轉換器的滿量程輸入范圍和采集時間 (tAQU)。

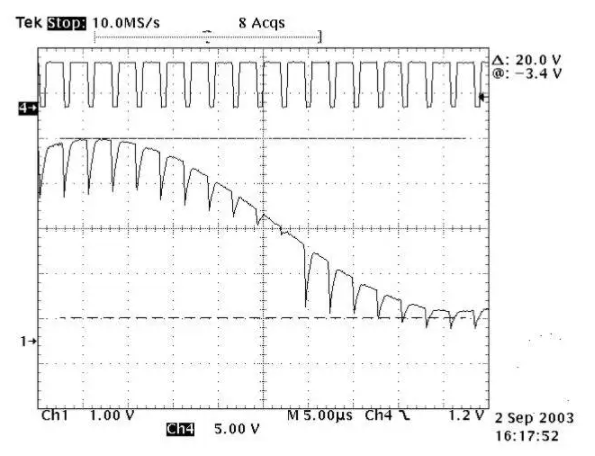

現在我們繼續通過確定它們的值來定義 RISO 和 CISO。圖 3 的示波器捕獲顯示了 SAR-ADC (ADS8326) 的輸入電荷注入瞬態。在此測量中,放大器緩沖器和 SAR-ADC (Ch1) 之間有一個 10 kOhm 電阻。開始轉換或片選信號出現在頂部曲線 (Ch4) 上。請注意,提供給 SAR 轉換器的輸入阻抗絕不應該高達 10 kOhm?但這讓我們可以看到這個 SAR-ADC 輸入端的高頻電流尖峰。

圖 3. 10 kOhm 電阻器捕獲 16 位 SAR-ADC (Ch1) 輸入處的電荷注入幅度。CS 引腳啟動每次發生的雜散,雜散發生在 ADC 的采集周期 (Ch4)。

SAR-ADC 輸入處的電荷注入發生在轉換器獲取輸入信號時。這些高頻尖峰對驅動運算放大器提出了非常苛刻的負載。

如圖1 所示,SAR 轉換器很少有內置輸入緩沖放大器。該電路需要一個具有無失真、軌到軌輸入級的運算放大器(請參見 OPA364 數據表,第 8 頁)。該放大器的輸出級跨度為正電源以下 100 mV 至 100 mV。

RISO 和 CISO(圖 2)的功能是為這種電荷注入提供一個到地的路徑,并將運算放大器的輸出與這些瞬態隔離。RISO 和 CISO 有效地完成了將放大器與容性負載隔離并從 SAR-ADC 吸收電荷尖峰的任務。然而,這兩個組件也會改變放大器的開環增益響應,如波特圖所示。

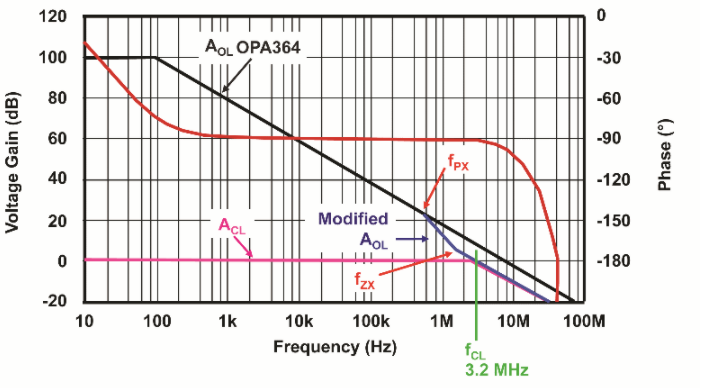

圖 4 顯示了一個示例運算放大器,該系統的波特圖。查看左側 y 軸如何繪制放大器的開環和閉環增益。右側 y 軸繪制放大器的開環相位響應。x 軸繪制頻率。

圖 4. 帶有 RISO|CISO 負載的 OPA364 開環增益/相位與頻率的關系。

該放大器 (OPA364) 的開環增益曲線在 10 Hz 時具有 100 dB 的增益。隨著頻率的增加,該增益曲線(~100 Hz)變為 –20 dB/decade 的斜率。該斜率一直持續到曲線持續超過 0 dB。開環增益曲線與 0 dB 的交點處的頻率為 7 MHz。

當外部電路 (RISO|CISO) 加載放大器時,會修改開環增益曲線。在圖 4 中,藍色曲線代表修改后的開環曲線。RISO 和 CISO 以及放大器的輸出電阻在 fPX 處產生一個極點,在 fZX 處產生一個零點。如圖 4所示,RISO 和 CISO 的極點出現在 769 kHz,而零點出現在 1.6 MHz。這條修改后的開環增益曲線的斜率從 –20 dB/decade 變為 –40 dB/decade 斜率,fPX 變為 –20 dB/decade 斜率,fPZ 在 1.6 MHz 為零。

電路穩定性定義在開環增益曲線和閉環增益曲線的交點 (3.2 MHz)。在這個交點處,如果這兩條曲線的斜率之差為 20 dB/decade,則放大器將是穩定的。如果這些斜率之間的差異大于 20 dB/decade(例如,40 dB/decade),則放大器電路將略微穩定。

為了盡量減少內部采樣電容的非線性效應,以及盡量減少電荷注入對輸入電壓的影響,最小 CISO 值是內部 SAR-ADC 采樣電容大小的 20 倍。通過注意這個 R|C 電路必須在轉換器的采集時間內完全穩定,可以找到 RISO 值。

結論

這是對 SAR-ADC 輸入結構和模擬驅動級設計策略的快速概述。SAR-ADC 的輸入結構在轉換器的采集時間內等于采樣電容陣列。為了確保輸入信號在采集期間保持穩定,一種有效的設計策略是在放大器的輸出和轉換器的輸入之間放置一個 R|C 對。

參考

1.“外部組件提高 SAR-ADC 精度”,Baker,Oljaca,EDN,2007 年 6 月 7 日。

2.“在驅動 SAR ADC 時從正確的運算放大器開始,”Oljaca,Baker,EDN,2008 年 10 月 16 日

。3 。 下載這些數據表:OPA364、ADS8361。

關于作者

Bonnie Baker是德州儀器 (TI) Webench 團隊的高級應用工程師,從事模擬和數字設計及系統工作超過 25 年。她撰寫了數百篇文章、設計和應用說明、會議論文,并撰寫了一本書:“A Baker‘s Dozen: Real Analog Solutions for Digital Designers”。

-

運算放大器

+關注

關注

215文章

4960瀏覽量

173253 -

模數轉換器

+關注

關注

26文章

3215瀏覽量

126906

發布評論請先 登錄

相關推薦

為什么使用24位轉換器來替代多個12位器件

基于SAR-ADC架構的此類系統的實現需求

根據系統和技術選擇轉換器

解析SAR-ADC 的內部工作原理和轉換器的驅動器要求

解析SAR-ADC 的內部工作原理和轉換器的驅動器要求

評論