前幾天和同事聊天,他說他上初中的兒子做出了一道很難的數學題,想考考我們這些大學生看能不能做得出來?

題目很簡單:

大家先嘗試做一下?我沒想出怎么算的,只是用排除法確定了a和b的范圍,然后再逐個嘗試。

1.對4361進行開方計算,得到結果最大為66,則a,b的值均小于等于66。

2.對4361/2進行開方計算,則得到結果為46,則a,b兩者,一個是1-46,一個是46-66之間的數。

3.由平方和4361末尾為1,再根據整數平方和的幾種可能,計算出僅有0+1和5+6這兩種可能,而且平方之后的個位數為0/1/5/6,這樣就進一步縮小了范圍,通過多次計算嘗試可以得出結果。

不過我懶得算了,就簡單寫了個C語言程序,計算出了結果:

#include其實可以設置一個數的循環范圍是:1-46,一個數的循環范圍是46-66,這樣會減少循環次數。

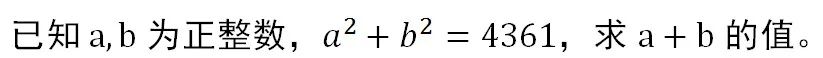

運行結果:

運行結果

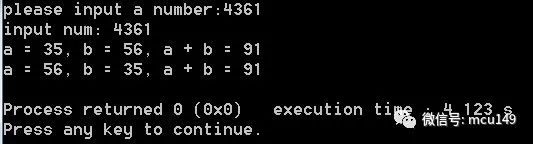

運行結果而且這種方式還適用于解的個數不唯一的情況,比如7605:

運行結果

運行結果作為一個野生FPGA開發者,我在想能不能用FPGA的編程思想來實現呢?也就是如何用Verilog來實現兩個循環的嵌套呢?抄起鍵盤就是干!

verilog源文件fpga_math.v:

modulefpga_math(

//inputs

inputclk,

inputrst_n,

//outputs

outputreg[13:0]a,b,

outputreg[14:0]result,

outputok

);

parameterSUM=4361;

parameterSQR=67;//sqrt(SUM);

reg[13:0]tmp_a;

reg[13:0]tmp_b;

regflag;

assignok=(tmp_a*tmp_a+tmp_b*tmp_b==SUM);

always@(posedgeclk)

begin

if(!rst_n)

tmp_b<=0;

elseif(tmp_b==SQR)

tmp_b<=?0;

elseif(tmp_a!=SQR)

tmp_b<=?tmp_b?+?1;

end

always@(posedgeclk)

begin

if(!rst_n)

flag<=0;

elseif(tmp_b==SQR)

flag<=?1;

else

flag<=?0;

end

always@(posedgeclk)

begin

if(!rst_n)

tmp_a<=0;

elseif((tmp_a!=SQR)&flag)

tmp_a<=?tmp_a?+?1;

end

always@(posedgeclk)

begin

if(!rst_n)

begin

a<=0;

b<=?0;

result<=?0;

end

elseif(ok)

begin

a<=tmp_a;

b<=?tmp_b;

????????result?=?tmp_a?+?tmp_b;

????end

end

endmodule

為了驗證這個模塊的正確性,我們需要對這個模塊進行仿真,即給一個激勵輸入信號,看輸出是否正確。

新建testbench文件fpga_math_tb.v:

`timescale1ns/100ps

modulefpga_math_tb;

parameterSUM=4361;

parameterSQR=67;//sqrt(4361)

parameterSYSCLK_PERIOD=10;//100MHZ

wire[13:0]a,b;

wire[14:0]result;

regSYSCLK;

regNSYSRESET;

initial

begin

SYSCLK=1'b0;

NSYSRESET=1'b0;

#(SYSCLK_PERIOD*10)

NSYSRESET=1'b1;

#(SYSCLK_PERIOD*(SQR*SQR+500))

$stop;

end

/*generateclock*/

always@(SYSCLK)

#(SYSCLK_PERIOD/2.0)SYSCLK<=?!SYSCLK;???????

/*instancemodule*/

fpga_math#(

.SUM(SUM),

.SQR(SQR)

)fpga_math_0(

//inputs

.clk(SYSCLK),

.rst_n(NSYSRESET),

//outputs

.a(a),

.b(b),

.result(result),

.ok(ok)

);

endmodule

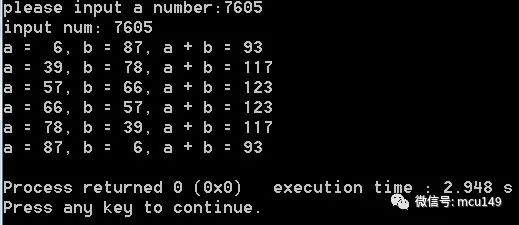

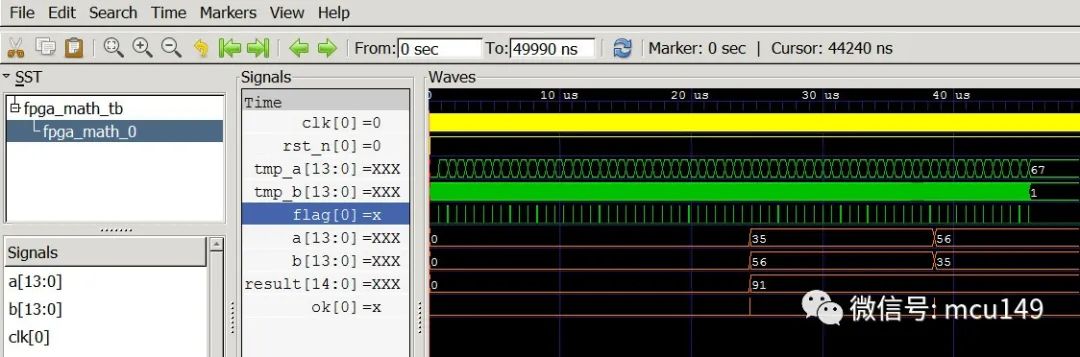

ModelSim仿真波形:

仿真波形

仿真波形仿真工具除了使用各大FPGA廠商IDE帶的ModelSim等,也可以使用小巧開源的全平臺仿真工具:iverilog+gtkwave,使用方法可以參考:

全平臺輕量開源verilog仿真工具iverilog+GTKWave使用教程

如果使用iverilog進行仿真,需要在TB文件中添加以下幾行語句:

/*iverilog*/

initial

begin

$dumpfile("wave.vcd");//生成的vcd文件名稱

$dumpvars(0,fpga_math_tb);//tb模塊名稱

end

/*iverilog*

首先,對Verilog源文件進行編譯,檢查是否有語法錯誤,這會在當前目錄生成wave目標文件:

iverilog-owave*.v

然后通過vvp指令,產生仿真的wave.vcd波形文件:

vvp-nwave-lxt2

使用gtkwave打開波形文件:

gtkwavewave.vcd

當然,以上命令也可以寫成批處理文件:

echo"開始編譯"

iverilog-owave*.v

echo"編譯完成"

echo"生成波形文件"

vvp-nwave-lxt2

echo"打開波形文件"

gtkwavewave.vcd

以文本方式存儲為build.bat文件即可,雙擊即可自動完成編譯、生成波形文件、打開波形文件操作。

仿真波形:

仿真波形

仿真波形可以看出,和使用ModelSim仿真是一樣的結果。

總結

從仿真波形圖中,可以得到計算的結果,a+b的值為91,如果要在真實的FPGA芯片硬件上實現,還需要添加其他功能模塊,把結果通過串口輸出,或者在數碼管等顯示屏上進行顯示,這里只是簡單介紹使用FPGA計算方法的實現。

作為純數字電路的FPGA,實現平方根是比較復雜的,這里采用直接人為輸入平方根結果的方式,而不是像C語言那樣調用sqrt函數自動計算平方根。

FPGA中不僅有觸發器和查找表,而且還有乘法器、除法器等硬核IP,所以在涉及到乘除法、平方根運算時,不要直接使用*/等運算符,而是要使用FPGA自帶的IP核,這樣就不會占用大量的邏輯資源,像Xilinx的基于Cordic算法的Cordic IP核,不僅能實現平方根計算,而且還有sin/cos/tan/arctan等三角函數。

END 審核編輯 :李倩-

FPGA

+關注

關注

1631文章

21808瀏覽量

606808 -

C語言

+關注

關注

180文章

7616瀏覽量

138078 -

編程

+關注

關注

88文章

3643瀏覽量

94132

原文標題:如何用FPGA解一道初中數學題?

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

采用fpga控制ADS8555進行采樣,對某一通道輸入正弦信號時,采樣的結果卻是方波,為什么?

ADS1256 8通道依次采樣,數據不正確怎么解決?

Kimi發布新一代數學推理模型k0-math

熱解粒子探測器干嘛用的

Verilog testbench問題求助

DS90CR486 133MHz 48位通道鏈路解串器數據表

DS92LV3241/3242 32位通道Link II串行器/解串器數據表

評論