【 一 】

數字IC系統邏輯設計這部分主要介紹兩個方面,一個是RTL的設計基礎;另一方面是verilog基本語法。這一篇文章主要介紹一下RTL的設計基礎。

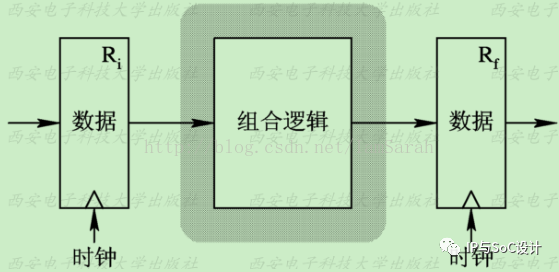

RTL設計都是采用同步電路設計方式,了解同步電路的設計要求是RTL設計的第一步。下圖是一個同步電路的示例:

其中,組合邏輯實現設計所需要的功能,寄存器用于暫存數據用時鐘控制。只有當時鐘進行有效跳變時,才將新的數據所存起來,否則數據保持原值。時鐘相當于同步電路中的指揮。時鐘一般是由晶振產生,或者由外部輸入,如果需要還需要用鎖相環進行倍頻、相移等操作。

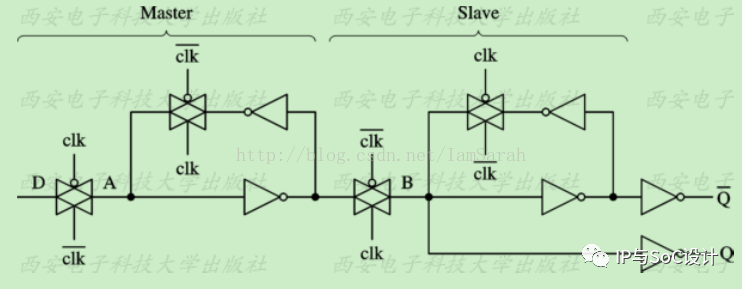

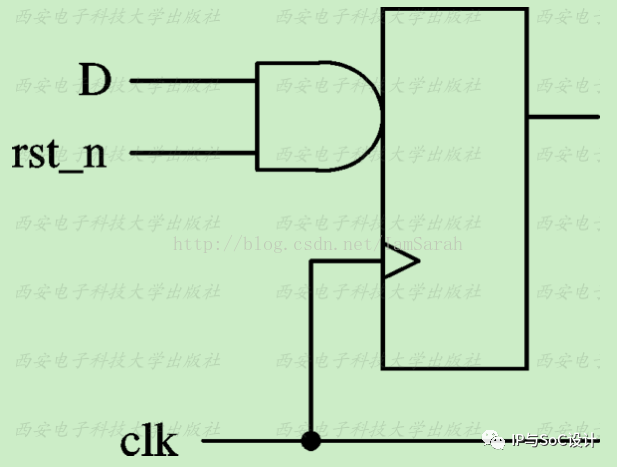

下面對寄存器做一個介紹,一個寄存器的結構如下圖所示:

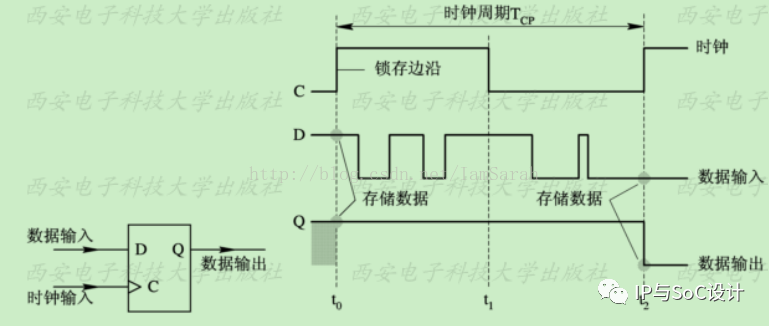

寄存器的功能如下圖所示:

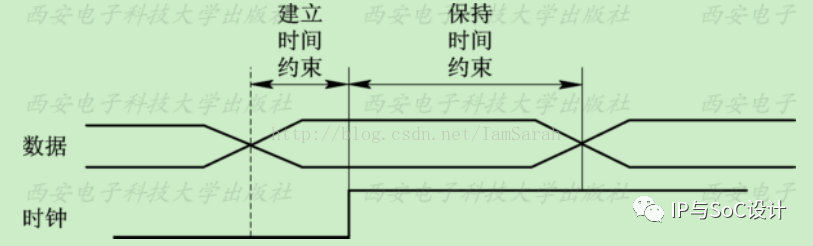

由圖可得,該寄存器在時鐘的跳變沿鎖存數據,然后數據會保持直到下一個跳變沿。寄存器要正常工作,必須保證D端的數據變化與時鐘的有效沿不能距離太近,否則有可能鎖存錯誤的數據。在綜合庫中,規定了數據變化端跟時鐘跳變沿最短的時間要求,即建立時間約束和保持時間約束。建立時間規定,在時鐘沿到達前的某段時間內,數據必須穩定;保持時間定義了在時鐘沿之后的某段時間之后,數據才能發生變化。

對于一個寄存器來說,除了數據端與時鐘端有時序要求。異步復位端與時鐘端也有要求。假設一個寄存器是已不復位的,復位信號低電平有效。當復位信號是低電平時,寄存器被初始化。當異步復位信號跳高時,寄存器在時鐘跳變沿鎖存新的數據。如果異步復位信號跳高的時刻距離時鐘有效沿太近,寄存器可能繼續保持復位狀太,也可能鎖存新的數據。因此有必要定義時鐘有效沿與異步復位無效沿之間的時序要求,這就是recovery/removal的時序要求,如圖所示;

寄存器中建立時間/保持時間、recovery/removal的時序要求, 對設計的最大組合邏輯延時、時鐘樹的構造、復位樹的構造都提出了要求。復位樹、時鐘樹一般由后端工具進行處理。對RTL設計者來說,最需關注的是建立時間的問題。設計中的時序違例通過靜態時序分析工具可以檢查出來。

在IC系統中, 復位的目的是為了將芯片強制到一個已知的狀態。同步復位與異步復位都能達到這個目的。兩者的差別在于:同步復位需要時鐘有效沿到達時才能起作用,而異步復位不需要。如下,是同步復位電路:

同步復位的優點在于:

1)在采用基于周期的仿真器場合,同步復位簡單

2)寄存器可以濾掉復位上的毛刺

缺點:

1)需要時鐘,在某些場合帶來不便。假如設計中包含三態總線,總線上接著許多寄存器。當上電后,晶振還未起振,鎖相環還未穩定,這時候沒有時鐘,所以復位還沒有起作用,因此會導致總線上發生沖突。只有增加上電復位電路才能解決此問題。

2)采用同步復位,復位成為路徑組合邏輯的一部分,由于復位的負載比較大,因此會使得復位樹的延遲比較大,從而導致在路徑上的延遲比較大。

異步復位的優點是不需要時鐘,且復位不會影響到路徑延時。缺點是:復位上的毛刺不能被由它復位的寄存器過濾掉;復位的無效沿與時鐘之間存在時序要求。

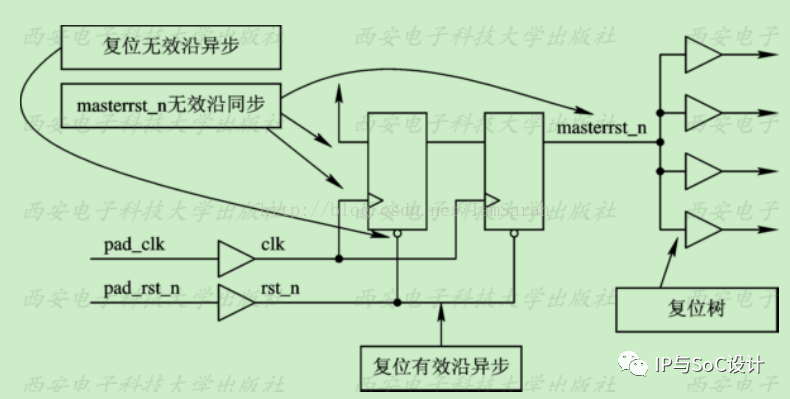

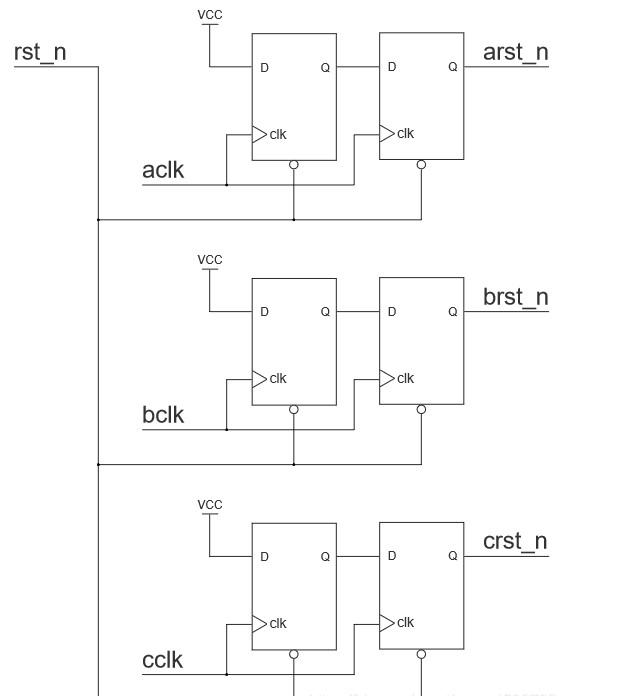

將同步復位和異步復位優點結合起來:給出了一種異步復位,同步釋放的復位方法,如下圖所示:

該電路的原理是:當復位信號有效時,兩個同步器都為低,因此同步器的輸出立即變低,而不管此時是否存在時鐘。當復位信號變高后,經過時鐘跳變沿后才能將高電平鎖存到同步器的輸出,也就是說,同步器的輸出的無效沿是與時鐘同步的。

【 二 】

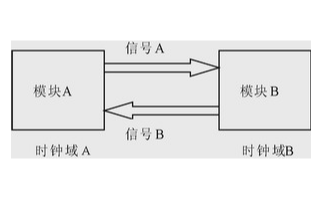

這篇文章主要講一下RTL設計中多時鐘域的處理,之前在異步FIFO設計中已經講到這個問題,這篇更全面詳細的介紹一下多時鐘域的處理。

多時鐘域之所以難以處理,是因為在兩個時鐘域之間傳遞信號時,不可避免地會出現建立時間/保持時間違例的問題。寄存器會鎖存錯誤的數據,引起功能錯誤。

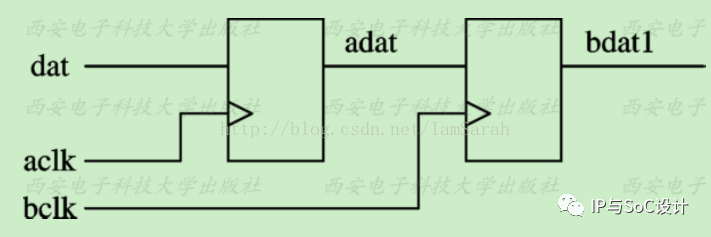

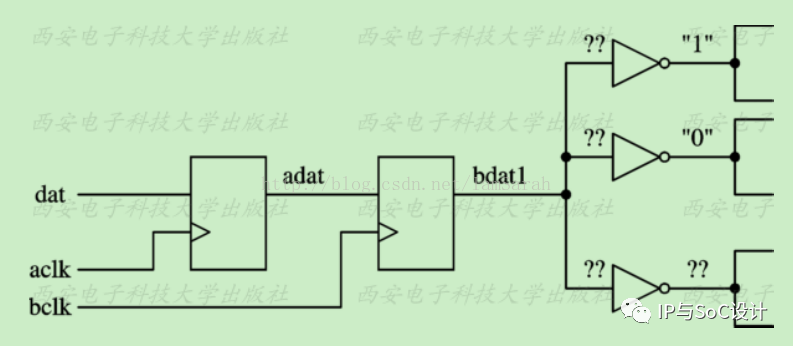

現考慮在兩個時鐘域間傳遞1位信號的情況。如下圖是多時鐘域傳遞一位信號的示例:

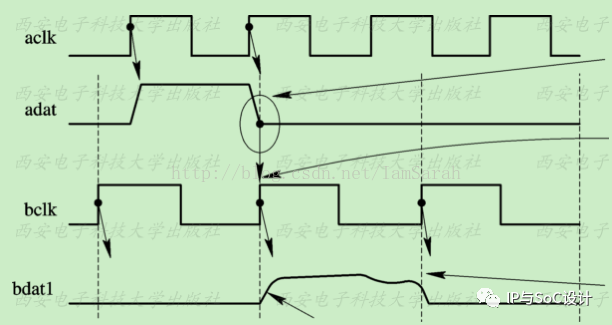

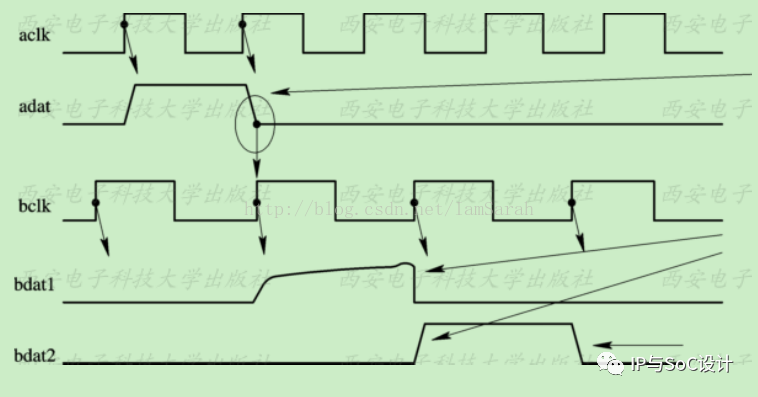

在這個例子中,aclk與bclk是兩個異步時鐘。由aclk時鐘域產生的數據adat要送到bclk的時鐘域。由于bclk與aclk不同步,所以會出現這種情形:在一定時刻,adat的變化沿距離bclk的采樣沿非常接近,不能滿足建立時間和保持時間的要求。這樣, 寄存器可能會進入亞穩態。下圖是這種情況下的波形圖:

bdat1的值會傳遞給其他模塊。在實際芯片中,在bdat1處于亞微態的時候,有些模塊會認為自己收到的是“1”, 有些會認為是“0”,這種不一致會導致功能錯誤,如下圖所示:

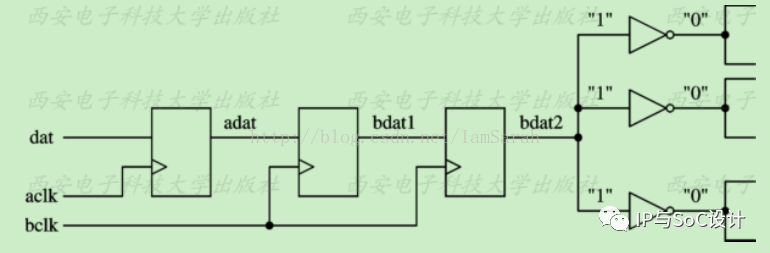

這種情形需要采用下圖所示的同步器來避免:

采用同步器之后,其波形如下圖所示:

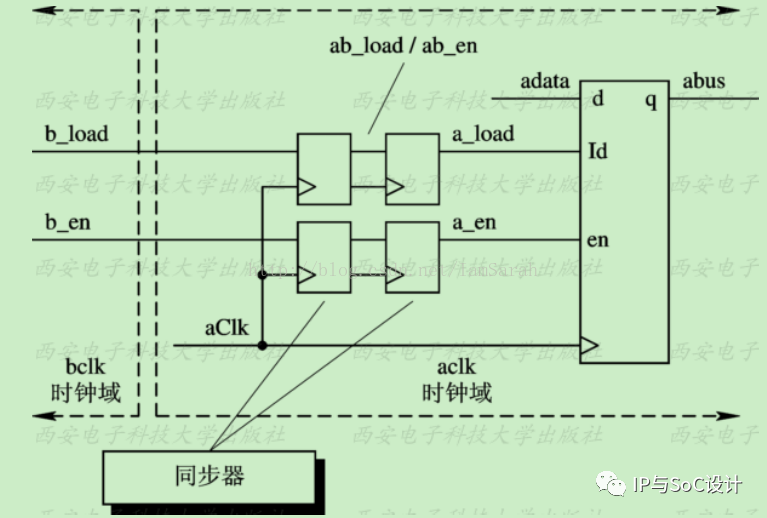

下面看一下相關的多位信號的傳遞,同步器適用于在多時鐘域間傳遞1位信號,但是對于相關的多位信號,采用這種技術仍然會出現問題。如下圖所示,在多時鐘域間傳遞兩位信號:

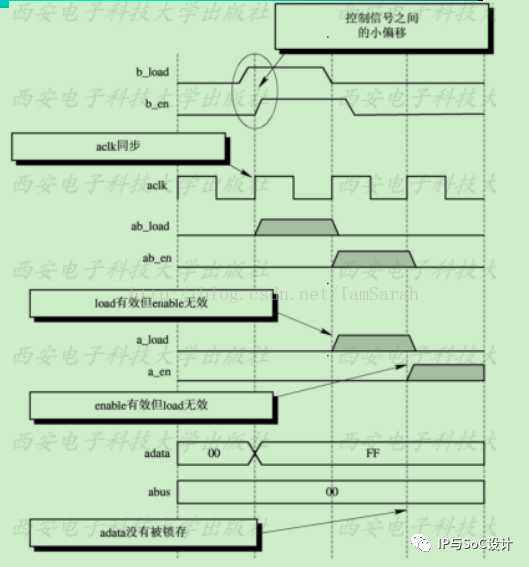

在這個例子中,有兩個信號b-load和b-en由bclk時鐘域傳遞到aclk時鐘域。這兩個信號相關。我們假設在某個時鐘周期內, b-load與b-en同時有效,那么這兩個信號分別經過同步器后,得到的波形如下所示:

由于b-load信號與b-en信號的延遲不同,兩者的上升沿之間有一些偏移。如果同步器的采樣時鐘正好也位于兩個信號變化沿之間, 則采樣后的信號有可能會相差一個周期。這種情況下,可以將兩個信號進行邏輯與操作變成一個信號送到同步器。但是很多時候,無法對傳遞信號進行簡單的合并。這個時候就可以考慮先將這些信號變成格雷碼,然后通過同步器來傳遞。由于格雷碼在一個周期內僅有一位發生變化,這樣經過同步器之后就可以得到正確的結果。

上述方案都是基于同步器的,依據的原理是降低寄存器處于亞穩態的概率。另外一種方案是用多組寄存器來存儲信號,過一段時間再進行讀操作。在開始讀操作的時候,數據早已經穩定下來,就不會出現建立時間/保持時間違例的情況。這也就是基于異步fifo在多時鐘減傳遞信號的基本原理。關于異步FIFO的設計,已經講過,在此不再贅述。

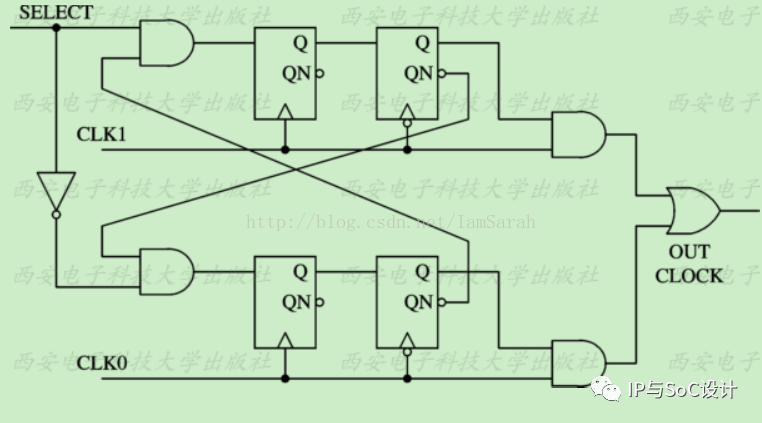

下面講一下時鐘切換電路,有些設計中需要進行時鐘切換。動態地將始終從高頻切換到低頻或者由低頻切換到高頻,切換過程中會出現毛刺。時鐘上的毛刺是非常致命的,可能會導致功能錯誤。要避免這種問題可以采取兩種方法,一種是在時鐘切換時,進入復位,當切換完成后,復位結束;另一種方法是采用時鐘切換電路,如下圖所示,這種切換電路跟鎖存器的設計有異曲同工之妙。

原文標題:帶你科普RTL設計基礎

文章出處:【微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5359瀏覽量

120790 -

RTL

+關注

關注

1文章

385瀏覽量

59874 -

多時鐘域

+關注

關注

0文章

6瀏覽量

6011

原文標題:帶你科普RTL設計基礎

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于FPGA中跨時鐘域的問題分析

解析多時鐘域和異步信號處理解決方案

詳解RTL設計中多時鐘域的處理方法

詳解RTL設計中多時鐘域的處理方法

評論