ASML開發(fā)的下一代EUV平臺,將數(shù)值孔徑從0.33增加到0.55,將能提供比當前的EUV平臺高70%的分辨率能力。

在最近的SPIE Advanced Lithography+Patterning Conference上,來自英特爾的Mark Phillips對0.55高數(shù)值孔徑極紫外光刻技術(shù)進行了有見地的分享。Mark甚至斷言High-NA EUV的開發(fā)進展將支持2025年的生產(chǎn)部署。本文總結(jié)了Mark演講的亮點,包括對0.55NA一代之后的預測。

具有13.5nm波長源的高數(shù)值孔徑系統(tǒng)將提高亞13nm半間距曝光所需的分辨率,以及更大的圖像對比度以實現(xiàn)更好的印刷線均勻性。High-NA EUV光刻的分辨率通常被稱為“13nm到8nm半間距”。

EUV技術(shù)歷史

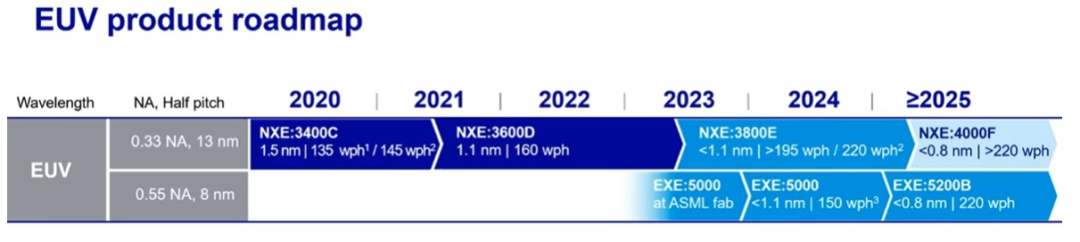

首先回顧以下0.33 NA EUV技術(shù)的歷史。2014-2017年第一代系統(tǒng)開發(fā)周期中實現(xiàn)目標源功率和可用性的困難。晶圓成本評估反映了增加的工具成本、掩模成本和0.33NA過渡對吞吐量的影響。

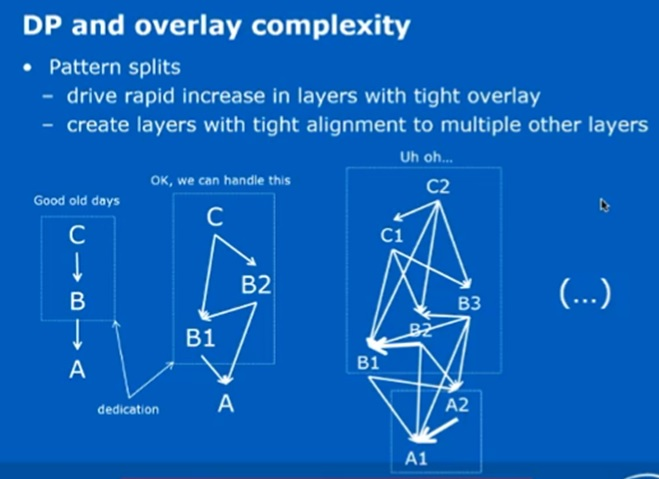

Mark指出:“93i的間距分割光刻(多圖案)運行良好。與EUV過渡相結(jié)合所需的光刻基礎設施尚未完全可用。轉(zhuǎn)向0.33NAEUV的令人信服的原因是間距劃分對邊緣放置誤差(EPE)的影響。帶有間距劃分的疊加對齊復雜性顯著增加。”下圖說明了Mark提到的掩模對齊依賴關系的示例,因為使用了越來越多的雙圖案掩模層。

Mark表示,從成本分析的角度來看,在解決用單個0.55NA掩模替換雙圖案0.33NA層時,與早期用單個0.55NA掩模替換193i掩模時的成本權(quán)衡相比,0.55NA EUV會比0.33NA EUV更方便掩膜。

EUV基礎設施

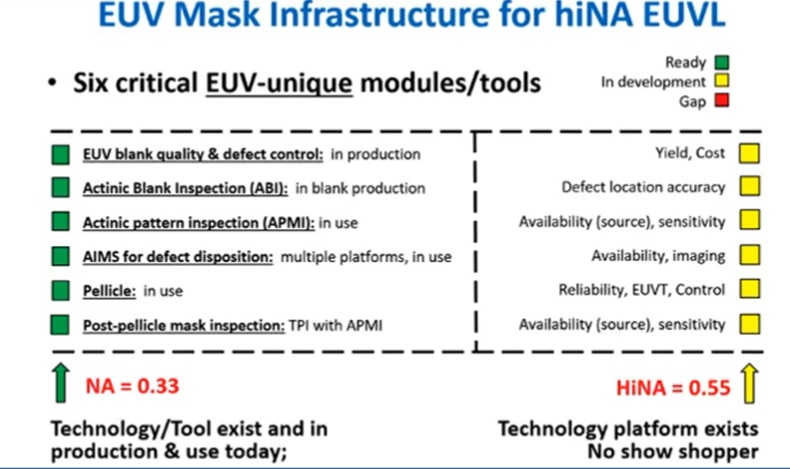

EUV光刻的討論往往集中在ASML光刻機上——然而,有一組豐富而復雜的相互依賴的技術(shù)需要伴隨曝光系統(tǒng)的任何變化:

劑量敏感性、粘度、涂層均勻性與厚度、可實現(xiàn)的分辨率以及對曝光時材料內(nèi)光子/離子/電子相互作用的理解

掩模空白質(zhì)量:平整度、缺陷、熱膨脹系數(shù)

圖案掩模質(zhì)量:掩模吸收層的缺陷、反射率/消光

掩模缺陷檢測技術(shù)——分辨率和吞吐量

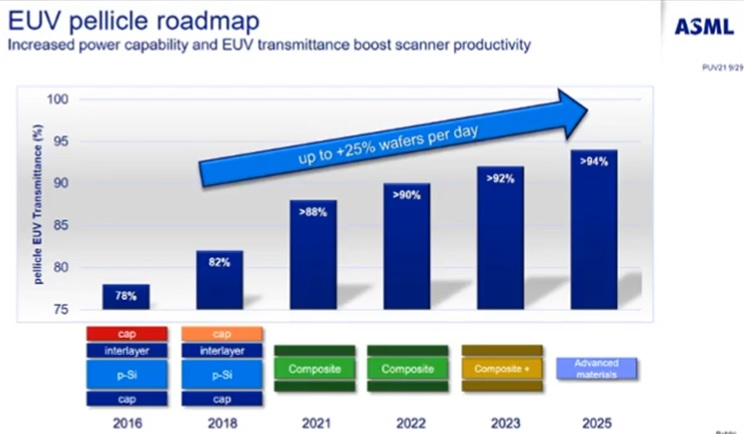

薄膜:透射率、均勻性、與暴露于高能照明的兼容性、薄膜貼附后缺陷檢測

Mark稱贊了光刻行業(yè)在所有這些領域取得的相應進展,并特別提到了檢測計量系統(tǒng)供應商。他說,“到2019年,所有0.33 NA EUV的基礎設施系統(tǒng)都是不錯的,盡管薄膜的傳輸、均勻性和功率彈性仍需要改進。”

ASML的下圖說明了防護膜透光率與晶圓產(chǎn)量之間的直接關系,目標是在2025年實現(xiàn)“先進的防護膜材料”,提供》94%的透光率。

0.55 High-NA轉(zhuǎn)換

Mark分享了即將到來的流程節(jié)點轉(zhuǎn)換的目標:

7nm節(jié)點:18nmHP

5nm節(jié)點:13nmHP

3nm節(jié)點:10nmHP

然后,他回顧了0.55NA基礎架構(gòu)的各個方面。

EUVEXE:5000系統(tǒng)

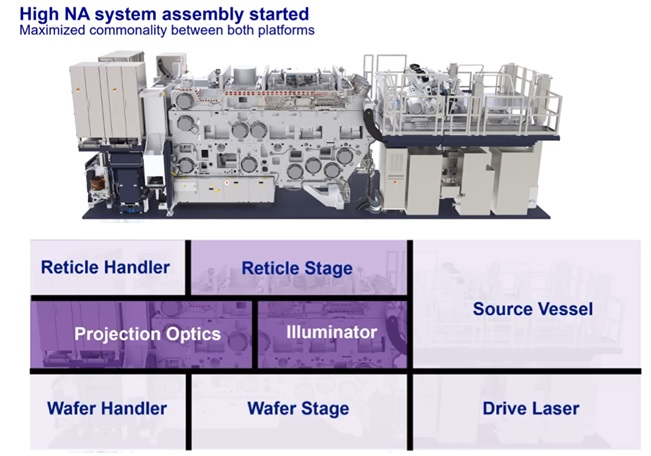

Mark表示,對下一代EUV光刻機可用性的信心很高。這些系統(tǒng)利用了第一代NX:3000系列中的許多現(xiàn)有子系統(tǒng)。

下圖顯示了高NA EUV系統(tǒng)的新子系統(tǒng)(紫色),以及從當前系列移植的子系統(tǒng)。

投影光學器件是一個關鍵的新模塊。蔡司和ASML之間的合作開發(fā)進展順利。至于必需的EUV光刻膠,Mark表示化學放大光刻膠(CAR)和金屬氧化物光刻膠仍處于積極開發(fā)階段。Mark說:“還有幾個優(yōu)化參數(shù)仍在評估中,包括光刻膠類型、粘度、厚度和達到目標分辨率的能量劑量、顯影光刻膠輪廓和線邊緣均勻性。”

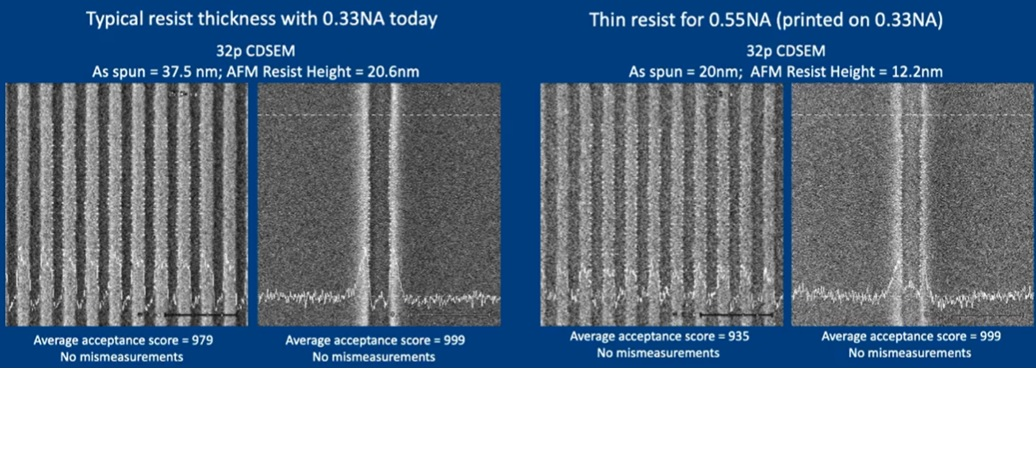

下圖顯示了0.55NA抗蝕劑實驗在20nm旋轉(zhuǎn)厚度下(使用0.33NA曝光)的SEM和原子力顯微鏡輪廓結(jié)果。

Mark指出,從0.33NA工藝步驟的約37.5nm抗蝕劑厚度到0.55NA更薄的層需要詳細注意抗蝕劑粘度和旋轉(zhuǎn)工藝步驟。(較薄的抗蝕劑在抗蝕劑高度與寬度方面保持2:1的縱橫比。請注意,對于較高的NA光學系統(tǒng),曝光的景深會降低,這是選擇抗蝕劑厚度時的另一個考慮因素。另請注意,較薄的抗蝕劑抗蝕劑會導致SEM圖像對比度降低,因此需要不斷開發(fā)改進的高通量抗蝕劑計量。)

高數(shù)值孔徑EUV掩模

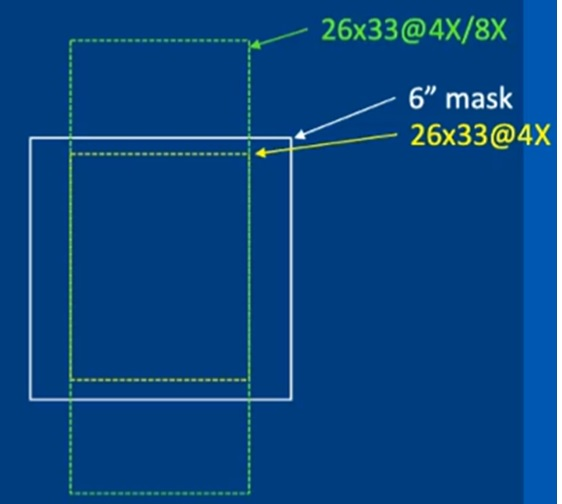

0.55NA系統(tǒng)采用了獨特的創(chuàng)新光路。光場數(shù)值孔徑的增加需要相應地改變掩模到晶片的曝光減少。投影光學系統(tǒng)利用各向異性縮小因子,即x維度縮小4倍,y維度縮小8倍。然而,如下圖所示,傳統(tǒng)的6英寸掩模尺寸不支持“全光罩”26mmX33mm視場——8X demagy范圍超過面罩高度。

因此,每個High-NA EUV層將有一個雙“半場”掩模曝光序列。

Mark表示0.55 NA EUV掩模基礎設施的其余部分將充分利用為0.33 NA開發(fā)的現(xiàn)有技術(shù)。Mark說:“與過渡到(環(huán)柵)RibbonFET器件相關的計量挑戰(zhàn)遠遠超過了與High-NA EUV掩模檢查和測量相關的挑戰(zhàn)。”

未來的0.7NA系統(tǒng)

在SPIE高級光刻會議上的另一次演講中,ASML和imec表示他們正在荷蘭Veldhoven建立一個High-NA EUV系統(tǒng)原型設施,將于2023年上線。該實驗室將允許進一步開發(fā)抗蝕劑和實驗室合作伙伴的方法流程。

Mark表示:“英特爾將繼續(xù)與ASML密切合作,與該實驗室的High-NA研究人員合作。我們預計2023年底或2024年初在俄勒岡州安裝試點工具系統(tǒng),并于2025年投入生產(chǎn)。”

Mark認為下一個目標可能是:

7NA

非整數(shù)掩模縮小光路(例如,y維度上為7.5X,x維度上為5X)

新的掩膜材料和尺寸的出現(xiàn)

Mark說:“我們需要一種熱膨脹率極低的材料(LTEM)來制造掩模坯。我們將需要更好的吸收器。而且,我們將需要一個新的‘標準’掩膜尺寸。”下圖顯示了如何應用300毫米圓形(775微米厚的基板)。

英特爾正與ASML合作,在2024年實現(xiàn)早期High-NA系統(tǒng)可用性,生產(chǎn)日期目標為2025年。由于重用掃描儀的0.33NA經(jīng)驗的顯著影響,這些日期的置信度相對較高子系統(tǒng)對掩模計量和檢測技術(shù)的重大成就。

Mark表示,盡管在選擇用于High-NA曝光的抗蝕劑和薄膜方面仍有重大進展,但新掃描儀中的光學系統(tǒng)是關鍵路徑。

采用0.55NA光刻技術(shù)將實現(xiàn)亞13nm半間距關鍵尺寸,與英特爾超越18A節(jié)點的工藝路線圖一致。

審核編輯 :李倩

-

EUV

+關注

關注

8文章

609瀏覽量

86681 -

ASML

+關注

關注

7文章

723瀏覽量

41820

原文標題:詳解ASML最新0.55 High-NA EUV平臺

文章出處:【微信號:ICViews,微信公眾號:半導體產(chǎn)業(yè)縱橫】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

百度李彥宏談訓練下一代大模型

使用下一代GaNFast和GeneSiC Power實現(xiàn)電氣化我們的世界

意法半導體下一代汽車微控制器的戰(zhàn)略部署

西門子EDA發(fā)布下一代電子系統(tǒng)設計平臺

通過電壓轉(zhuǎn)換啟用下一代ADAS域控制器應用說明

實現(xiàn)具有電平轉(zhuǎn)換功能的下一代無線信標

通過下一代引線式邏輯IC封裝實現(xiàn)小型加固型應用

ASMPT與美光攜手開發(fā)下一代HBM4鍵合設備

24芯M16插頭在下一代技術(shù)中的潛力

評論