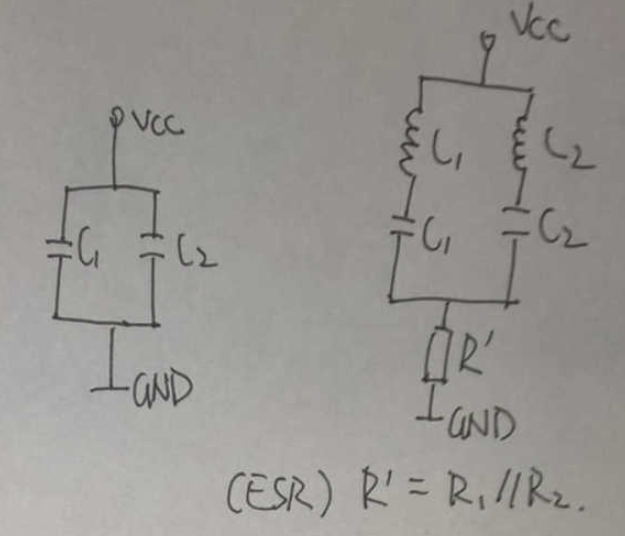

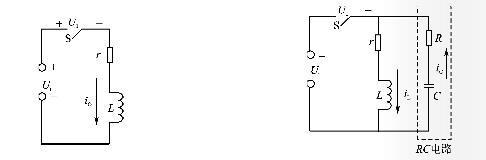

電路原理圖畫成一個極性電容和非極性電容并聯的形式,更加多地是為了在畫板的過程中在PCB的絲印層添加相關的引腳極性信息,避免接錯極性炸電容。

當然了,EE的老司機們,一般都能直接看出這是電源“去耦”電容的經典組合。理想的電源應該提供穩定的直流電壓,故去耦(decouple)的對象是電源網絡中的噪聲。在電源網絡上并電容到地是解決這個問題最簡單的辦法。

至于為什么是極性//非極性這種奇怪的形式,而不選擇極性//極性,亦或是直接選一個等值的電容,這里面就有點意思了。

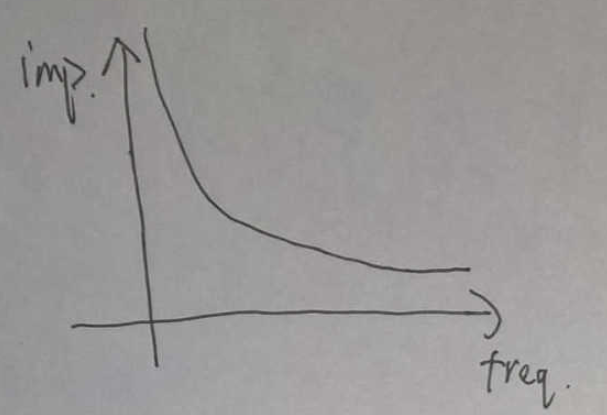

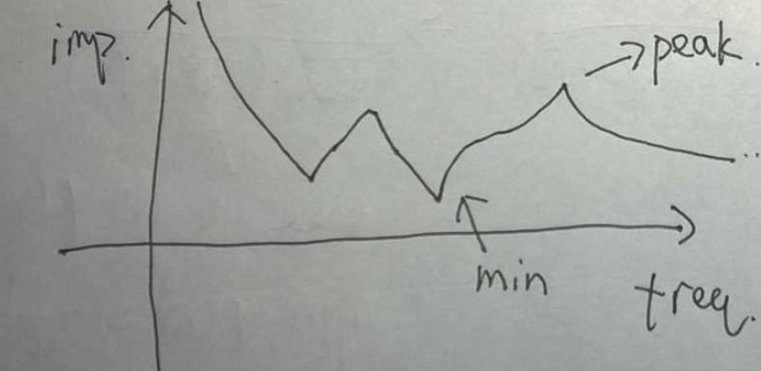

一般說來,實際電路上大容量的極性電容會是電解電容,而小容量的無極性電容會是瓷片電容之類的。對于一個理想的電容,阻頻曲線大概是這樣的

這個也是理想的電源網絡應該有的阻抗特性樣子。

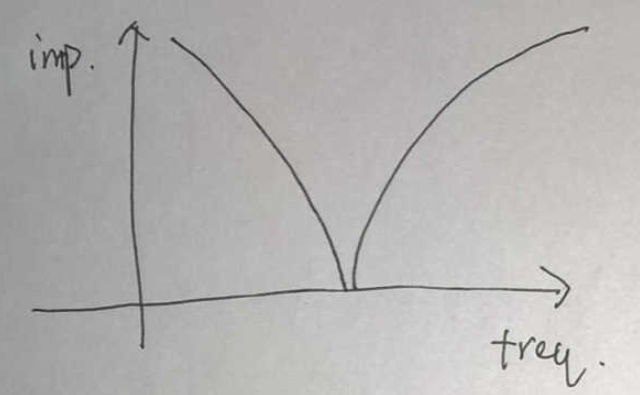

而實際的電容,會有引腳和自身材料特性帶來的等效串聯電感(ESL),所以曲線會變成這幅鬼樣

電解電容值很大,但同時ESL也非常大,所以用它來做低頻上的去耦工作。但是在高頻段,因為很大的ESL,這時候電解電容的“電感特性”占了主導地位,頻率越高去耦效果越弱。有時電路中也會利用大容值電解電容來撫平極低頻段的電壓波動,這時更加多地是在利用電容的儲能特性(你也可以多掏點錢用線性穩壓器來解決這個問題),而不是狹義上的“去耦”或者“濾波”了。

瓷片電容來說雖然容值較小,在低頻段的去耦效果不明顯,但是相對較小的ESL使得它在高頻段特定范圍內的去耦效果非常不錯。

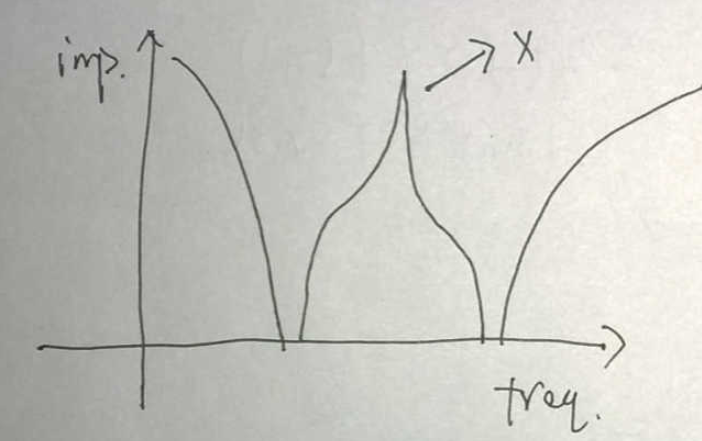

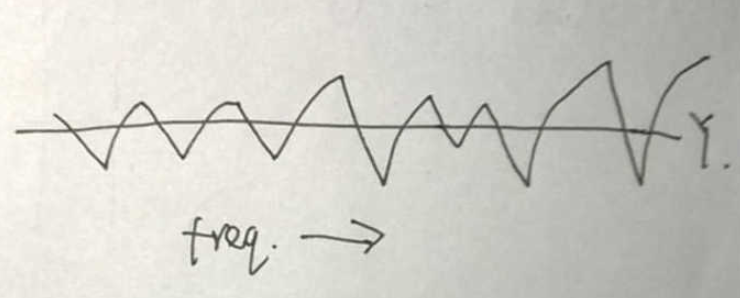

因此,最好的辦法就是把這兩個電容并聯來用。一并起來,阻抗曲線大概就會變成這個樣子

這個理想電容模型的阻抗曲線因為忽略了ESR,顯得非常奇怪,既有尖峰也有為負的阻抗。如果考慮阻抗的相頻特性,在阻抗接近0的時候這個電路組合甚至會發生諧振。所以考察這個問題必須要電容的ESR加進來,如下列形式的電

然后阻抗特性就會變成這樣了

像上圖展示的一樣,這個阻抗特性曲線雖然也有明顯尖銳的峰值和谷值,但是從整體上看,明顯比上圖平滑了很多。峰值部分一般稱為“抗諧振”點(anti-resonance)。既然求電容組合要發揮去耦的作用,那設計要點之一就是這個尖峰必須遠離電路中的噪聲頻率分布集中點。而逆向利用這個尖峰的思路就是把這個峰值盡量靠近臨近負載電流譜頻率集中點上,盡量減少電路拓撲上的相鄰負載變化對本地電壓的影響。

題主的原理圖中和去耦網絡相連的是REF腳,一般都是指參考信號輸入。沒有更多信息,那我就假設一個場景來舉例說明上圖中谷值的意義。假設這是一個ADC的REF引腳,ADC每一個conversion周期都會從REF腳吸取一次或多次電流,具體取決于ADC的電路結構。在這種情況下,REF的電流譜是有規律可循的。我們希望REF腳在工作過程中電壓的波動盡可能少,那就可以將去耦網絡的谷值盡量靠近這個電流譜中的頻率集中點。因為谷值min比ESR值R‘ 要小,在這個頻率上電源網絡對電流信號的阻抗是最低的。這是設計要點之二。

這里還有一個不得不提的問題,就是由去耦網絡帶來潛在的諧振危險。雖然去耦網絡的阻抗在考慮了ESR之后谷值已經不為0了,但是在很多電路中,這個谷值的數值還是相當低的。再加上去耦網絡的另一頭就是電源,盡量減少諧振的發生幾率幾乎成了Design Rule的標配。至于如何消除諧振,又是另一個復雜的話題了。

總結一下,一大一小不同種類的電容并聯,可以用“高低搭配”的方法通俗解釋。但是嚴謹說來,尤其是對于簡單的數字電路,工作過程中電流譜有明顯規律的,相比使用單一電容的結構,兩個電容并聯的組合在成本最優的前提下提供了大量的優化空間(一大一小的ESR和ESL組合)。

上面的都是在理論上泛泛而談,實際上這個優化做起來是非常困難的。主要是電路中影響ESL的參數實在太多了,便宜的電解電容“體質”嚴重不一致使得ESL的失配分析做起來很麻煩。一句話總結就是很難將理論計算結果與做出來的電路對應起來。

對于沒有明顯頻率分布的電路電流譜,又怎么辦呢?最簡單的辦法就是多并不同參數不同規格材料的電容唄,讓這個特性曲線不斷逼近設計需求的“平坦狀態”。

電源完整性(Power Integrity)就是系統研究這類問題的。

作者:瘋狂的蔬菜

-

電解電容

+關注

關注

14文章

677瀏覽量

50946 -

電源完整性

+關注

關注

9文章

211瀏覽量

20749 -

瓷片電容

+關注

關注

0文章

76瀏覽量

14620

發布評論請先 登錄

相關推薦

極性電容和非極性電容并聯的作用

極性電容和非極性電容并聯的作用

評論