在本系列的第 1 部分中,我們將討論如何基于直接數(shù)字頻率合成 (DDFS) 原理設(shè)計(jì)一個(gè)非常精確的正弦波發(fā)生器,但通過(guò)軟件在浮點(diǎn) DSP 處理器上實(shí)現(xiàn)。在第 2 部分中,我們介紹了如何在軟件中實(shí)現(xiàn)高精度 NCO。在本系列的最后一部分中,我們將介紹如何選擇重構(gòu) DAC 并完成 DDFS 系統(tǒng)。

第一個(gè)誘惑是選擇在非線性誤差(INL 和 DNL)方面具有最佳規(guī)格的高精度 DAC,例如AD5791,一個(gè) 20 位精確的 DAC。但是它的分辨率只有 20 位,而且它的 R-2R 架構(gòu)不利于信號(hào)的重構(gòu),尤其是非常純正弦曲線的產(chǎn)生,因?yàn)樗谳斎氪a轉(zhuǎn)換過(guò)程中會(huì)出現(xiàn)很大的毛刺。圍繞二進(jìn)制加權(quán)電流發(fā)生器或電阻網(wǎng)絡(luò)構(gòu)建的傳統(tǒng) DAC 架構(gòu)對(duì)數(shù)字饋通和數(shù)字開關(guān)損傷敏感,例如外部或內(nèi)部時(shí)序偏移和數(shù)字輸入位的其他開關(guān)不對(duì)稱,尤其是在能量變化隨之而來(lái)的主要轉(zhuǎn)換期間。這會(huì)引起與代碼相關(guān)的瞬變,從而導(dǎo)致高幅度的諧波雜散。

在 20+ 位分辨率下,使用外部超線性和快速采樣保持放大器對(duì) DAC 的輸出進(jìn)行去毛刺處理并沒(méi)有多大幫助,因?yàn)樗鼤?huì)在數(shù)十個(gè) LSB 中產(chǎn)生自己的瞬態(tài),并由于重采樣引入群延遲非線性。 對(duì)于信號(hào)重建,主要在通信應(yīng)用中,毛刺問(wèn)題通過(guò)使用分段架構(gòu)來(lái)解決,該架構(gòu)混合了 MSB 的完全解碼部分和最低有效位的二進(jìn)制加權(quán)元素。不幸的是,目前不存在超過(guò) 16 位精度的此類商用 DAC。與 NCO 的完全可預(yù)測(cè)行為不同,DAC 誤差難以準(zhǔn)確估計(jì)和模擬,尤其是當(dāng)制造商的動(dòng)態(tài)規(guī)范相當(dāng)薄弱或不存在時(shí),除了專用于音頻應(yīng)用的 DAC 或 ADC。插值過(guò)采樣和多位 sigma-delta DAC 似乎是唯一足以勝任這項(xiàng)工作的解決方案。這些最先進(jìn)的轉(zhuǎn)換器具有高達(dá) 32 位的分辨率、超低失真和高 SNR,是中低帶寬信號(hào)重建的最佳選擇。為了在音頻頻譜或稍寬的頻帶(20 kHz 或 40 kHz 帶寬)內(nèi)獲得最佳噪聲和失真性能,ADI 產(chǎn)品組合中最好的 Σ-Δ DAC 是AD1955音頻立體聲 DAC,盡管其分辨率限制為 24 位,但仍然是市場(chǎng)上最好的音頻 DAC 之一。

這款音頻 DAC 于 2004 年推出,基于多位 sigma-delta 調(diào)制器和過(guò)采樣技術(shù),并輔以各種技巧來(lái)減輕這種轉(zhuǎn)換原理所固有的失真和其他問(wèn)題。 8

即使在今天,AD1955 也擁有同類產(chǎn)品中最好的插值 LP FIR 濾波器之一。它具有非常高的阻帶衰減 (≈–120 dB) 和非常低的帶內(nèi)紋波 (≈±0.0001 dB)。它的兩個(gè)(左聲道和右聲道)DAC 可以以高達(dá) 200 kSPS 的速度運(yùn)行,但最佳交流性能是在 48 kSPS 和 96 kSPS 下實(shí)現(xiàn)的,其動(dòng)態(tài)范圍和 SNR 均采用典型的 EIAJ 標(biāo)準(zhǔn)、A 加權(quán)、120 dB。立體聲模式。在單聲道模式下,兩個(gè)通道同時(shí)異相組合,可以預(yù)期性能提高 3 dB。然而,對(duì)于寬帶應(yīng)用,這些規(guī)范有些不切實(shí)際,因?yàn)樗鼈兪呛铣傻牟⑶覂H限于 20 Hz 到 20 kHz 的帶寬。超過(guò) 20 kHz 時(shí)不考慮帶外噪聲和雜散,部分原因是 EIAJ 標(biāo)準(zhǔn)、A 加權(quán)濾波器、和音頻行業(yè)規(guī)范定義。這種專用于音頻測(cè)量的帶通濾波器模擬人耳頻率響應(yīng),比未濾波測(cè)量產(chǎn)生 3 dB 更好的結(jié)果。

DDFS 硬件演示平臺(tái):使用 AD1955 重建正弦波

完整的 DDFS 已使用兩塊評(píng)估板實(shí)現(xiàn),一塊支持 DSP 處理器,另一塊用于使用 AD1955 DAC 進(jìn)行模擬信號(hào)重建。第二代SHARC ADSP-21161N選擇評(píng)估板是出于可用性的原因,以及它的易用性和適用于任何音頻應(yīng)用的精簡(jiǎn)配置。ADSP-21161N 仍在生產(chǎn)中,不久前設(shè)計(jì)用于支持工業(yè)、高端消費(fèi)和專業(yè)音頻應(yīng)用,提供高達(dá) 110 Mips 和 660 MFlops 或 220 MMACS/s 的能力。與最新一代的 SHARC 處理器相比,ADSP-21161N 的主要區(qū)別在于其較短的 3 級(jí)指令流水線、片上 1 Mb、僅三端口 RAM 和一組減少的外設(shè)。精密音調(diào)發(fā)生器的最后也是最關(guān)鍵的階段基于 AD1955 評(píng)估板,它必須忠實(shí)地從軟件 NCO 提供的樣本中重建模擬信號(hào)。該評(píng)估板帶有一個(gè)針對(duì)音頻帶寬優(yōu)化的抗混疊濾波器 (AAF),以滿足 Nyquist 標(biāo)準(zhǔn),并且除了通常的 S/PDIF 或 AES-EBU 接收器外,還具有幾個(gè)支持 PCM/I2S 和 DSD 數(shù)字流的串行音頻接口。PCM/I2S 串行鏈路連接器用于將 AD1955 DAC 板連接到 ADSP-21161N EVB 的串行端口 1 和 3 連接器 (J)。兩個(gè)板都可以配置為 I2S PCM 或 DSP 操作模式,采樣率分別為 48 kSPS、96 kSPS 或 192 kSPS。DSP串口1產(chǎn)生左右聲道數(shù)據(jù)、字選擇或L/R幀同步以及雙通道DAC的數(shù)字輸入接口所需的SCK位時(shí)鐘信號(hào)。串行端口 3 僅用于生成 DAC 主時(shí)鐘 MCLK,DAC 插值濾波器和 sigma-delta 調(diào)制器運(yùn)行所需的速度比輸入采樣頻率 (48 kSPS) 快 256 倍(默認(rèn)情況下)。由于所有 DAC 時(shí)鐘信號(hào)均由 DSP 生成,因此電路板原裝低成本 Epson 時(shí)鐘振蕩器已更改為 Crystek 的超低噪聲振蕩器 CCHD-957。對(duì)于 24.576 MHz 的輸出頻率,其相位噪聲規(guī)格在 1 kHz 時(shí)可低至 –148 dB/Hz。

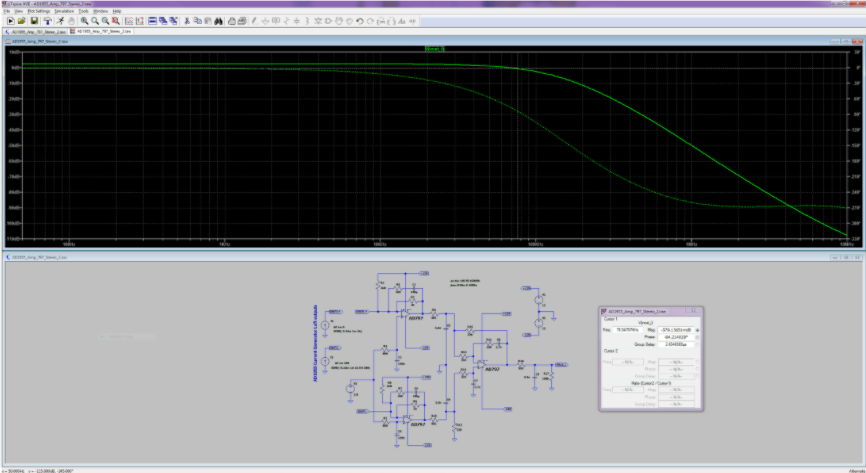

在模擬輸出端,必須使用有源 I/V 轉(zhuǎn)換器將 AD1955 電流差分輸出保持在恒定的共模電壓(通常為 2.8 V),以最大限度地減少失真。超低失真和超低噪聲高精度運(yùn)算放大器(如AD797)用于此目的并處理模擬信號(hào)重建。由于兩個(gè)差分輸出由 DSP 分別處理,因此選擇了具有 AAF 拓?fù)涞牧Ⅲw聲輸出配置,而不是單聲道模式。此 AAF 使用 LTspice XVII 進(jìn)行仿真,結(jié)果如圖 6 所示。由于濾波器的最后一部分是無(wú)源的,因此應(yīng)添加一個(gè)有源差分緩沖級(jí),如最近推出的ADA4945. 這款低噪聲、超低失真、快速建立時(shí)間、全差分放大器是驅(qū)動(dòng)任何高分辨率 SAR 和 sigma-delta ADC 的幾乎完美的 DAC 伴侶。ADA4945 具有相對(duì)較大的共模輸出電壓范圍和出色的直流特性,可提供出色的輸出平衡并有助于抑制偶次諧波失真產(chǎn)物。

EVB 三階濾波器具有 76 kHz 的 –3 dB 截止頻率,在 500 kHz 時(shí)衰減僅為 –31 db。帶內(nèi)平坦度非常好,但這種 LP 濾波器的帶外衰減必須認(rèn)真改進(jìn),即使僅限于純粹的重建音頻應(yīng)用。這是抑制 DAC 整形噪聲以及調(diào)制器時(shí)鐘頻率 MCLK 所必需的。根據(jù)軟件 DDS 用于單音發(fā)生器或任意波形發(fā)生器(用于復(fù)雜波形的 AWG),AAF 將針對(duì)帶外衰減或群延遲失真進(jìn)行優(yōu)化。作為一個(gè)實(shí)際示例和比較,舊的但著名的 SRS DS360 超低失真函數(shù)發(fā)生器已設(shè)計(jì)為具有相似采樣率的七階 Cauer AAF。信號(hào)重建依賴于 AD1862,針對(duì)數(shù)字音頻應(yīng)用的串行輸入 20 位分段 R-2R DAC。AD1862 能夠維持高達(dá) 768 kHz (×16 fS) 的 20 位字采樣率,并具有出色的噪聲和線性度規(guī)格。其單端電流輸出為外部 I-V 轉(zhuǎn)換級(jí)提供了使用最佳放大器的選擇。

圖 6. AD1955 EVB 三階抗混疊濾波器的 LTspice 模擬頻率響應(yīng)(立體聲配置)。

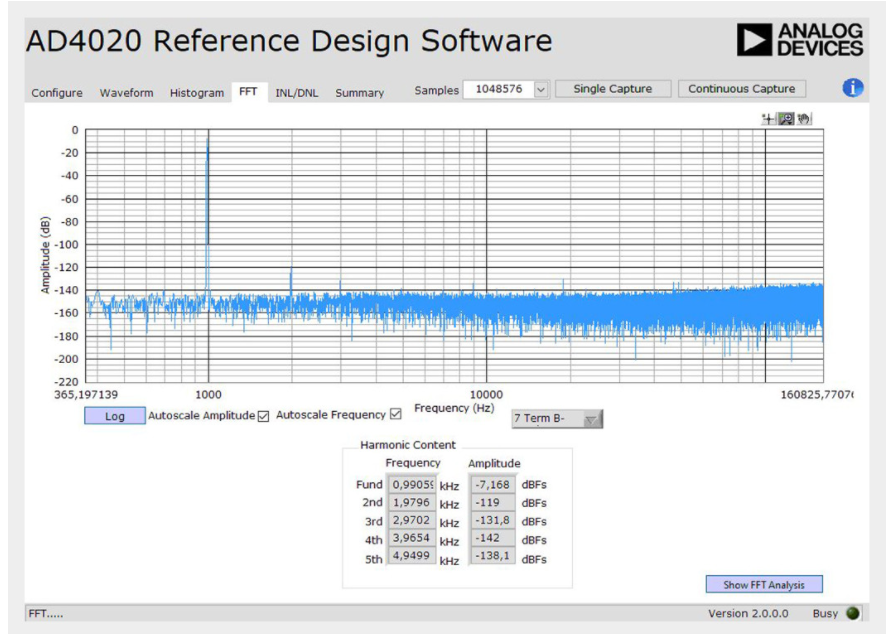

AD1955 和 SHARC DSP 組合針對(duì)多個(gè)高分辨率 SAR ADC(例如AD4020 )進(jìn)行了測(cè)試,中間沒(méi)有外部選擇性無(wú)源濾波器。默認(rèn)情況下,基本 AD4020 評(píng)估板除了板載ADA4807驅(qū)動(dòng)器外別無(wú)選擇。將 ADC 輸入偏置到 V_REF/2 共模電壓的簡(jiǎn)單電路會(huì)施加 300 Ω 的相當(dāng)?shù)偷妮斎胱杩梗⑶倚枰盘?hào)隔離、交流耦合或使用外部差分放大器模塊,例如 EVAL-ADA4945 -1。電路筆記CN-0513中描述的 AD4020 參考設(shè)計(jì)板是更好的選擇。它包括一個(gè)分立的可編程增益儀表放大器 (PGIA),它提供高輸入阻抗并接受 ±5 V 差分輸入信號(hào) (G = 1)。盡管這些 AD4020 板及其 SDP-H1 控制器缺乏支持相干采樣采集的能力,但它們?cè)试S對(duì)樣本進(jìn)行適當(dāng)?shù)牟ㄐ尾东@長(zhǎng)度,范圍高達(dá) 1M。因此,具有選擇性開窗的長(zhǎng) FFT 是可能的,同時(shí)提供精細(xì)的頻率分辨率和低本底噪聲。例如,對(duì)于七項(xiàng) Blackman-Harris 窗口,圖 7 中所示的 1 Mpts FFT 圖說(shuō)明了 AD1955 對(duì)于 990.059 Hz 生成的正弦波的失真水平。二次諧波是 350 kHz 帶寬內(nèi) –111.8 dBc 處的最大失真分量和最大雜散。然而,

圖 7. 1 M 點(diǎn) FFT 分析顯示失真非常好,H2 低于 –111 dBc,對(duì)于 1 kHz 輸入頻率,在 10 kHz 至 200 kHz 頻帶內(nèi)具有最大雜散。本底噪聲約為 –146 dBFS。

在相同條件下,對(duì)老式 AD1862 進(jìn)行了測(cè)試,其光譜行為略有不同。在差分配置中,兩個(gè)時(shí)鐘頻率約為 500 kSPS 的 20 位 DAC 報(bào)告的本底噪聲為 –151 dBFS,THD 為 –104.5 dB,正弦輸出電平為 12 V pp,頻率為 1.130566 kHz。AD4020 奈奎斯特帶寬 (806 kHz) 上的 SFDR 接近 106 dB,受三次諧波限制。基于兩個(gè)AD743低噪聲 FET 放大器的 DAC 重建濾波器是類似于 AD1955 評(píng)估板的一個(gè)三階濾波器,但在 –3 dB 處具有 35 kHz 的截止頻率。

為了變得有效,基于 DDS 的發(fā)生器需要一個(gè)合適的濾波器,該濾波器能夠在大約 250 kHz 處衰減大于 100 dB,以生成 dc 至 25 kHz CW 信號(hào)頻率范圍。這可以通過(guò)六階 Chebyshev 甚至六階 Butterworth LP 濾波器來(lái)實(shí)現(xiàn),以獲得完美的帶內(nèi)平坦度。濾波器的階數(shù)將被最小化,以限制模擬級(jí)的數(shù)量及其非理想性,例如噪聲和失真。

結(jié)論

在標(biāo)準(zhǔn)評(píng)估板上進(jìn)行的初步和開箱即用測(cè)試表明,基于處理器的 DDS 技術(shù)可用于具有頂級(jí)性能的傳統(tǒng)正弦波 CW 生成。精心設(shè)計(jì)的重建濾波器和模擬輸出緩沖級(jí)可以滿足 –120 dBc 的諧波失真系數(shù)。基于 DSP 的 NCO/DDS 不僅限于生成單音正弦波。通過(guò)使用具有適當(dāng)截止頻率且無(wú)需更改其他硬件的優(yōu)化 AAF(貝塞爾或巴特沃斯),可以將相同的 DSP 和 DAC 組合偽裝成高性能 AWG 以產(chǎn)生任何類型的波形,例如,合成完全可參數(shù)化的多音正弦波,可完全控制 IMD 測(cè)試中每個(gè)組件的相位和幅度。

由于浮點(diǎn)運(yùn)算對(duì)于需要高精度和/或高動(dòng)態(tài)范圍的應(yīng)用至關(guān)重要,因此如今的 SHARC+ DSP 處理器,如低成本ADSP-21571或 SoC ADSP-SC571(ARM 和 SHARC)是實(shí)時(shí)處理高達(dá) 10 MSPS 的聚合采樣率的事實(shí)標(biāo)準(zhǔn)。時(shí)鐘頻率為 500 MHz,雙 SHARC 內(nèi)核及其硬件加速器可提供超過(guò) 5 Gflops 的計(jì)算性能并提供大量?jī)?nèi)部專用 SRAM,這是生成任何類型波形以及復(fù)雜波形的任務(wù)所需的基本成分分析處理。這種類型的應(yīng)用表明,系統(tǒng)地使用硬件可編程解決方案對(duì)于處理精密數(shù)字信號(hào)處理并不是強(qiáng)制性的。浮點(diǎn)處理器及其完整的開發(fā)環(huán)境允許從 MATLAB 等模擬器輕松快速地移植代碼,

關(guān)于作者

Patrick Butler 是 ADI 公司南歐銷售部門的一名現(xiàn)場(chǎng)應(yīng)用工程師,負(fù)責(zé)為法國(guó)全球市場(chǎng)和一些 ADEF 客戶提供支持。自 1984 年以來(lái),他一直在 ADI 工作,支持 DSP 構(gòu)建模塊 IC 以及高速轉(zhuǎn)換器。此前,他曾在法國(guó)圣艾蒂安的斯倫貝謝公司 ATE 部門擔(dān)任設(shè)計(jì)工程師五年,然后在南特的 Matra-MHS、AMD 和 Harris SC-Intersil 擔(dān)任多個(gè)應(yīng)用工程師和 FAE 職位。如今,他的主要愛好是在兩個(gè)兒子的幫助下收集老式聲音組件來(lái)構(gòu)建有源、高效的號(hào)角揚(yáng)聲器系統(tǒng)。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8707瀏覽量

147251 -

濾波器

+關(guān)注

關(guān)注

161文章

7826瀏覽量

178203

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何通過(guò)SPI接口去操控DAC?

使用51單片機(jī)對(duì)DAC7718輸入信號(hào),信號(hào)無(wú)法識(shí)別,為什么?

DAC161P997的配置寄存器如何工作?通過(guò)什么選擇?

基于相變材料的可重構(gòu)超構(gòu)表面用于圖像處理

能否使用ADS1262的REFOUT緩沖后提供給外部DAC?

智能選擇ADC/DAC可實(shí)現(xiàn)更好的軟件定義無(wú)線電設(shè)計(jì)

時(shí)鐘噪聲對(duì)DAC性能影響系統(tǒng)分析

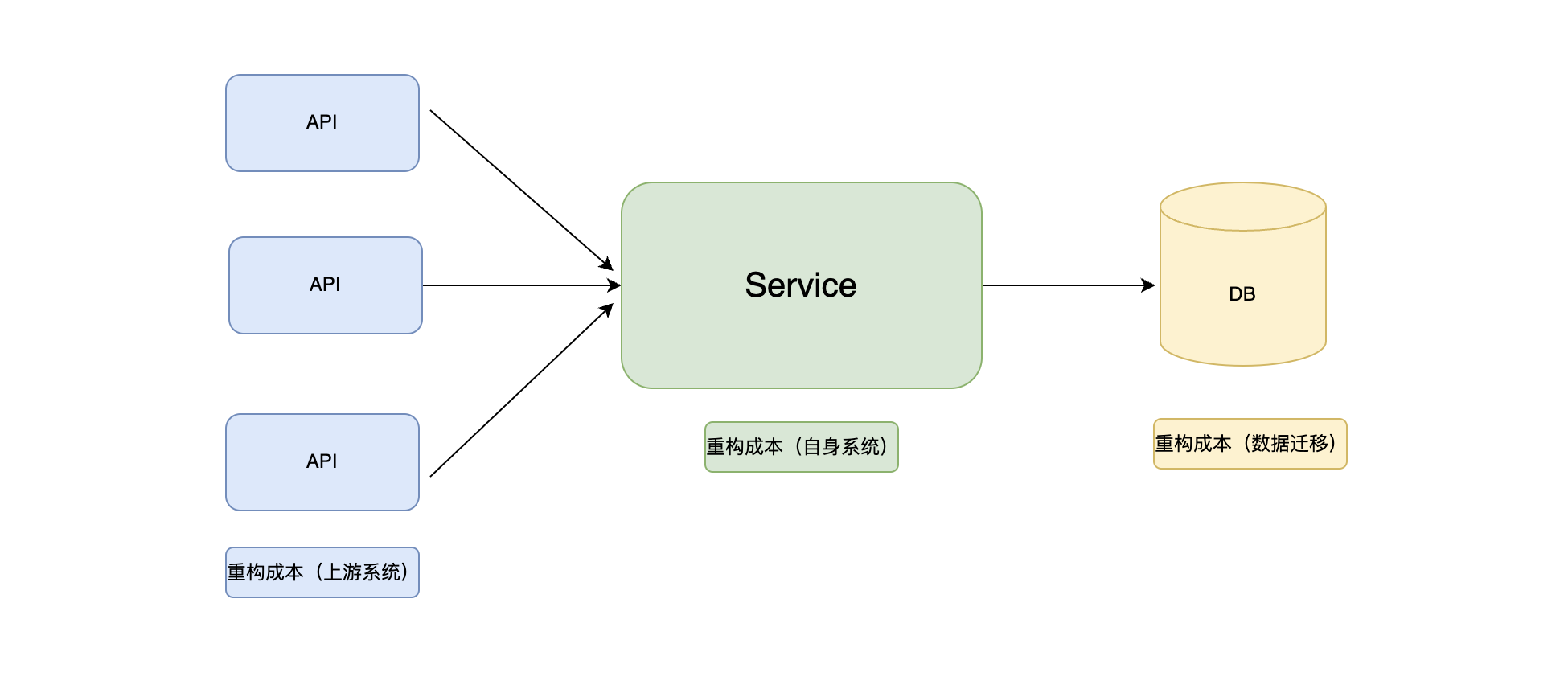

「重構(gòu):改善既有代碼的設(shè)計(jì)」實(shí)戰(zhàn)篇

如何在RT-Thread系統(tǒng)下用ESP8266連上EMQX的公用服務(wù)器并完成數(shù)據(jù)收發(fā)?

DAC63204.DAC53204.DAC43204數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

DAC3152/DAC3162數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

求助,關(guān)于DAC外部觸發(fā)轉(zhuǎn)換問(wèn)題求解

CS32G020 DAC觸發(fā)源選擇定時(shí)器時(shí),無(wú)法觸發(fā)DAC轉(zhuǎn)換?

深度操作系統(tǒng)V23 Beta3發(fā)布,提升用戶體驗(yàn)并兼容Steam原生應(yīng)用

STM32U5系列TIMER+DMA+DAC應(yīng)用演示

如何選擇重構(gòu) DAC并完成DDFS系統(tǒng)

如何選擇重構(gòu) DAC并完成DDFS系統(tǒng)

評(píng)論