2nm、GAA、3D封裝、chiplet、異構(gòu)....近年來(lái),隨著半導(dǎo)體工藝的進(jìn)步,單顆IC的晶體管數(shù)量已經(jīng)從百億向千億甚至萬(wàn)億數(shù)量發(fā)展,功能復(fù)雜需求也讓單顆IC也集成了越來(lái)越多的IP,此外 ,工藝的進(jìn)步也帶來(lái)了制造商良率的問(wèn)題,這都給IC設(shè)計(jì)師帶來(lái)了極大的挑戰(zhàn),一方面要應(yīng)付工藝、復(fù)雜度提升帶來(lái)的設(shè)計(jì)難度挑戰(zhàn),另外還要應(yīng)付time-to-market帶來(lái)的效率壓力。

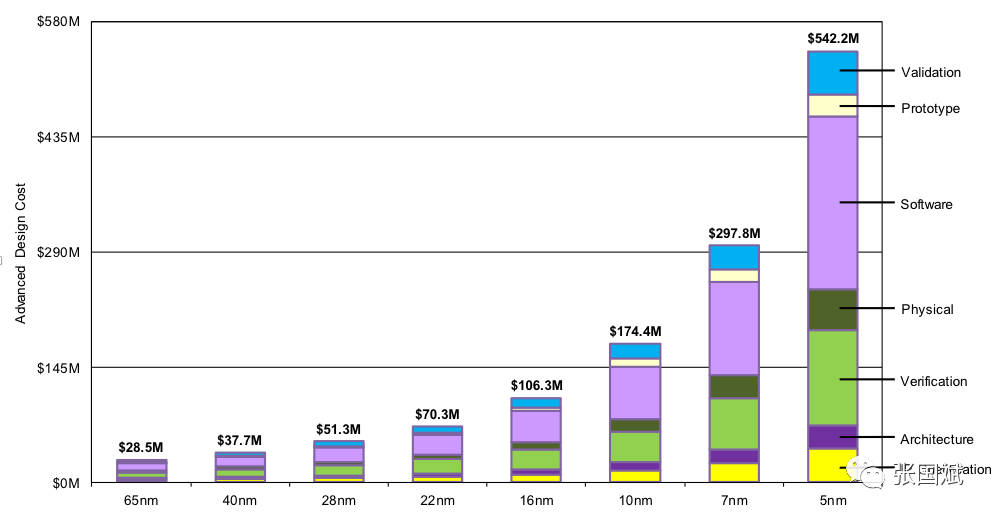

而熟悉IC設(shè)計(jì)的人都知道,過(guò)去十年中,IC設(shè)計(jì)中仿真驗(yàn)證成本的增長(zhǎng)速度遠(yuǎn)高于設(shè)計(jì)成本。數(shù)據(jù)表明,包括工程師、軟件、硬件在內(nèi)的驗(yàn)證資源占到整個(gè)前端設(shè)計(jì)的70%,而設(shè)計(jì)本身只占30%,所以仿真驗(yàn)證在整個(gè)集成電路行業(yè)當(dāng)中的占比會(huì)越來(lái)越高,而且隨著工藝的升級(jí),所占比還在提升(如上圖所示),所以要確保芯片高效開發(fā),就要提升仿真驗(yàn)證的效率。

5月31日,在電子創(chuàng)新網(wǎng)旗下芯英雄聯(lián)盟直播頻道舉辦的《EDA仿真最新趨勢(shì)和效率提升》線上直播活動(dòng)中,華為數(shù)據(jù)存儲(chǔ)半導(dǎo)體行業(yè)解決方案架構(gòu)師施鉆專和概倫電子研發(fā)副總裁方君分享了提升EDA仿真效率一些做法。

1、華為存儲(chǔ)四大舉措提升EDA仿真效率

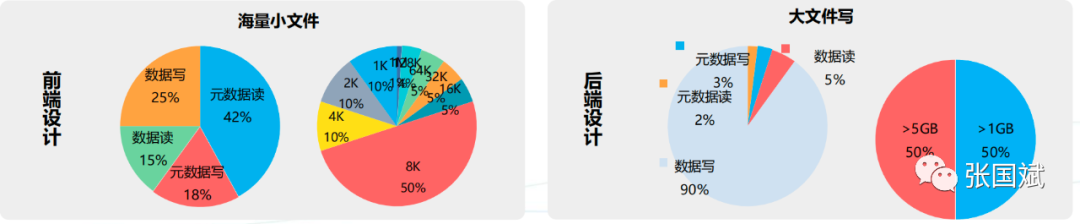

施鉆專指出,目前,EDA仿真平臺(tái)面臨幾個(gè)困境,一個(gè)是面對(duì)混合型業(yè)務(wù),存儲(chǔ)更容易成為瓶頸。這是因?yàn)镋DA仿真主要分前端業(yè)務(wù)和后端業(yè)務(wù)。前端業(yè)務(wù)主要以RTL編碼仿真為主,數(shù)據(jù)特點(diǎn)基本都是KB級(jí)別的小文件,并且主要是8KB左右的文件為主,超過(guò)60%以上都是元數(shù)據(jù)讀寫,這類場(chǎng)景針對(duì)存儲(chǔ)的要求就是更高的OPS性能訴求。后端業(yè)務(wù),主要以綜合優(yōu)化仿真、編譯網(wǎng)表及網(wǎng)表測(cè)試為主,主要是GB級(jí)別的大文件寫場(chǎng)景,這類場(chǎng)景對(duì)存儲(chǔ)性能要求帶寬更高。

EDA仿真平臺(tái)面臨的另個(gè)困境是解決方案不匹配或者不會(huì)用,表現(xiàn)在:

1、服務(wù)器本地盤方案資源利用率低投資浪費(fèi),表現(xiàn)為項(xiàng)目組間資源無(wú)法調(diào)度無(wú)法共享;Temp文件增長(zhǎng)迅速服務(wù)器容量受限容易爆盤;無(wú)專業(yè)存儲(chǔ)企業(yè)特性,易用性差;數(shù)據(jù)安全無(wú)法保障等。

2、共享存儲(chǔ)方案選型不對(duì)、導(dǎo)致仿真性能差影響研發(fā)進(jìn)度。主要表現(xiàn)為分布式文件系統(tǒng)分片機(jī)制只適合大文件大帶寬場(chǎng)景、萬(wàn)億海量KB級(jí)小文件性能不足,存儲(chǔ)時(shí)延高,仿真卡頓、Lustre等文件系統(tǒng)需MDS等額外元數(shù)據(jù)節(jié)點(diǎn)服務(wù)器,增加故障點(diǎn)、高負(fù)載下刪除時(shí),EDA軟件卡頓等。

3、專業(yè)存儲(chǔ)不會(huì)規(guī)劃使用,具體表現(xiàn)為不懂如何確保仿真業(yè)務(wù)不中斷、關(guān)鍵仿真任務(wù)高效執(zhí)行、不懂如何確保高價(jià)值數(shù)據(jù)安全性?不懂如何實(shí)現(xiàn)業(yè)務(wù)安全隔離、不懂如何在有限的存儲(chǔ)空間實(shí)現(xiàn)價(jià)值最大化,這樣會(huì)導(dǎo)致資源利用率低、投資浪費(fèi)等。

針對(duì)這樣的痛點(diǎn),華為存儲(chǔ)是如何提升EDA仿真效率的呢?施鉆專表示華為存儲(chǔ)聯(lián)合IC設(shè)計(jì)企業(yè)在EDA設(shè)計(jì)仿真過(guò)程中的業(yè)務(wù)訴求,通過(guò)系列化的優(yōu)化,打造半導(dǎo)體設(shè)計(jì)EDA存儲(chǔ)解決方案,大幅縮短EDA仿真周期。

概括起來(lái),有四大舉措:

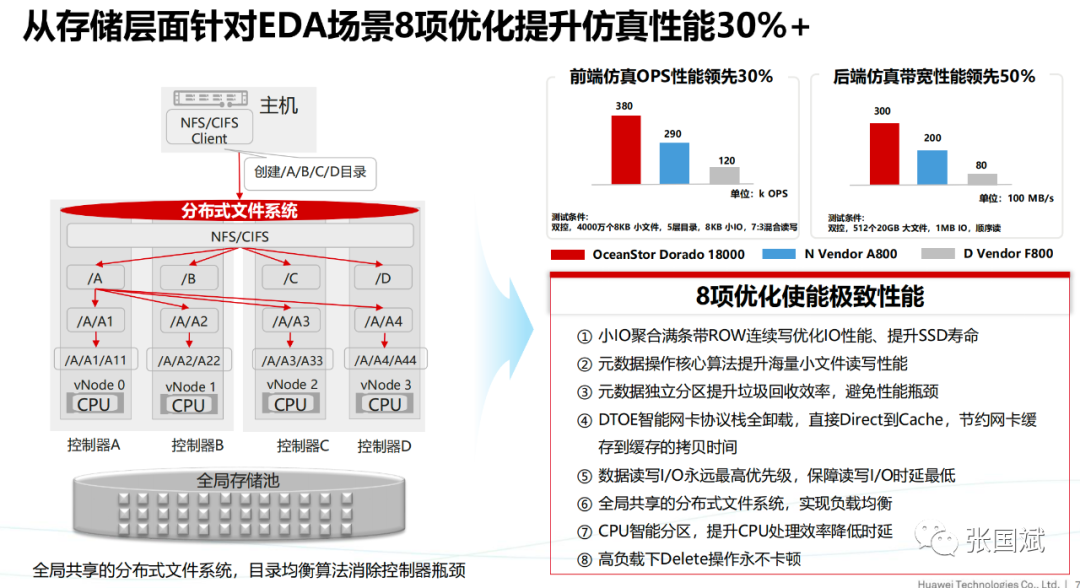

1、從存儲(chǔ)層面針對(duì)EDA場(chǎng)景8項(xiàng)優(yōu)化提升仿真性能30%+

施鉆專表示針對(duì)海量小文件場(chǎng)景,可以通過(guò)小IO聚合滿條帶ROW連續(xù)寫來(lái)優(yōu)化IO性能,同時(shí)也提升了SSD壽命。

針對(duì)大量的元數(shù)據(jù)操作,通過(guò)多項(xiàng)核心算法,比如元數(shù)據(jù)的壓緊算法,元數(shù)據(jù)的預(yù)取與淘汰算法等,提升元數(shù)據(jù)操作性能。

元數(shù)據(jù)和數(shù)據(jù)獨(dú)立分區(qū),有利于提升垃圾回收效率,消除性能瓶頸。

在硬件方面,華為存儲(chǔ)專門用了DTOE的智能網(wǎng)卡,把協(xié)議從CPU卸載到網(wǎng)卡上,節(jié)約網(wǎng)卡緩存到緩存的拷貝時(shí)間。

CPU需要處理讀寫IO、GC、快照等其他特性,把讀寫IO優(yōu)先級(jí)排最高,這樣可以保障讀寫IO的時(shí)延最低。

華為存儲(chǔ)采用全局共享的分布式文件系統(tǒng),基于目錄均衡打散,消除控制器的瓶頸,支持自動(dòng)遷移熱點(diǎn)目錄到空閑控制器上,實(shí)現(xiàn)自動(dòng)負(fù)載均衡。

華為存儲(chǔ)使用多核鯤鵬920 CPU,通過(guò)CPU智能分區(qū),綁核處理,避免跨CPU核跨控開銷,提升CPU的處理效率、降低時(shí)延。

EDA場(chǎng)景會(huì)有大量刪除Temp文件的操作,華為存儲(chǔ)專門針對(duì)刪除操作做了CPU綁核處理,專核專用,確保高負(fù)載情況下Delete操作不卡頓。

2、全閃存介質(zhì)升級(jí),能效優(yōu)化降低整體TCO

施鉆專表示存儲(chǔ)介質(zhì)主要分HDD機(jī)械硬盤以及SSD全閃存硬盤。以前大多數(shù)IC設(shè)計(jì)企業(yè),會(huì)選擇采用1.2TB左右的HDD機(jī)械硬盤,通過(guò)好幾個(gè)硬盤柜來(lái)堆存儲(chǔ)性能,但是這樣會(huì)導(dǎo)致機(jī)房空間、功耗大幅增高。目前越來(lái)越多的IC設(shè)計(jì)企業(yè),尤其是一些先進(jìn)制程的比如7nm、5nm芯片設(shè)計(jì)企業(yè),為了性能需求會(huì)選擇SSD全閃存存儲(chǔ)。

從投入產(chǎn)出比看,SSD應(yīng)用可以大大降低企業(yè)的運(yùn)維成本,相比于傳統(tǒng)存儲(chǔ)需要配置幾十個(gè)磁盤機(jī)柜、上萬(wàn)塊HDD磁盤,SSD只需要幾個(gè)機(jī)柜即可;SSD不僅在空間需求上優(yōu)勢(shì)明顯,在能耗、運(yùn)維成本上也非常突出:相對(duì)于HDD,在相同的容量下,SSD的電力能耗降低70%,空間占用節(jié)省50%。在存儲(chǔ)系統(tǒng)中每更換1塊SSD,帶來(lái)的節(jié)能減排效果,相當(dāng)于種了150棵樹,以及3360個(gè)普通家庭熄燈一小時(shí)。

3、存儲(chǔ)層豐富的企業(yè)軟件特性,幫助IC設(shè)計(jì)企業(yè)更好的管理數(shù)據(jù)提升效率

華為存儲(chǔ)提供了很多豐富的軟件特性,幫助IC設(shè)計(jì)企業(yè)更好的管理數(shù)據(jù),提升工作效率。如多租戶特性可以用來(lái)確保數(shù)據(jù)安全隔離。

施鉆專表示EDA仿真臨時(shí)文件較多,如果不做及時(shí)刪除,空間就會(huì)被快速消耗掉,影響到其他用戶,這個(gè)問(wèn)題可以通過(guò)設(shè)置配額的方式來(lái)解決,確保存儲(chǔ)空間的有效利用。有些關(guān)鍵仿真為了不被其他任務(wù)擠占掉存儲(chǔ)性能資源,會(huì)特別設(shè)置一個(gè)關(guān)鍵VIP任務(wù)的最低性能要求,來(lái)確保仿真任務(wù)高效完成。

海量小文件一直都是EDA仿真場(chǎng)景的最大難題,華為存儲(chǔ)不是通過(guò)備份軟件對(duì)應(yīng)用層掃描的方式來(lái)備份,而是通過(guò)底層的快照技術(shù)和異步復(fù)制技術(shù),來(lái)做到Disk to Disk的快速備份,可以有效提升幾倍甚至十倍的性能提升。

4、存儲(chǔ)層四級(jí)可靠為EDA仿真平臺(tái)平穩(wěn)運(yùn)行保駕護(hù)航

永遠(yuǎn)在線的方案:通過(guò)業(yè)界唯一的NAS Active-Active雙活解決方案,確保單套存儲(chǔ)故障時(shí)不會(huì)影響生產(chǎn)。

永遠(yuǎn)在線的系統(tǒng):通過(guò)RAID TP可以容忍3塊硬盤同時(shí)失效,另外全閃存儲(chǔ)重構(gòu)1TB時(shí)間只需要15分鐘,解決塊硬盤不影響生產(chǎn)的問(wèn)題。

永遠(yuǎn)在線的架構(gòu):通過(guò)Smart Matrix全互聯(lián)架構(gòu)和獨(dú)有的SMB Failover功能,可以容忍單套存儲(chǔ)系統(tǒng)內(nèi)單個(gè)引擎故障或者7個(gè)控制器故障,業(yè)務(wù)不中斷。

永遠(yuǎn)在線的SSD:通過(guò)全局磨損與反磨損,來(lái)提升SSD的使用壽命,降低IT運(yùn)維人員壓力。

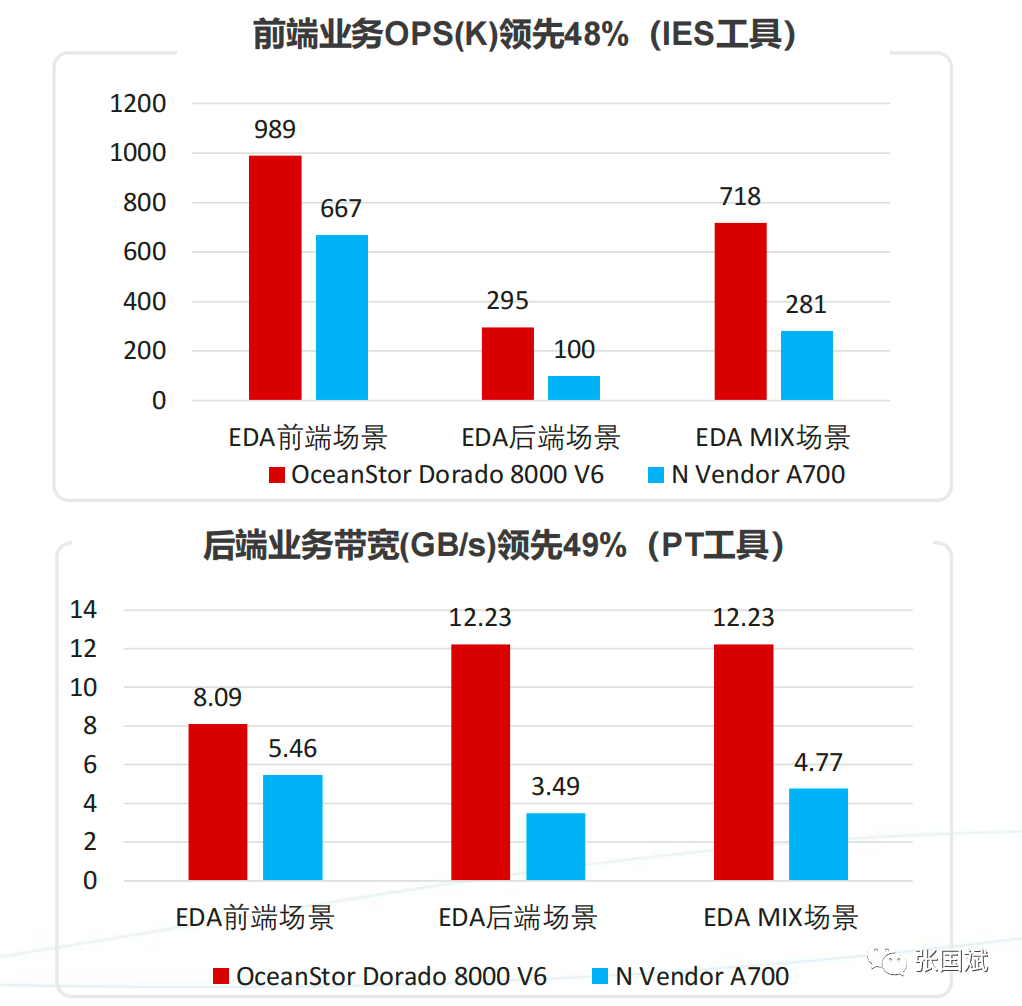

施鉆專特別指出華為存儲(chǔ)在海思EDA仿真平臺(tái)使用表明使用之后其前端業(yè)務(wù)OPS領(lǐng)先48% ,后端業(yè)務(wù)帶寬領(lǐng)先49%!

2、概倫電子如何提升EDA仿真效率?

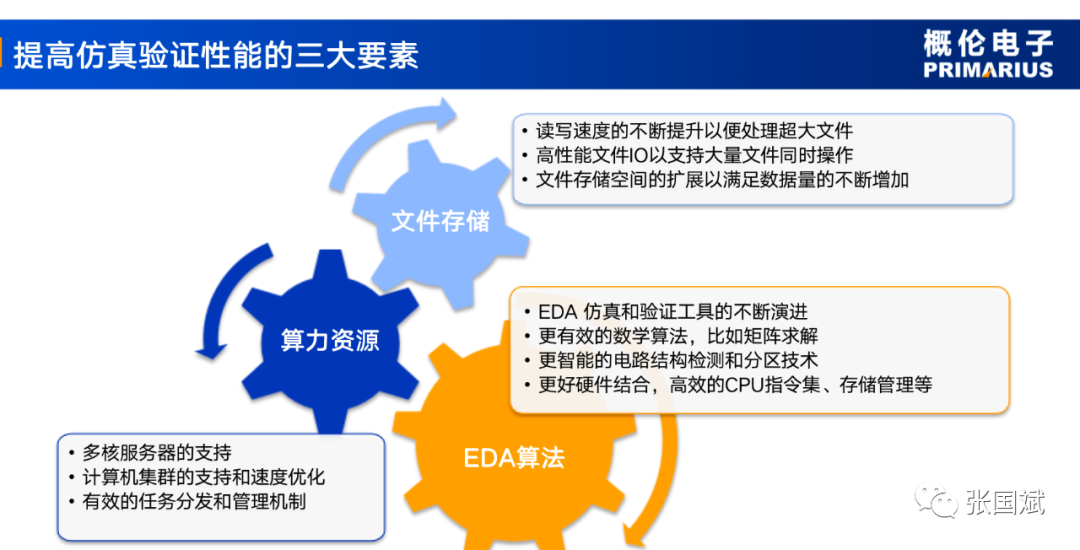

方君認(rèn)為可以通過(guò)三個(gè)方面提升EDA仿真效率,分別是文件存儲(chǔ)、EDA算法和算力資源。

文件存儲(chǔ)體現(xiàn)在讀寫速度的不斷提升以便處理超大文件、高性能文件IO以支持大量文件同時(shí)操作以及文件存儲(chǔ)空間的擴(kuò)展以滿足數(shù)據(jù)量的不斷增加。

EDA算法層面體現(xiàn)在EDA 仿真和驗(yàn)證工具的不斷演進(jìn)、更有效的數(shù)學(xué)算法,比如矩陣求解、更智能的電路結(jié)構(gòu)檢測(cè)和分區(qū)技術(shù)、更好硬件結(jié)合,高效的CPU指令集、存儲(chǔ)管理等;

算力資源體現(xiàn)在多核服務(wù)器的支持、計(jì)算機(jī)集群的支持和速度優(yōu)化、有效的任務(wù)分發(fā)和管理機(jī)制等。

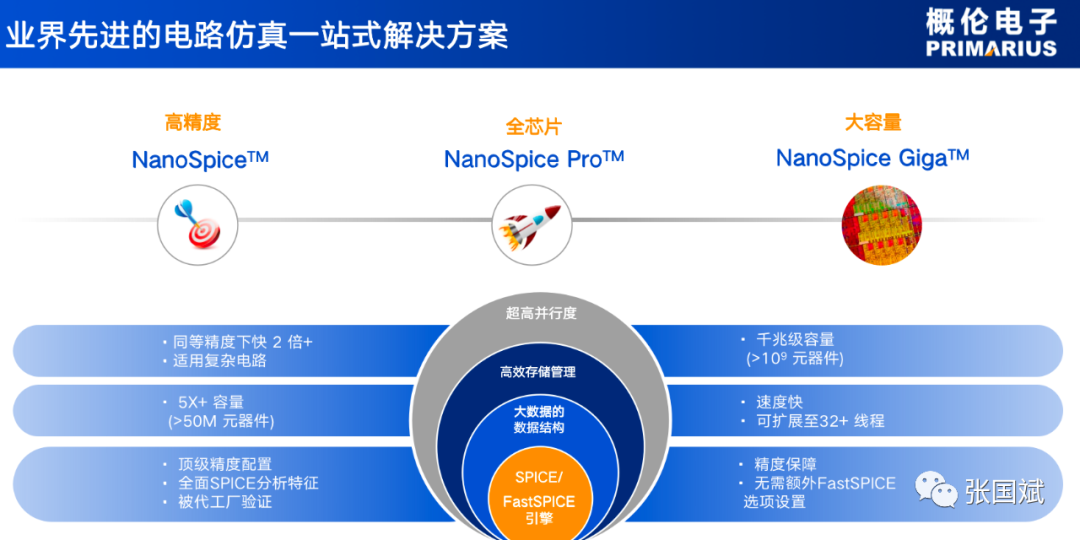

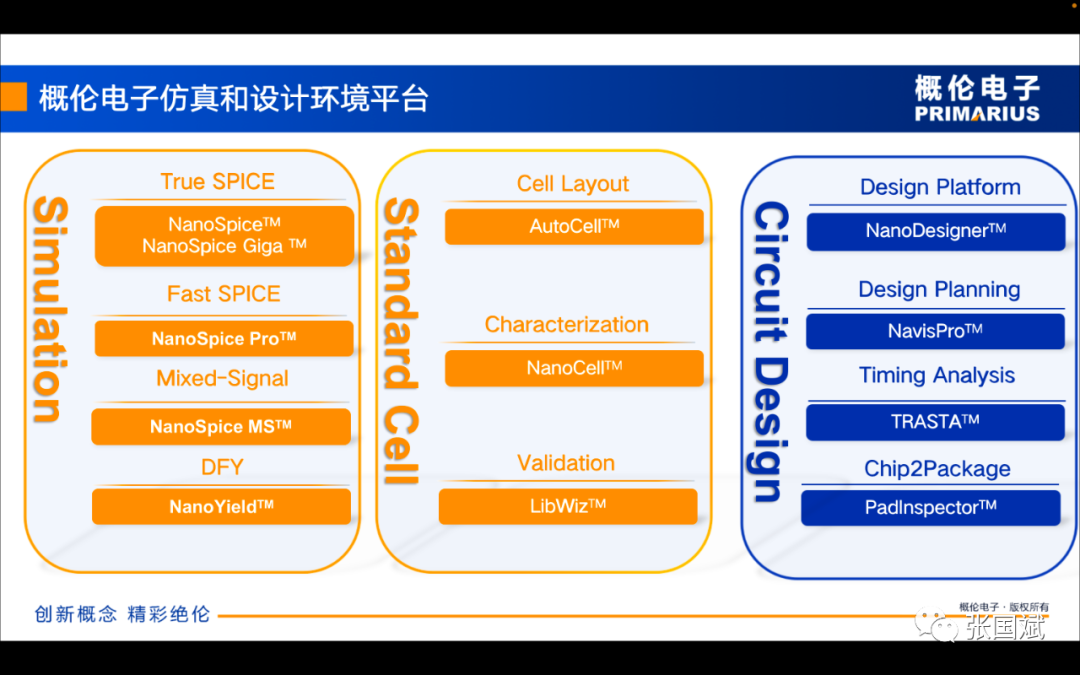

他指出概倫電子提供的是融合上述三個(gè)要素的一站式仿真解決方案,從仿真工具到標(biāo)準(zhǔn)單元庫(kù)再到電路設(shè)計(jì)都有覆蓋。

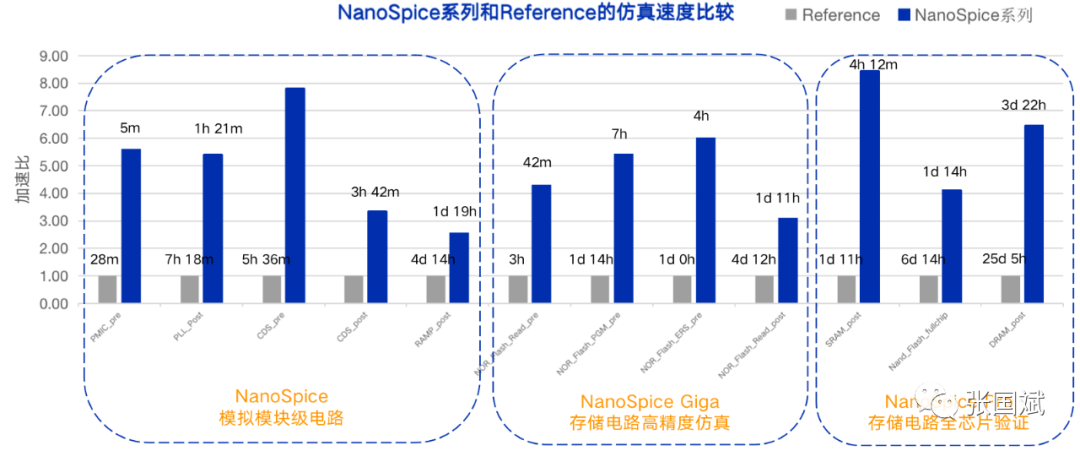

如NanoSpice就是概倫電子推出的新一代大容量、高精度、高性能并行SPICE電路仿真器,覆蓋模塊級(jí)模擬電路到全芯片存儲(chǔ)器電路,特別對(duì)高精度模擬電路和大規(guī)模后仿電路的電路仿真進(jìn)行優(yōu)化,同時(shí)滿足高精度、大容量和高性能的高端電路仿真需求。

NanoSpice Pro是一款概倫電子自主研發(fā)的FastSPICE電路仿真器,可滿足存儲(chǔ)器單元設(shè)計(jì)、存儲(chǔ)陣列和編譯器驗(yàn)證、存儲(chǔ)器特征化及全芯片驗(yàn)證等所有需求,相比其它同類仿真器性能有較明顯提高。

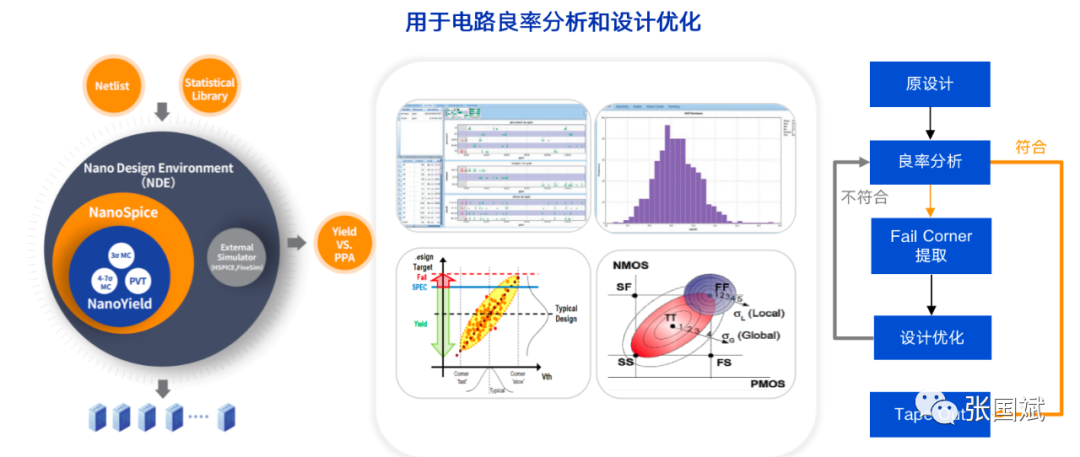

而概倫電子的NanoYield良率導(dǎo)向設(shè)計(jì)平臺(tái)則可以用于電路良率分析和設(shè)計(jì)優(yōu)化。

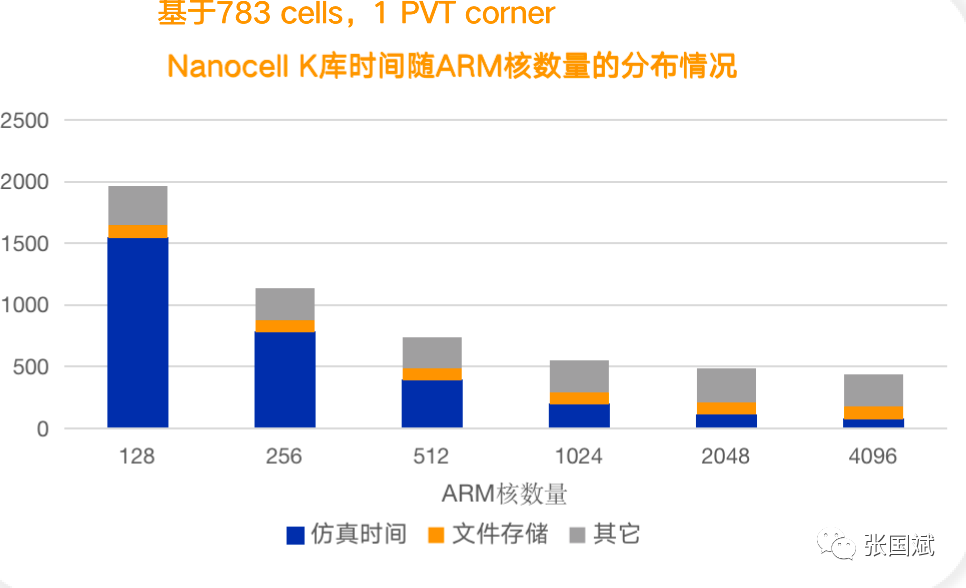

方君表示概倫電子的NanoCell 是一款快速精確且易用的標(biāo)準(zhǔn)單元庫(kù)特征化 EDA 工 具,它通過(guò)內(nèi)置的 NanoSpice仿真器,采用先進(jìn)的分布式并行架構(gòu)技術(shù)和單元電路分析提取算法,精確且高效的對(duì)單元電路進(jìn)行時(shí)序、功耗及噪聲等特征進(jìn)行仿真與提取,提供友好易使用的接口,幫助用戶縮短產(chǎn)品開發(fā)周期。它支持ARM/X86 環(huán)境。

此外他還強(qiáng)調(diào),概倫電子建設(shè)有基于ARM架構(gòu)的計(jì)算服務(wù)中心,服務(wù)器超過(guò)800臺(tái),CPU超過(guò)10萬(wàn)核,內(nèi)存達(dá)800TB;服務(wù)器本地存儲(chǔ)為10PB、集中高速存儲(chǔ):270TB,網(wǎng)絡(luò)方面支持25G網(wǎng)絡(luò)互連 ,最大100G帶寬 、支持全鏈路負(fù)載均負(fù)載。

他強(qiáng)調(diào)概倫電子會(huì)圍繞三大要素持續(xù)和改進(jìn)以提升EDA仿真效率。

半導(dǎo)體工藝會(huì)不斷演進(jìn),未來(lái)EDA工具的重要性日益凸顯,隨著人工智能、大數(shù)據(jù)的應(yīng)用深入 ,EDA仿真效率將不斷提升,助力IC設(shè)計(jì)師設(shè)計(jì)出更復(fù)雜更高性能的IC產(chǎn)品。

審核編輯 :李倩

-

仿真

+關(guān)注

關(guān)注

50文章

4109瀏覽量

133781 -

eda

+關(guān)注

關(guān)注

71文章

2772瀏覽量

173494 -

晶體管

+關(guān)注

關(guān)注

77文章

9711瀏覽量

138579

原文標(biāo)題:如何大幅度提升EDA仿真效率?華為、概倫電子專家這樣說(shuō)

文章出處:【微信號(hào):motorcontrol365,微信公眾號(hào):電機(jī)控制設(shè)計(jì)加油站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

UVLED固化機(jī)結(jié)構(gòu)的四大模塊

華為存儲(chǔ)四大舉措提升EDA仿真效率

華為存儲(chǔ)四大舉措提升EDA仿真效率

評(píng)論