業界正在接受嵌入式現場可編程門陣列 (eFPGA),因為該技術已在多個流行工藝節點的硅片中可用并得到驗證。eFPGA 正在以多種方式集成到芯片中,包括作為可重新配置的 I/O 處理器或加速器,在數據路徑或控制路徑中。這種方法的好處是它通過不將加速器綁定到固定功能來提供靈活性。

為此,芯片設計人員可以創建從 eFPGA 到 ARM 架構的高級外圍總線 (APB)、AMBA 高性能總線 (AHB) 和 AMBA 高級可擴展接口 (AXI) 總線的連接,從最簡單的接口到APB 從機到最復雜的 AXI 主機。

隨著網絡、深度學習和人工智能 (AI) 以及航空航天和國防等應用對硬件加速的需求不斷增長,對片上系統 (SoC) 和微控制器 (MCU) 設計的需求也在不斷發展。如今,常見的 SoC 具有集成數字信號處理 (DSP) 和 FPGA IP 塊,專用于特定 I/O 或處理工作負載,而主 CPU 內核處理通用任務。這些架構支持更高效、更靈活的整體處理解決方案。

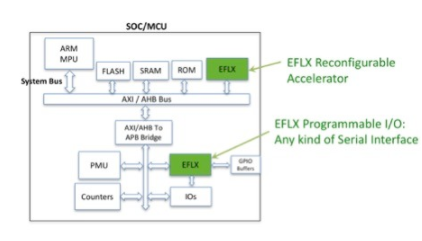

尤其是 eFPGA,由于上述原因,最近越來越受歡迎。與傳統的 DSP 和 FPGA 不同,eFPGA 可以作為可重新配置的 IP 塊設計到芯片中,可以重新編程以處理不同的工作負載加速任務或在芯片組的整個生命周期內管理不同的 I/O(圖 1)。

圖 1. Flex Logix 的 EFLX eFPGA IP 可以在 MCU 和 SoC 設計中實現為可重新配置的硬件加速塊或可重新編程的 I/O 塊。]

例如,對于使用 ARM 架構的芯片設計人員,eFPGA 可以連接到 APB、AHB 或 AXI 處理器總線以利用這些優勢。但是,考慮到多種組合(主/從 x AXI/AHB/APB x 外部接口邏輯或使用 eFPGA 實現),應仔細考慮這些設計。

eFPGA I/O 資源

為了更好地了解如何使用標準接口將 eFPGA 設計成基于 ARM 的 MCU 或 SoC,我們將以 Flex Logix EFLX-2.5K 嵌入式 FPGA IP 內核為例。

EFLX-2.5K eFPGA 是一個 1x1 陣列,由 2,520 個具有 632 個輸入和 632 個輸出的六輸入查找表 (LUT) 組成。它在 16 nm 工藝中的工作頻率約為 1 GHz,在 28 nm 工藝中優于 500 MHz。因此,即使是最小的 eFPGA 也具有足以連接到最寬、最快的 ARM 總線的 I/O 資源和速度。

(注意:最大 7x7 的更大數組是可能的,每個增加的數組大小的 I/O 數量計算為 NxM 數組中的 N*632 輸入和 N*632 輸出。增加數組大小的 LUT 數量類似計算為 N*M*2520。)

eFPGA 作為 APB 從機

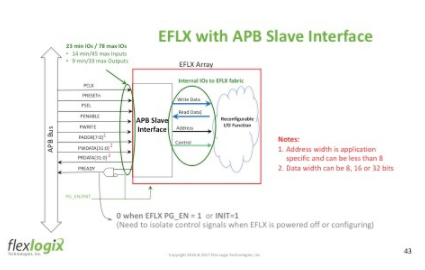

配置為 APB 從機的 eFPGA 通常會實現為可重新配置的 I/O 功能。例如,多種串行接口中的一種可以包括 UART、I2C 和 SPI。

在這種配置中,多個模塊連接到 APB 總線,該總線一次在一個模塊上運行(圖 2)。每個塊都有內存映射的地址空間(例如 128 個寄存器的 8 位),而總線上的數據可以是 8、16 或 32 位。8 位地址空間和 32 位數據需要 45 個輸入和 33 個輸出,而 16 位總線使用更少的 16 個輸入和 16 個輸出。

圖 2.配置為 APB 從機的 eFPGA 通常實現為包含多個存儲器映射塊的可配置 I/O 功能。APB 總線在每一個上同步運行。

APB 從接口快速、簡單,可以在外部實現,也可以在 eFPGA 的邏輯中實現。例如,在此配置中,EFLX eFPGA 需要少于 10 個 LUT。如圖 3 所示,APB 從接口 Verilog 代碼和狀態圖也很簡短。

圖 3.當 eFPGA 配置為 APB 從接口時,Verilog 代碼和狀態圖很簡單。

eFPGA 作為 AXI 主機

AXI 總線由三個版本組成:AXI4、AXI4 Stream 和 AXI4 Lite。

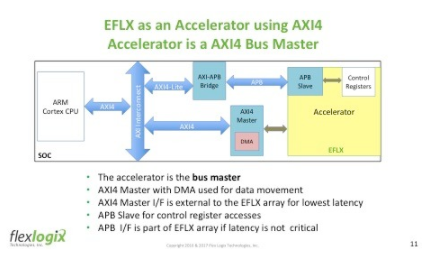

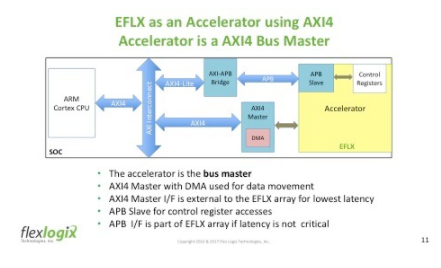

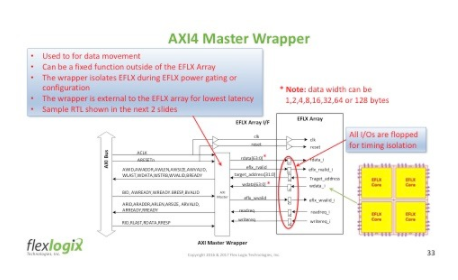

圖 4 顯示了具有在 eFPGA 外部實現的包裝器的 AXI4 主設備。AXI 主包裝器的功能是處理所有總線協議,管理數據流控制,并在配置期間將 EFLX FPGA 與 AXI 總線隔離。

在這里,EFLX Reconfigurable Accelerator 充當總線主控器,因此 CPU 不需要向內存傳輸數據和從內存傳輸數據。這可以將 CPU 卸載到可以與 EFLX 加速器并行運行的其他任務上。

圖 4.配置為 AXI 主設備的 EFLX 可重配置加速器可以減輕 CPU 的總線管理任務負擔。

EFLX eFPGA 能夠支持窄或非常寬(128 字節)的 AXI 數據寬度,具體取決于加速器功能所需的帶寬。EFLX 陣列中的控制寄存器和 APB 從屬邏輯在 EFLX 陣列中實現并通過 APB 總線進行控制。圖 2 所示的 APB 從接口示例可以實現控制寄存器接口。

圖 5 顯示了 AXI 總線架構的高級圖,說明了主從連接。在將 eFPGA 實現為 AXI 主設備時,應始終翻轉 eFPGA 以簡化關閉、定時、輸入和輸出到/輸出。數據總線寬度可以是 1、2 或 4 字節等,最多 128 字節。

圖 5.為了簡化 AXI 總線中的主從連接,建議對 eFPGA 進行翻轉。

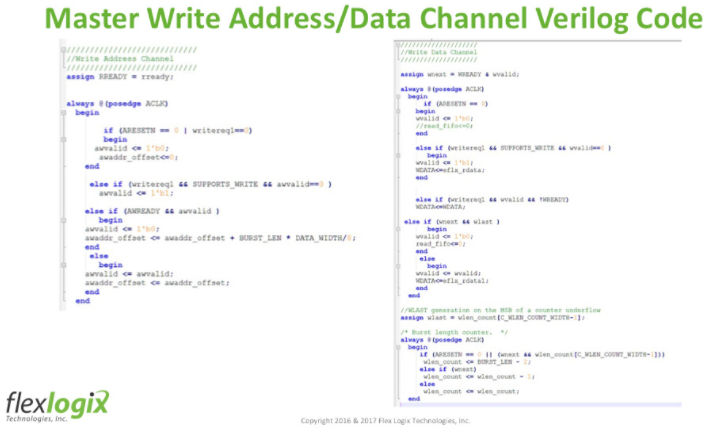

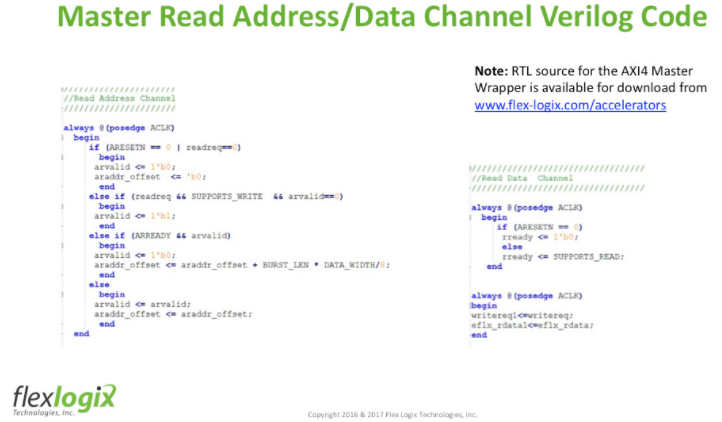

即使對于復雜的總線主控,Verilog 代碼也相對簡單(圖 6)。

圖 6.使用 eFPGA 作為 AXI 總線主控器時,Verliog 代碼仍然相對簡單。

eFPGA 通過單獨的從接口

除了作為加速器或 I/O 處理器的陣列操作的總線連接之外,EFLX 等 eFPGA 還提供了一個單獨的從接口,用于加載配置位以根據需要進行重新配置。外部 AXI 從包裝器也可用于與配置端口連接。

例如,使用 EFLX,配置位通常存儲在與 ARM 處理器代碼相同的閃存中。處理器啟動后,它使用直接存儲器訪問 (DMA) 通過配置從接口將配置位訪問到 eFPGA。

結論

隨著現代處理解決方案對靈活性和性能的需求日益增長,eFPGA 可以使用少量高速邏輯輕松連接到任何類型和寬度的 ARM 總線。經過多年的復雜性和成本挑戰,基于 eFPGA 技術的可重構加速器和 I/O 處理器已成為任何基于 ARM 的 SoC 或 ASIC 架構師的易于使用的資源。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19293瀏覽量

229966 -

asic

+關注

關注

34文章

1200瀏覽量

120515 -

寄存器

+關注

關注

31文章

5343瀏覽量

120448

發布評論請先 登錄

相關推薦

ARM嵌入式通信協議及應用

ARM嵌入式編程高效技巧

歐時推介微芯嵌入式控制解決方案

嵌入式系統設計參考解決方案

嵌入式常用總線有哪些

ARM MCU嵌入式開發 | 基于國產GD32F10x芯片+嵌入的開始

【「ARM MCU嵌入式開發 | 基于國產GD32F10x芯片」閱讀體驗】+書籍整體概況

ARMxy ARM嵌入式計算機支持Ubuntu OS快速部署AIoT解決方案

ARMxy ARM嵌入式計算機搭載 1 TOPS NPU支持深度學習

嵌入式FPGA與ARM總線連接支持整體處理解決方案

嵌入式FPGA與ARM總線連接支持整體處理解決方案

評論