經驗豐富的 ASIC 工程師可能會告訴項目團隊的初級成員,沒有捷徑可走,尤其是當挑戰因素發揮作用時,例如:如果設計要在現代、激進的工藝節點上實施;或者,如果項目團隊依賴的半導體知識產權 (IP) 可以占芯片的 70% 之多;或者如果 ASIC 有 5 億個或更多的門;或者,如果項目團隊將部分或全部設計委托給合同設計公司,他們可以省去很多細節,但信任一個單獨的組織。在任何這些情況下走捷徑都可能出錯。

然而,這并不意味著沒有途徑可以簡化設計過程。每次確保項目成功都需要使用基于多年實踐項目管理經驗的設計管理系統,以確保每個項目都按計劃進行并實現其目標。因此,以下重點關注設計 ASIC 設計管理系統和實施已成為工程師和管理人員重要資源的決策。

設計管理系統簡化流程

設計公司在設計芯片時有許多目標,從實現最高性能設計到在盡可能短的時間內完成設計,同時保持高質量。

ASIC 設計人員通常比 FPGA 設計人員需要考慮更多。例如,大部分設計可以由第三方 IP 或以前實現的代碼片段組成。此外,工藝技術變得越來越小,而門數繼續增加,使得驗證(或驗證 ASIC 是否按預期工作)成為必要。

因此,ASIC 設計管理系統的目標是以最小的開銷提供項目的一致性,以便所有設計都以可預測的方式進行。

隨著新的半導體工藝技術的發展,每個設計都受到越來越復雜的工具鏈的影響。項目管理的一個困難和對一致性的威脅是每個工程師對設計應該如何通過工具有不同的想法。例如,個別工程師喜歡通過調用工具和管理結果的腳本來自動化他們的 ASIC 設計部分的流程。他或她可能有一個腳本例程,有助于簡化詳細時序分析的輸出結果。如果管理不當,這可能會導致“簡歷依賴”,即每個項目都根據工程師的歷史、技能和突發奇想進行管理。如果發生這種情況,如果工程師加入或離開公司,每個項目都會面臨風險,并且很難將工程師從一個項目轉移到另一個項目。

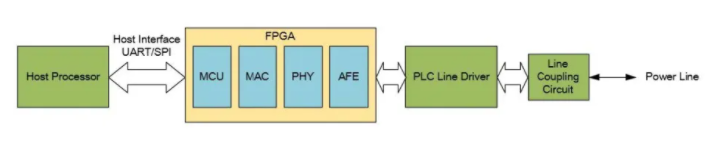

ASIC 設計管理系統是一個基于軟件的平臺,它提供了一種標準的、一致的方式來進行所有設計(圖 2),通過使用不同的模塊來平衡所有項目的需求,包括數據管理器、構建管理器、分析儀和監視器。

圖 2: ASIC 設計管理系統為每個設計提供一致的格式。例如,其中一個系統包括數據管理器、構建管理器以及分析器和監視器。

文件、文件和更多文件

在項目的生命周期中,將使用和創建許多文件,并調用許多工具,分析結果并用于確定下一步做什么。設計管理系統通過在整個芯片實現過程中提供一致的方法和流程來自動化和管理這個過程。

ASIC 設計中的事情很容易出錯,并且很容易相信其他人已經完成的先前工作。從腳本到代碼再到庫文件,在不檢查所有內容的情況下繼續進行可能會產生可能導致返工的問題。

種類繁多的庫文件就是一個很好的例子,尤其是當第三方 IP 與反映不同過程變體和角落的大量文件一起使用時。即使有已建立的流程,在這些文件中發現軟件錯誤也并不罕見,并且存在真正的風險,即直到項目后期才能發現此類錯誤。由于庫文件和數據的變體如此之多,很容易錯誤地使用錯誤的變體,因此需要一種管理修訂控制的方法。

通常,這些庫文件是通過從原始位置復制到項目的數據結構中來手動管理的,這很容易出錯。文件名或目錄名可能指示哪些文件,但這些名稱可能與文件中的內容無關,并且實際上可能是錯誤的。這就是設計管理系統可以通過自動定位、審查和存儲項目的所有輸入文件來提供幫助的地方。它解析(分析、組織和分發)文件的內容,以確保不會發生錯誤。它強制執行標準文件結構,因此可以在設計階段的早期發現潛在問題,而不是在它們可能影響進度和成本時發現。

自動化分析在設計的早期審查中起著至關重要的作用。掃描所有設計和 IP 文件以提取層次結構、跟蹤時鐘并檢查模塊連接性。來自這些早期分析的信息有助于設計工程師將精力集中在設計中更有問題的領域。

自動優化

完成預設計分析后,即可繼續進行設計工作。構建管理器和分析器模塊是此階段的重要組件。構建管理器封裝了整個 ASIC 流程,確保每個項目都具有相同的結構。個別工程師不維護自己的構建腳本。相反,設計管理系統自動生成構建腳本(程序指令集)并為用于設計 ASIC 的 EDA 工具所需的所有各種文件創建工作目錄。

ASIC 設計不是一個線性過程,許多設計策略中的哪一個可能最有效可能并不明顯。構建經理創建并運行一系列不同的設計選項,以便項目團隊可以審查它們并找到最佳解決方案。

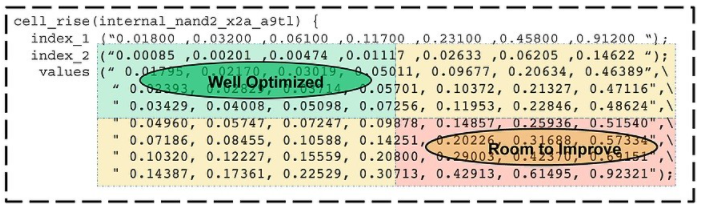

同時,分析器執行結果聚合和優化(圖 3)。從綜合和仿真到驗證和測試的各種電子設計工具將生成大量不同的結果文件,對于人類來說,這些文件不易閱讀,難以識別最緊迫的問題。分析器從文件中提取結果并將它們匯總在一個地方,從而更容易查看當前構建的狀態。

圖 3:分析器模塊從文件中提取結果并將它們匯總在一個地方。

實現 ASIC 頂層

借助設計管理系統,ASIC 設計中的各個模塊可以直接實現。每個工程師都從平面圖中分配了一塊不動產,假設有足夠的硅區域可以工作,則該區域內的布局和布線可以順利進行。它需要額外的邏輯和互連來將塊連接到一個單一的設計中頂級,這可能具有挑戰性。

在設計平面圖時,為頂層 ASIC 集成留出空間以確保頂層邏輯(組件)能夠適應通道是至關重要的。這些添加的組件必須填充到成品塊周圍和穿過的通道中。

根據大小和復雜性,一個芯片設計項目可能涉及少數到數十名工程師,他們同時在不同的模塊上工作。項目經理希望了解項目的不同方面是如何進行的。

顧名思義,監控模塊對每個設計活動的當前狀態具有持續可見性。由于它在后臺工作,它使管理人員可以了解進度,而不會干擾和減慢設計工作。任何可識別的問題都將可見。因為它們被及早發現,所以它們可以及早修復,隨著項目的進展,進度表不太可能出現。

到達終點線

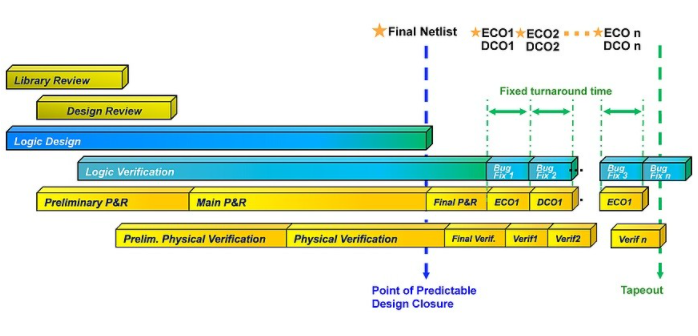

流片是項目中最關鍵的時間,必須解決對設計的任何最終更改。其中包括 ECO(對網表的更改)和 DCO(對 RTL 代碼的更改)(參見圖 4)。在理想情況下,對設計的所有更改都將在流片之前就位。實際上,最終設計變更將被識別并且必須在最終流片之前解決,這是設計過程的預期部分。

設計管理系統應該能夠適應最后一刻的更改并將它們合并到設計中,而無需返回并重新開始。由于設計管理系統可以直接訪問所有項目數據,它可以快速接受設計更改并使用新數據自動重新運行設計。

圖 4:設計管理系統可以適應最后一刻的更改并將它們合并到設計中。

贏得高風險的 ASIC 設計游戲

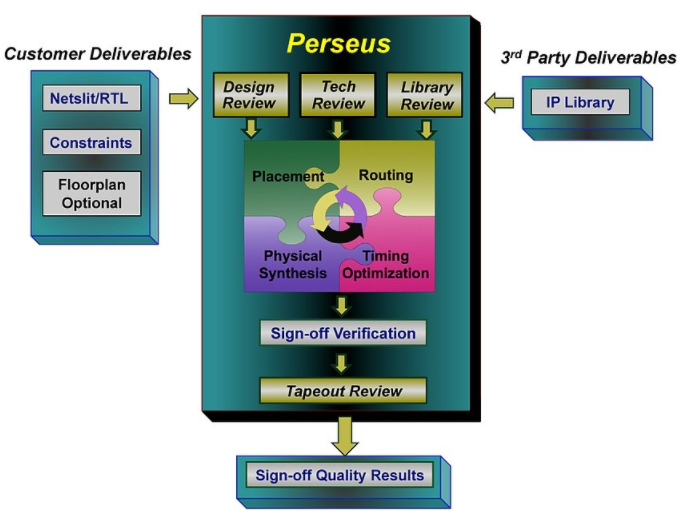

ASIC 設計的風險是巨大的,從失去市場機會和收入到公司因設計失敗而倒閉。在冒險走捷徑時,很多事情都會出錯。通過建立標準的項目流程和結構,項目團隊可以自信地參與每個新項目,相信它將以可預測、有序的方式進行——這比走捷徑要好得多。該過程應包括設計管理系統的實施。例如,Uniquify 開發并實施了 Perseus,這是一個構成項目主干的設計管理系統。這樣的設計管理系統是設計師和管理者的關鍵資源。

審核編輯:郭婷

-

芯片

+關注

關注

456文章

51075瀏覽量

425880 -

asic

+關注

關注

34文章

1205瀏覽量

120625 -

eda

+關注

關注

71文章

2777瀏覽量

173547

發布評論請先 登錄

相關推薦

ASIC和GPU的原理和優勢

ASIC集成電路如何提高系統效率

【《軟件開發珠璣》閱讀體驗】居安思危之風險

用于完善智能電表設計的FPGA到ASIC研究

“新一代”漏洞掃描管理系統:網絡安全風險管理利器

設計管理系統消除了ASIC捷徑風險

設計管理系統消除了ASIC捷徑風險

評論