ZYNQ從放棄到入門(十二)- AMP — Zynq 上的非對稱多核處理器

之前介紹的所有文章我們都只使用了一個 ARM Cortex-A9 處理器內(nèi)核(Core 0)。然而,PS 端包含兩個處理器內(nèi)核,對于許多應用程序,我們希望同時使用兩個 Zynq 內(nèi)核以獲得最佳性能。將兩個 Zynq 處理器內(nèi)核用于不同的任務可以稱為非對稱多核處理 (AMP,Asymmetric Multiprocessing),并且可以涉及以下任意組合:

Core 0 和 Core 1 上運行不同操作系統(tǒng)

Core 0 上運行操作系統(tǒng),Core 1 上運行裸機代碼(反之亦然)

兩個Core上的裸機代碼執(zhí)行不同的程序

AMP介紹

有兩種多核處理方式:對稱和非對稱。在我們定義兩者之間的區(qū)別之前,我們首先必須定義什么是多核處理:“多核處理是在系統(tǒng)中使用多個處理器。這可以允許同時執(zhí)行多條指令。但是,它不一定非要如此。” 對稱和非對稱多核處理之間的區(qū)別是

對稱多核處理通過將處理進程分布在多個微處理器內(nèi)核上來同時運行多個軟件任務

非對稱多處理使用專門的處理器來運行特定的應用程序或在相同的處理器上運行專門的應用程序

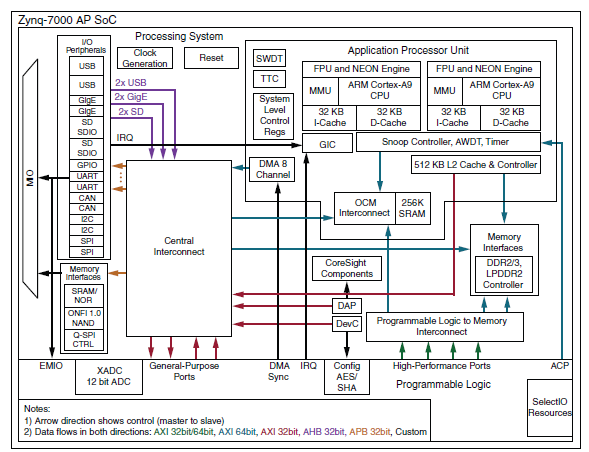

在接下來的幾篇博客中,我們將介紹 Zynq SoC 上的 AMP。首先,我們研究兩個裸機應用程序,每個應用程序都運行在不同的core上。在 Zynq SoC 上運行 AMP 時,必須考慮 Zynq 處理器core混合了私有資源和共享資源。兩個處理器都有私有的 L1 指令和數(shù)據(jù)緩存、定時器和看門狗以及共享的中斷控制器(共享和私有中斷)。然而,Zynq 上的中斷并不那么簡單,因為 PS 中的每個內(nèi)核都能夠使用軟件中斷來中斷自己、另一個處理器或兩個處理器,這些中斷是通過中斷控制器來分發(fā)的。

Zynq SoC 還擁有大量共享資源,常見示例包括 I/O 外設、片上存儲器、中斷控制器分配器、L2 高速緩存和位于 DDR 存儲器內(nèi)的系統(tǒng)存儲器。下圖顯示了其中一些資源。

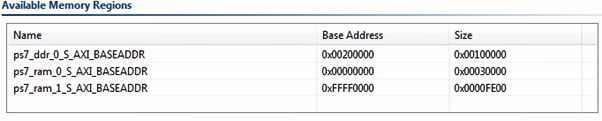

我們將從 DDR 內(nèi)存運行兩個處理器內(nèi)核,因此我們必須非常小心地對每個處理器使用的地址區(qū)域進行分段。地址是通過每個應用程序的鏈接描述文件確定的。如果我們對此處理不當,在不同內(nèi)核上運行的應用程序可能會干擾彼此的操作。

我們還必須修改 SDK 自動生成的文件以使系統(tǒng)啟動并運行。第一步將根據(jù)XAPP1079(http://www.xilinx.com/support/documentation/application_notes/xapp1079-amp-bare-metal-cortex-a9.pdf)修改第一階段引導加載程序,它將檢查裸機/裸機 AMP。

我最初打算創(chuàng)建一個非常簡單的系統(tǒng),一旦它啟動并運行,我們就可以對其進行擴展。第一個應用程序將讓 Zynq SoC 的處理器 Core 0 通過 RS232 與用戶通信,而 Core 1 在驅動連接到 ZYNQ IO 的 LEDS 。這兩個應用程序無需交互即可同時運行。

啟動和運行AMP

雖然啟動和運行 AMP 需要幾個步驟,但它實際上是非常簡單直接的過程,當然沒什么好害怕的。

讓 AMP 在 Zynq SoC 上運行的關鍵方面是引導加載程序,它在將第一個可執(zhí)行文件加載到內(nèi)存后查找第二個可執(zhí)行文件。為了簡單化,我將使用賽靈思應用筆記 XAPP1079 中提供的修改后的 FSBL 和修改后的獨立操作系統(tǒng)。(源文件可在此處獲得http://www.xilinx.com/support/documentation/application_notes/xapp1079-amp-bare-metal-cortex-a9.pdf)

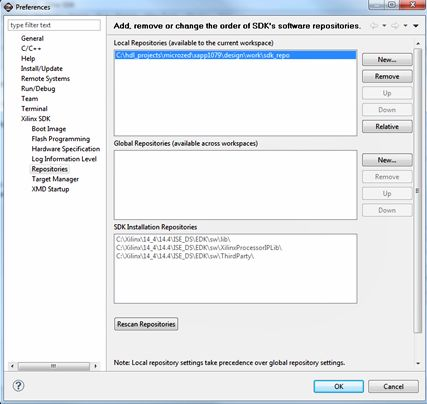

下載 zip 文件后,第一步是將壓縮文件解壓縮到所需的工作目錄中,并將名為 SRC 的文件夾重命名為 design。這些文件包含修改后的 FSBL 和修改后的獨立操作系統(tǒng)。我們需要 SDK 了解這些文件,因此下一步是更新 SDK 存儲庫(repository)以使 SDK 了解它們的存在。在 SDK的Xilinx 工具菜單下中,選擇存儲庫,然后選擇新建,導航到目錄位置 <工作目錄>app1079designworksdk_repo,如下所示:

在存儲庫中添加后,下一階段是生成以下內(nèi)容:

AMP 第一階段引導加載程序

core 0 應用程序

core 1 應用程序

我們將為其中的每一個core生成一個 BSP(板級支持包)。

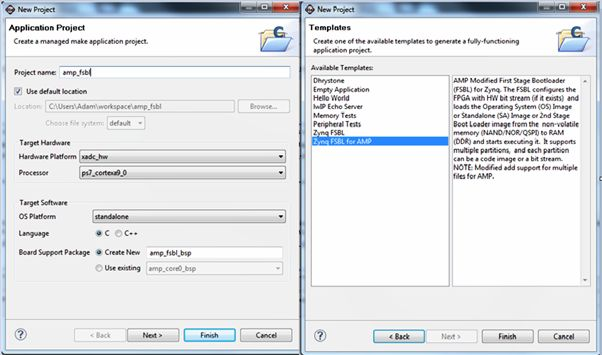

首先要做的是創(chuàng)建一個新的 FSBL。選擇file -> new application -> project,這使我們能夠創(chuàng)建一個支持 AMP 的 FSBL 項目。這與我們之前所做的相同,但是我們將選擇 Zynq FSBL for AMP 模板來代替 Zynq FSBL 模板。

在創(chuàng)建 AMP FSBL 之后,我們需要為第一個內(nèi)核創(chuàng)建應用程序。這又很簡單,我們以前做過很多次了。確保選擇 Core 0 和獨立操作系統(tǒng)并允許它創(chuàng)建自己的 BSP。

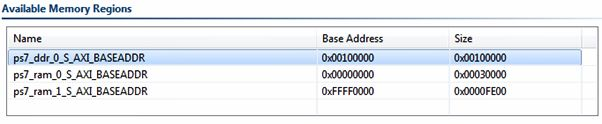

一旦我們創(chuàng)建了這個應用程序,我們需要在 DDR 內(nèi)存中正確定義應用程序將執(zhí)行的位置。為此,我們?nèi)缦戮庉嬫溄用枋鑫募燥@示 DDR 基地址和大小。這個很重要,如果我們沒有對 Core 0 和 Core 1 應用程序的 DDR 內(nèi)存進行正確分段,我們就有可能無意中損壞另一個應用程序。

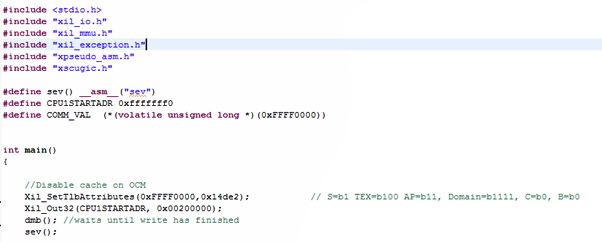

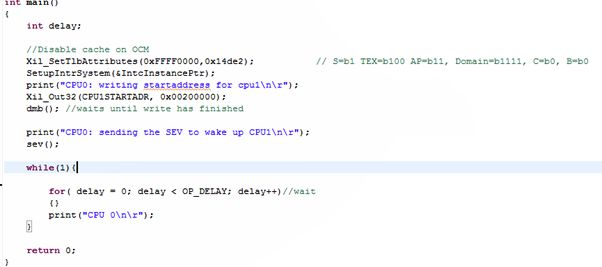

我們現(xiàn)在可以編寫我們希望在core 0 上執(zhí)行的應用程序。我們需要將以下代碼部分包含在應用中。

此代碼禁用 Zynq SoC 片上存儲器上的緩存,并將 Core 1 程序的起始地址寫入 Core 1 將在 Core 0 執(zhí)行 Set Event (SEV) 命令后訪問的地址。SEV 命令使 Core 1 開始執(zhí)行其程序。

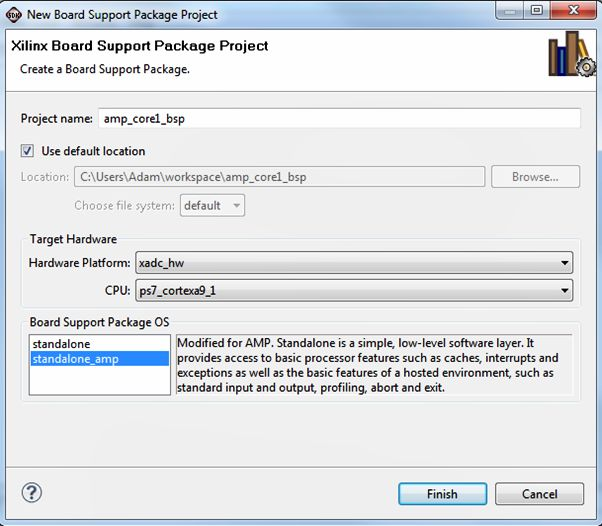

下一步是為 Core1 創(chuàng)建 BSP。我們想使用修改后的獨立操作系統(tǒng) (standalone_amp),它可以防止重新初始化 PS Snoop 控制單元 (SCU)。因此,我們不能像為 Core 0 那樣創(chuàng)建項目時允許自動生成 BSP。請務必在 CPU 選擇選項中選擇 Core 1。

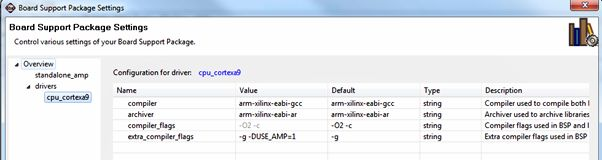

現(xiàn)在我們已經(jīng)為 Core 1 創(chuàng)建了 BSP,我們需要修改 BSP 的設置,然后才能繼續(xù)創(chuàng)建要在 Core 1 上運行的應用程序。這非常簡單,需要添加一個額外的編譯器標志-DUSE_AMP=1 到 BSP 的驅動程序部分的配置:

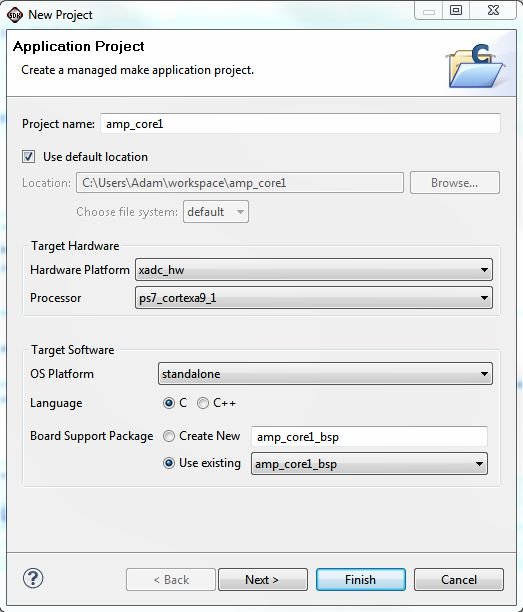

完成后,我們可以自由地為 Core 1 創(chuàng)建應用程序。確保選擇 Core 1 作為處理器并使用我們剛剛創(chuàng)建的 BSP:

同樣,在創(chuàng)建新應用程序后,我們需要再次在 DDR 內(nèi)存中正確定義內(nèi)存位置,Core 1 程序將從該位置執(zhí)行。這是通過編輯 Core 1 應用程序的鏈接器腳本來實現(xiàn)的:

與此應用程序中的第一個內(nèi)核一樣,我們還必須禁用片上內(nèi)存上的緩存,因為我們將在以后的博客中使用此內(nèi)存在兩個處理器之間進行通信. 一旦我們完成了我們的應用程序并構建了項目,我們現(xiàn)在應該擁有以下內(nèi)容:

AMP FSBL ELF

core 0 ELF

core 1 ELF

定義設備配置的位文件。

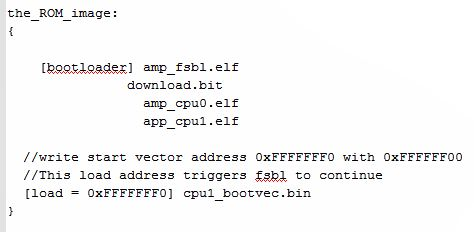

我們現(xiàn)在需要一個 .bin 文件來使 Zynq SoC 從選擇的配置存儲器啟動。我們還需要一個 bif 文件,它定義了用于創(chuàng)建 bin 的文件,并且我們需要定義文件的順序。

我們將使用 XAPP 1079 的 directorydesignworkootgen 下提供的 bat 文件,而不是使用在 SDK 中創(chuàng)建的 Zynq 啟動映像。該目錄包含一個 bif 文件和一個 cpu1_bootvec.bin,該文件用作修改后的 FSBL 的一部分,以阻止它尋找更多要加載的應用程序。

為了生成bin文件,我們將生成的三個ELF文件復制到bootgen目錄并編輯BIF文件,確保bif文件中的elf名稱正確。

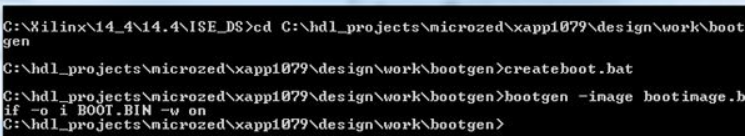

我們現(xiàn)在可以打開 ISE/Vivado 命令提示符,導航到 bootgen 目錄,然后運行 createboot.bat,將創(chuàng)建 boot.bin 文件:

然后可以將該文件下載到 Zynq SoC 上的flash中。引導設備運行兩個內(nèi)核啟動并執(zhí)行各自的程序。

下一節(jié)我們在聊聊一些細節(jié)。

上一節(jié)文章創(chuàng)建了兩個core上啟動并運行簡單的軟件。它的簡單性使我能夠展示如何讓兩個 Zynq SoC 處理器內(nèi)核通過 OCM(片上存儲器)進行通信。但是,兩個核上運行的軟件目前正在做一些簡單的事情,因此我們有一個可以繼續(xù)前進的基線。

Core 0 是主控并控制執(zhí)行 Core 1。它還使用 UART 向終端程序打印消息。

一旦由 Core 0 啟動,Core 1 就會初始化其私有資源并驅動八個 LED 。我們需要使用 Core 1 的私有定時器并通過 GIC 啟用中斷。

這些應用程序沒有任何關聯(lián),也不共享資源。但是,實際的應用程序希望能夠做到這一點。在 Core 0 上運行的應用程序非常簡單。它在 Core 1 上啟動軟件,然后使用 UART 0 在循環(huán)中打印出一條簡單的消息:

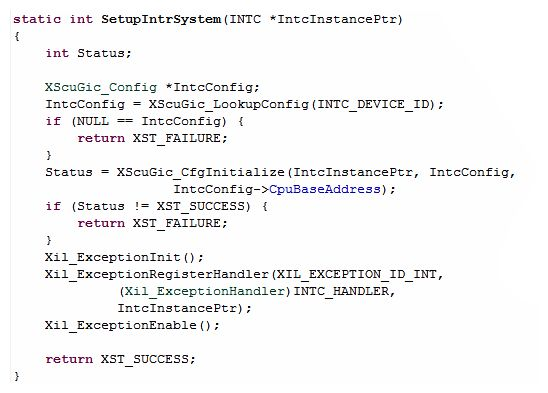

但是,我們計劃使用 Core 1 的中斷控制器,因此我們必須首先使用以下代碼配置 GIC(通用中斷控制器):

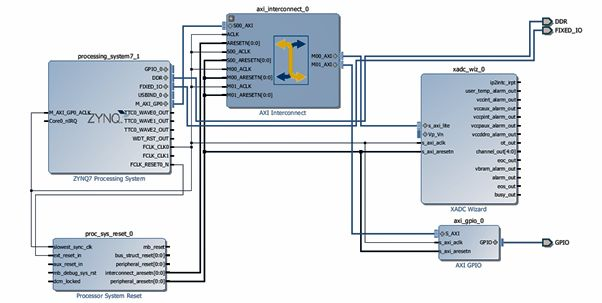

Core 1 代碼必須稍微復雜一些,因為我們使用 Zynq SoC 的 PL(可編程邏輯)端的 GPIO 模塊來驅動 ZYNQ 上的 LED。與賽靈思的所有其他接口一樣,獨立操作系統(tǒng)為此通過#include提供了一組簡單的驅動程序,“xgpio.h” 這個文件與我們之前用來驅動連接到 Zynq SoC 的 PS(處理系統(tǒng))端的 MIO / EMIO GPIO 的 xgpio_ps.h 文件略有不同。然而,在本例中,我想展示如何在 Zynq SoC 的 PL 端使用 GPIO。為了確保我們可以看到 LED 的開關,我們將使用 Core 1 的私有計時器,這與我們過去在核心 0 上使用私有計時器相同。

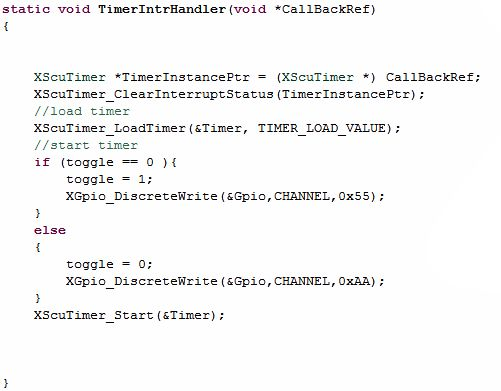

在 Core 1 的程序開始執(zhí)行其主應用程序之前,我們需要禁用片上存儲器 (OCM) 上的緩存,初始化 GPIO,初始化私有定時器,并配置中斷控制器,以便可以使用私有定時器的中斷來切換LED。我們現(xiàn)在可以開始編寫相當簡單的中斷服務例程,在專用定時器結束并重新啟動時切換 LED。這個過程將永遠持續(xù)下去。

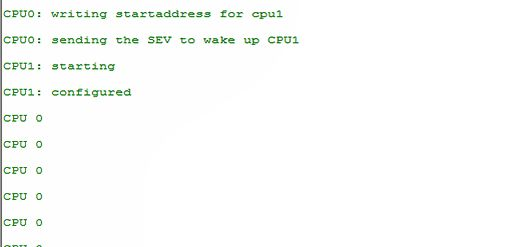

以下是程序執(zhí)行的結果,正如 Core 0 向終端窗口輸出的報告:

代碼地址

https://github.com/suisuisi/zynq_guide/blob/main/core_0_main_part50.c

審核編輯 :李倩

-

處理器

+關注

關注

68文章

19286瀏覽量

229854 -

操作系統(tǒng)

+關注

關注

37文章

6826瀏覽量

123333 -

Amp

+關注

關注

0文章

81瀏覽量

47162

原文標題:ZYNQ從放棄到入門(十二)- AMP — Zynq 上的非對稱多核處理器

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

“雙系統(tǒng)”出爐!瑞芯微RK3562J非對稱AMP:Linux+RTOS/裸機

旋智多核心處理器助力電機控制應用

對稱多處理器的特點是什么

對稱多處理器系統(tǒng)中的進程分配包括

對稱多處理器和非對稱多處理器的區(qū)別

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

TMS320C6474多核數(shù)字信號處理器數(shù)據(jù)表

OPA828運放非對稱電源供電有什么好處嗎?

【本周六-上海】SMP對稱多處理 線下培訓

線下培訓 | 瑞薩電子基于RZ/G2L的OpenAMP混合部署實戰(zhàn)培訓

單相降壓轉換器雙非對稱BG評估板數(shù)據(jù)手冊

單相降壓轉換器雙非對稱AG評估板數(shù)據(jù)手冊

用于多核處理器的可配置多軌PMU TPS650860數(shù)據(jù)表

Zynq上的非對稱多核處理器

Zynq上的非對稱多核處理器

評論