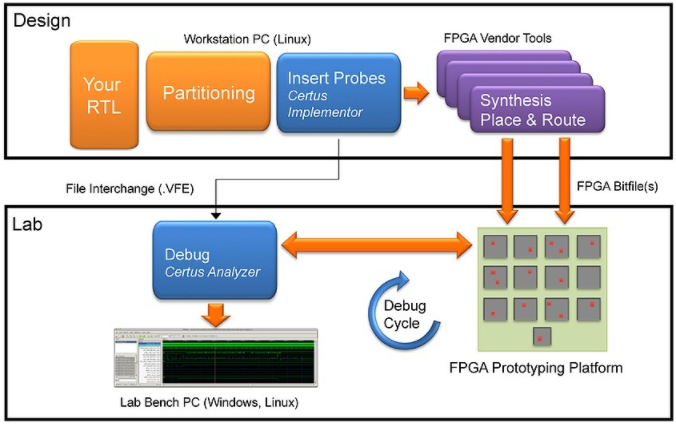

ASIC 和 FPGA 變得非常復(fù)雜,特別是對(duì)于涉及多核的片上系統(tǒng) (SoC) 設(shè)計(jì)。這種復(fù)雜性帶來(lái)了更長(zhǎng)、更繁瑣的調(diào)試和驗(yàn)證周期。不幸的是,當(dāng)出現(xiàn)故障或出錯(cuò)時(shí),在高度集成的設(shè)計(jì)中訪問(wèn)測(cè)試點(diǎn)幾乎是不可能的。除非您想在運(yùn)行多個(gè)原型時(shí)花費(fèi)數(shù)周時(shí)間在黑暗中拍攝隨機(jī)錯(cuò)誤,否則片上儀器不再是可選的;這是一個(gè)重要的必備品。圖 1 顯示了使用片上儀器的調(diào)試過(guò)程概覽。

圖 1:儀器和調(diào)試周期對(duì)于檢測(cè) FPGA 原型中的錯(cuò)誤至關(guān)重要。

雖然有多種方法可以將儀器添加到 FPGA,但使用儀器網(wǎng)絡(luò)的分布式方法正在成為首選方法,因?yàn)樗畲笙薅鹊卦黾恿藵撛谟^察點(diǎn)的數(shù)量,同時(shí)最大限度地減少了硅面積或查找表的使用要求。對(duì)高效調(diào)試同樣重要的是深度跟蹤捕獲,以了解系統(tǒng)的各個(gè)部分如何隨著時(shí)間的推移進(jìn)行交互。最后,設(shè)計(jì)人員必須能夠觀察多個(gè)器件和時(shí)鐘域的交互,包括片上和片外,所有這些都是完全時(shí)間相關(guān)的,以獲得真正的系統(tǒng)級(jí)視角。

總而言之,包括靈活和完整的觀察點(diǎn)訪問(wèn)、深度跟蹤捕獲和系統(tǒng)級(jí)視圖在內(nèi)的創(chuàng)新有可能將 FPGA 和 ASIC 調(diào)試的游戲規(guī)則從漫長(zhǎng)而艱巨的過(guò)程轉(zhuǎn)變?yōu)榭焖俣咝У倪^(guò)程。

調(diào)試挑戰(zhàn)

在回顧實(shí)現(xiàn)嵌入式儀器的不同方法之前,首先了解為什么儀器是必要的會(huì)很有幫助。最大的原因僅僅是每個(gè)系統(tǒng)中不斷增長(zhǎng)的功能。

雖然過(guò)去有很多探測(cè)點(diǎn)(設(shè)備上的外部 I/O)可供選擇,但現(xiàn)在無(wú)法觀察到發(fā)生了什么,因?yàn)樵诖蠖鄶?shù)情況下,關(guān)鍵接口現(xiàn)在都在設(shè)備內(nèi)部。與五年前相比,當(dāng)前一代 FPGA 的并行運(yùn)行功能數(shù)量增加了 100 倍,而外部輸出的數(shù)量卻保持不變。從試圖調(diào)試意外行為的開(kāi)發(fā)人員的角度來(lái)看,現(xiàn)代芯片只不過(guò)是一個(gè)大黑匣子。

似乎這還不夠,雖然模擬器的功能繼續(xù)以線性方式提高,但并行功能的每一次增加都會(huì)增加潛在組合的指數(shù)級(jí)增長(zhǎng)。由于仿真一次運(yùn)行在一種組合上,因此不可能涵蓋硅前仿真運(yùn)行中的所有功能。

由于無(wú)法充分模擬硅前所有可能的排列,導(dǎo)致在設(shè)計(jì)完成之前進(jìn)行基于 FPGA 的原型設(shè)計(jì)。特別是在原型級(jí)別,訪問(wèn)觀察點(diǎn)對(duì)于快速有效地調(diào)試功能問(wèn)題非常有幫助。

另一個(gè)調(diào)試挑戰(zhàn)是硅上嵌入式軟件的出現(xiàn)。越來(lái)越多的 FPGA 和 ASIC 設(shè)計(jì)包括一個(gè)或多個(gè)處理器內(nèi)核。此類系統(tǒng)可能包括軟件、固件、嵌入式處理器、GPU、內(nèi)存控制器和其他高速外圍設(shè)備的復(fù)雜組合。這種增加的功能集成與更快的內(nèi)部時(shí)鐘速度和復(fù)雜的高速 I/O 相結(jié)合,使開(kāi)發(fā)人員比以往任何時(shí)候都更難提供功能齊全且經(jīng)過(guò)充分驗(yàn)證的系統(tǒng)。

片上信號(hào)捕捉

當(dāng)系統(tǒng)涉及多個(gè)芯片和組件時(shí),很容易移動(dòng)邏輯分析儀探頭以查看不同的信號(hào)組合。即使轉(zhuǎn)向片上儀器,靈活地將虛擬邏輯分析儀探頭移動(dòng)到不同信號(hào)點(diǎn)的需求仍然保持不變。由于設(shè)計(jì)人員無(wú)法預(yù)測(cè)給定芯片的每個(gè)變量或潛在應(yīng)用,因此可用的信號(hào)捕獲點(diǎn)越多越好。

傳統(tǒng)的 ASIC 方法使用具有共享選擇信號(hào)的多路復(fù)用器網(wǎng)絡(luò)(每個(gè)多路復(fù)用器級(jí)別一個(gè))并提供 n/m 個(gè)不同的信號(hào)組合,其中 n 是探測(cè)點(diǎn)的數(shù)量,m 是同時(shí)查看的信號(hào)數(shù)量(調(diào)試總線寬度)。這是最嚴(yán)格但最簡(jiǎn)單的選項(xiàng),因?yàn)樗昧撕?jiǎn)單的多路復(fù)用器。為了有效,這種方法需要大量的前期時(shí)間來(lái)創(chuàng)建與每個(gè)可能的調(diào)試場(chǎng)景相對(duì)應(yīng)的信號(hào)組,并且一旦捕獲點(diǎn)起作用,設(shè)計(jì)人員就只能查看同一組中的信號(hào)。此過(guò)程要求高、耗時(shí)且極不可能捕獲所有調(diào)試場(chǎng)景。

另一個(gè)極端是創(chuàng)建一個(gè)完整的交叉開(kāi)關(guān)多路復(fù)用器,以提供完全的信號(hào)靈活性,這需要 m 個(gè)大小為 n:1 的多路復(fù)用器。相對(duì)于面積而言,這可能會(huì)很快變得昂貴,這使得這種方法對(duì)于除了最小的情況之外的所有情況都是不切實(shí)際的。

中間立場(chǎng)是要么增加多路復(fù)用器結(jié)構(gòu)內(nèi)的選擇信號(hào)數(shù)量,要么創(chuàng)建多個(gè)具有不同信號(hào)排序的重復(fù)組。共享選擇多路復(fù)用器和帶有附加選擇信號(hào)的多路復(fù)用器都在許多本土方法中實(shí)現(xiàn)。雖然共享選擇多路復(fù)用方案可以處理常見(jiàn)和預(yù)期的調(diào)試場(chǎng)景,但它們?nèi)匀粵](méi)有達(dá)到理想的完整覆蓋范圍。因此,它們不適合解決意外問(wèn)題,并且通常會(huì)導(dǎo)致實(shí)現(xiàn)效率低下,因?yàn)樾盘?hào)會(huì)重復(fù)連接到多個(gè)多路復(fù)用器。

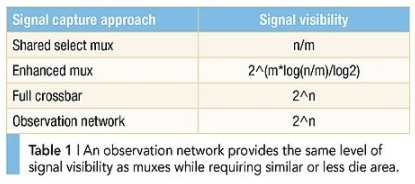

通過(guò)利用多級(jí)無(wú)序網(wǎng)絡(luò)(通常稱為集中器網(wǎng)絡(luò)),可以找到更優(yōu)雅、更高效的解決方案。這種新方法有效地創(chuàng)建了一個(gè)觀測(cè)網(wǎng)絡(luò),并且正在商業(yè)化。使用獨(dú)特的網(wǎng)絡(luò)架構(gòu)和互補(bǔ)的路由算法,觀察網(wǎng)絡(luò)提供了完整交叉開(kāi)關(guān)多路復(fù)用器的信號(hào)靈活性,而在大多數(shù)情況下,只需要共享簡(jiǎn)單多路復(fù)用器的裸片面積。表 1 顯示了使用不同方法計(jì)算的信號(hào)可見(jiàn)度的比較。

表 1:觀察網(wǎng)絡(luò)提供與多路復(fù)用器相同級(jí)別的信號(hào)可見(jiàn)性,同時(shí)需要相似或更少的裸片面積。

通過(guò)觀察網(wǎng)絡(luò),設(shè)計(jì)人員可以使用自動(dòng)化工具以寄存器傳輸語(yǔ)言 (RTL) 實(shí)現(xiàn)片上信號(hào)捕獲探針。在設(shè)計(jì)階段,無(wú)需擔(dān)心不同的信號(hào)組合或排序,因?yàn)槊糠N組合都可用。結(jié)果是一個(gè)隨信號(hào)數(shù)量線性增長(zhǎng)的觀察網(wǎng)絡(luò)。這種方法將確定路由的復(fù)雜性從芯片轉(zhuǎn)移到軟件中。在產(chǎn)生顯著的面積/性能改進(jìn)的同時(shí),觀測(cè)網(wǎng)絡(luò)需要復(fù)雜的算法來(lái)確定路由,因此如果沒(méi)有商業(yè)軟件來(lái)控制信號(hào)選擇,就很難使用它。

在觀察點(diǎn)可見(jiàn)性方面,網(wǎng)絡(luò)方法比簡(jiǎn)單多路復(fù)用器的優(yōu)勢(shì)有多大?以這個(gè)例子為例,其中探測(cè)了 256 個(gè)信號(hào) (n),同時(shí)可見(jiàn) 32 個(gè)信號(hào) (m):

簡(jiǎn)單多路復(fù)用器:信號(hào)組合數(shù)(可見(jiàn)性)= 256/32 = 32

觀測(cè)網(wǎng)絡(luò):信號(hào)組合數(shù)(可見(jiàn)度)= 2^256 = 1.2 x 10^77

相差76個(gè)數(shù)量級(jí)。雖然第一種方法具有高度限制性,但觀察網(wǎng)絡(luò)方法提供了任何可能的信號(hào)組合。以大致相同的成本,觀測(cè)網(wǎng)絡(luò)提供了巨大的優(yōu)勢(shì),其靈活性更高。

最大化捕捉深度

對(duì)于跨越硬件和軟件的調(diào)試挑戰(zhàn),捕獲長(zhǎng)跡線的能力對(duì)于追蹤在數(shù)千或數(shù)百萬(wàn)個(gè)時(shí)鐘周期內(nèi)出現(xiàn)的問(wèn)題至關(guān)重要。在硅后和 FPGA 上,深度捕獲對(duì)于了解整個(gè)系統(tǒng)的工作方式至關(guān)重要,因?yàn)樵S多無(wú)法驗(yàn)證的錯(cuò)誤需要很長(zhǎng)時(shí)間才能出現(xiàn)。此外,大多數(shù)軟件驅(qū)動(dòng)的功能跨越數(shù)十萬(wàn)到數(shù)百萬(wàn)個(gè)時(shí)鐘周期。

傳統(tǒng)的儀器方法在從觀測(cè)探頭接收到的信息時(shí),使用內(nèi)部 RAM 中的一個(gè)條目來(lái)捕獲每個(gè)時(shí)鐘周期捕獲的數(shù)據(jù)。使用這種方法很難或不可能一次捕獲超過(guò)幾千個(gè)時(shí)鐘周期而不會(huì)對(duì)內(nèi)部存儲(chǔ)器資源造成不可接受的壓力。出于這個(gè)原因,現(xiàn)在開(kāi)始使用壓縮技術(shù)來(lái)提高捕獲深度。

然而,大多數(shù)眾所周知的壓縮算法都不太適合跟蹤壓縮,它們是為視覺(jué)媒體和通信應(yīng)用開(kāi)發(fā)的。一起使用多種壓縮技術(shù)的專用跟蹤壓縮層,每一種都專門(mén)針對(duì)常見(jiàn)的跟蹤數(shù)據(jù)模式進(jìn)行定制,現(xiàn)在已經(jīng)上市。對(duì)于大多數(shù)實(shí)際應(yīng)用,這可提供 10-1,000 倍的深度,而不會(huì)損失分辨率。

高效的系統(tǒng)范圍調(diào)試

更高效的 FPGA 和 ASIC 調(diào)試的最后一個(gè)難題是時(shí)間相關(guān)的系統(tǒng)范圍視圖,它跨越多個(gè)并行運(yùn)行的時(shí)鐘域。當(dāng)問(wèn)題需要跨多個(gè)檢測(cè)區(qū)域進(jìn)行關(guān)聯(lián)時(shí),設(shè)計(jì)人員正在考慮獲取單個(gè)軌跡然后手動(dòng)關(guān)聯(lián)事件的耗時(shí)過(guò)程。例如,基于 FPGA 的原型設(shè)計(jì)平臺(tái)上的平均 ASIC 原型由跨四到八個(gè) FPGA 的每個(gè) FPGA 兩到三個(gè)時(shí)鐘域組成。這意味著設(shè)計(jì)人員將需要單獨(dú)調(diào)試 8 到 24 個(gè)時(shí)鐘域。一次跟蹤這 24 個(gè)域中的每一個(gè)并手動(dòng)將結(jié)果拼湊在一起既耗時(shí)又容易出錯(cuò)。

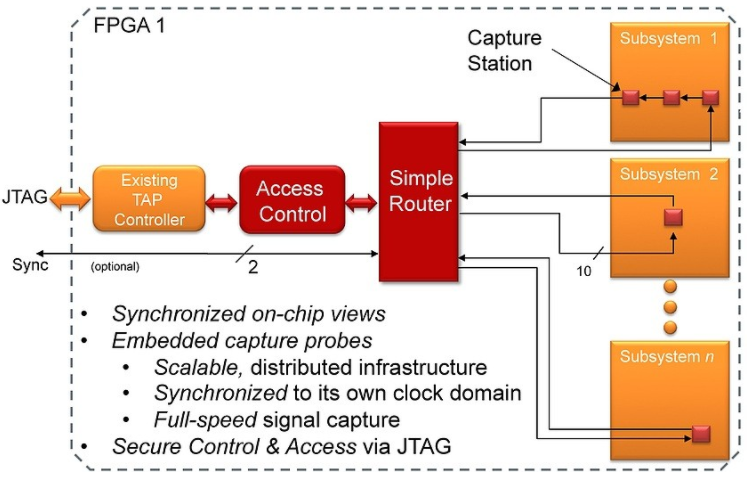

一種更有效的方法是使用邏輯分析儀軟件從在多個(gè)時(shí)鐘域和跨多個(gè)設(shè)備運(yùn)行的獨(dú)立儀器中生成時(shí)間相關(guān)視圖,如圖 2 所示。專用調(diào)試軟件可以從芯片的每個(gè)儀器區(qū)域收集數(shù)據(jù),反轉(zhuǎn)壓縮算法,然后對(duì)齊捕獲的數(shù)據(jù)以生成系統(tǒng)范圍的時(shí)間相關(guān)視圖。這導(dǎo)致單一的跟蹤捕獲和調(diào)試方案,既節(jié)省時(shí)間又提供許多功能單元和時(shí)鐘域的同時(shí)硬件調(diào)試。此過(guò)程通常會(huì)揭示在構(gòu)建設(shè)備時(shí)從未考慮過(guò)的緊急系統(tǒng)行為。

圖 2:時(shí)間相關(guān)視圖加速系統(tǒng)級(jí)調(diào)試。

創(chuàng)新應(yīng)對(duì)意外

隨著復(fù)雜性的增加和對(duì)探測(cè)點(diǎn)的訪問(wèn)受限,ASIC 和 FPGA 驗(yàn)證和調(diào)試變得乏味且耗時(shí)。隨著越來(lái)越多的功能集成到每個(gè)芯片中,對(duì)探測(cè)點(diǎn)的物理訪問(wèn)變得不可能。接下來(lái)的挑戰(zhàn)是整合足夠的片上觀察點(diǎn),不僅可以處理預(yù)期的調(diào)試場(chǎng)景,還可以處理意外的調(diào)試場(chǎng)景。

即使是最復(fù)雜的設(shè)計(jì),也能更快、更有效地驗(yàn)證和調(diào)試的一項(xiàng)關(guān)鍵創(chuàng)新是觀察網(wǎng)絡(luò)。與觀察信號(hào)的傳統(tǒng)共享選擇多路復(fù)用器方法相比,觀察網(wǎng)絡(luò)可提供更多具有相似芯片面積要求的信號(hào)組合。

支持更高效調(diào)試方案的其他創(chuàng)新包括使用高級(jí)壓縮算法來(lái)提高片上存儲(chǔ)器捕獲深度,以及邏輯分析儀軟件的出現(xiàn),該軟件可以生成跨越多個(gè)設(shè)備和片外儀器的時(shí)間相關(guān)的系統(tǒng)范圍視圖。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1630文章

21777瀏覽量

604717 -

asic

+關(guān)注

關(guān)注

34文章

1205瀏覽量

120600 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7521瀏覽量

164092

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA與ASIC的區(qū)別 FPGA性能優(yōu)化技巧

ASIC集成電路與FPGA的區(qū)別

FPGA和ASIC在大模型推理加速中的應(yīng)用

FPGA與ASIC的優(yōu)缺點(diǎn)比較

淺談邏輯分析儀的技術(shù)原理和應(yīng)用領(lǐng)域

將ASIC IP核移植到FPGA上——更新概念并推動(dòng)改變以完成充滿挑戰(zhàn)的任務(wù)!

通過(guò)片上儀器和邏輯分析輕松進(jìn)行FPGA和ASIC調(diào)試

通過(guò)片上儀器和邏輯分析輕松進(jìn)行FPGA和ASIC調(diào)試

評(píng)論