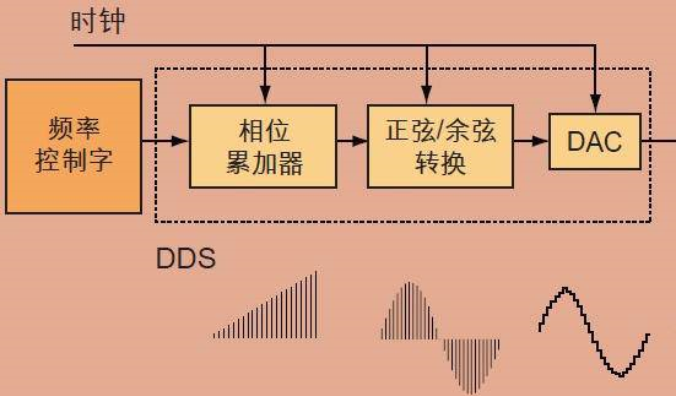

一、功能描述

本工程實現DDS直接數字式頻率合成器,利用正弦波相位線性增加的特點,產生正弦波和余弦波。本工程主要由3部分組成:相位累加器,相位幅度轉換,數模轉換器DAC(FPGA外部實現)。其中,相位累加器的高10比特用于ROM的索引地址。

二、波形調制說明

模塊將一個正弦波采樣1024個點,然后保存到內部一個8比特、1024深度的ROM當中,通過改變時序和相位控制字,即可生成不同頻率的波形。 生成波形的公式是: FO=TCLK*FCW/655360 上面公式中,TCLK是指本模塊的工作時間,FCW是相位控制字,FO即是生成的信號頻率。

相位控制字FCW可以改變每次步進數M。如果FCW=128,則模塊內部累加器每次加128,則經過M=16’hffff/128=512個時鐘,就可以循環一個周期,也就是512個時鐘完成一個正弦波輸出。假如FCW為256,則代表1024/4=128個時鐘周期就輸出一個正弦波。

三、應用舉例

設定是FCW=128,CLK=50M的時鐘頻率,由公式計算得出F0=10KHZ。實際測量出一個波形時間為10332000ps,最終波形的頻率為10KHZ。 如果是FCW=128,CLK=5M的時鐘頻率,由公式計算得出F0=1KHZ。輸出實際測量一個波形時間為51898054ps,最終波形的頻率為1KHZ。

如果是FCW=128,CLK=100M的時鐘頻率,由公式計算得出F0=0.2MHZ。輸出實際測量一個波形時間為5167188ps,最終波形的頻率為0.2MHZ。 以此類推,通過對頻率控制字的改變來控制波形頻率。

四、平臺效果圖

五、實現過程

首先根據所需要的功能,工程頂層的輸入輸出信號列表。

我們可以把工程劃分成三個模塊,分別是Sin相位轉波形模塊和Cos相位轉波形模塊和相位累加器模塊。

1. 相位累加器模塊

本模塊根據設置好的相位控制字FCW來進行相位累加,以此控制波形的相位,sum 《= sum + fcw;對相位不斷累加,然后將累加的sum數據實時傳到另外兩個模塊中去 以此本模塊實現了相位累加,并將數據傳輸給其它模塊的功能。

本模塊信號列表如下:

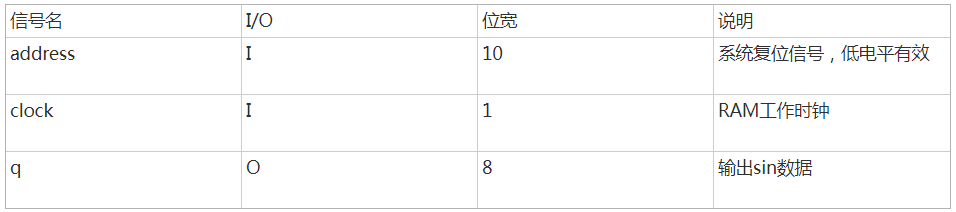

2.Sin相位轉波形模塊

本模塊實際上是一個RAM,事先將相位和相應相位上的幅值關系寫入,然后通過從相位累加模塊傳來的相位累加數據sum進行查表,得到對應的幅值,以此當一個sin波的相位全部轉換一遍后即可得到一個完整的sin波形。

信號列表如下:

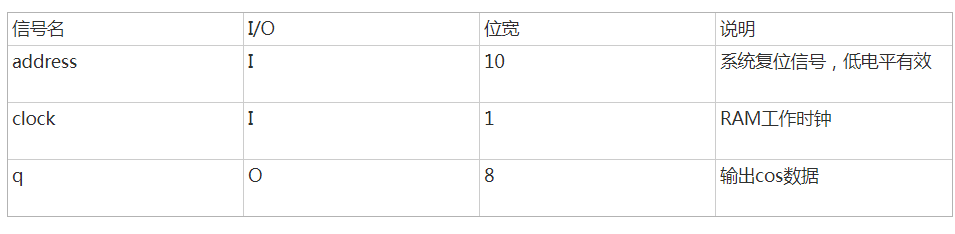

3. Cos相位轉波形模塊

本模塊實際上是一個RAM,事先將相位和相應相位上的幅值關系寫入,然后通過從相位累加模塊傳來的相位累加數據sum進行查表,得到對應的幅值,以此當一個cos波的相位全部轉換一遍后即可得到一個完整的cos波形。

信號列表如下:

-

數模轉換器

+關注

關注

14文章

1018瀏覽量

83278 -

累加器

+關注

關注

0文章

50瀏覽量

9474

發布評論請先 登錄

相關推薦

DDS直接數字式頻率合成器的正弦波和余弦波

DDS直接數字式頻率合成器的正弦波和余弦波

評論