用于精心管理電源的片上系統 (SoC) 的新 DSP 內核、具有正交頻分多址 (OFDMA) 的電力線通信 (PLC) 芯片高噪聲智能電網環境,以及電子設計自動化 (EDA) 設計流程的獨特方法,可為 SoC 設計人員帶來巨大回報。

DSP 性能與節能

DSP 對便攜式多媒體設備至關重要,但是在保持電源管理的同時實現高性能以及在電池供電操作的預期范圍內是兩件事并沒有很好地結合在一起。找到一種在控制功耗的同時提供更高 DSP 性能的方法創造了一個有趣的突破。

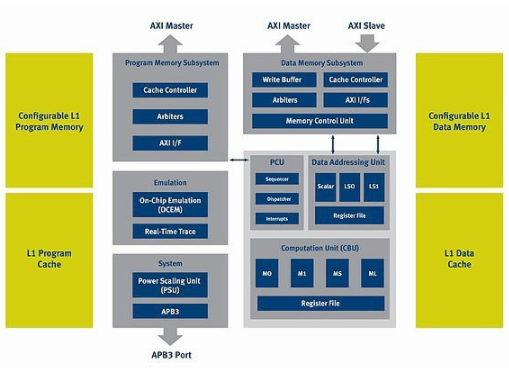

圖 1: CEVA-X1643

CEVA 最新的 DSP 內核 CEVA-X1643 提供 1 GHz 的處理速度和一個集成的功率調節單元 (PSU),可處理動態和泄漏功率的高級電源管理。PSU 控制內核中的多個時鐘源和電源域,以及從完全開啟到調試旁路到內存保留到完全斷電的多種操作模式。AXI 總線接口還提供低功耗功能,例如在沒有流量運行時關閉。

CEVA

www.ceva.com

www.embedded-computing.com/p46219

電力線通信采用 OFDMA

多年來,國防和寬帶通信網絡一直使用頻率捷變無線電來避免干擾并提供強大的通信。智能電網的一個恒定特征是噪聲——大負載快速切換并且經常在電力線上產生大量電氣噪聲。在這個最新的創新中結合這兩個想法。

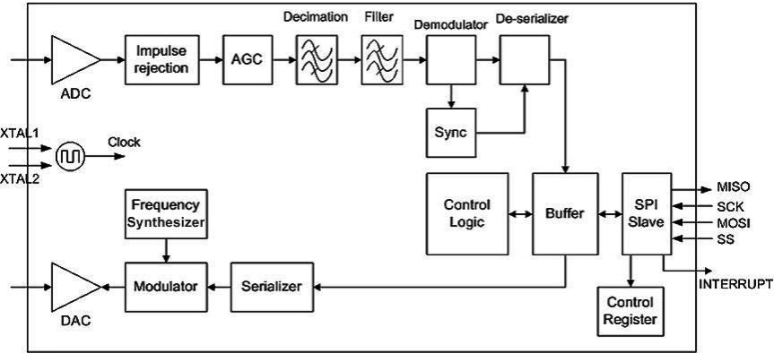

圖 2: Semitech SM2200

Semitech 的 SM2200 PLC 芯片將 OFDMA 收發器用于管理電力線數據的任務,例如用于智能電網的數據。它適應噪聲環境,選擇最有效的運行頻率,并使用多接入方案來幫助同時與多個節點通信。SM2200 可以很容易地與微控制器結合來構建數據鏈路。

Semitech Semiconductor

www.semitechsemi.com

www.embedded-computing.com/p46220

EDA 設計流程使 SoC 斷電

今年設計自動化大會的最大主題之一是低功耗設計流程。隨著速度越來越快和幾何尺寸越來越小,SoC 中的動態和泄漏功率成為更大的問題,這已經不是什么新聞了。在設計流程中優化功率可能是一項耗時的手工工作,可能會引入更多錯誤并減慢整個過程。

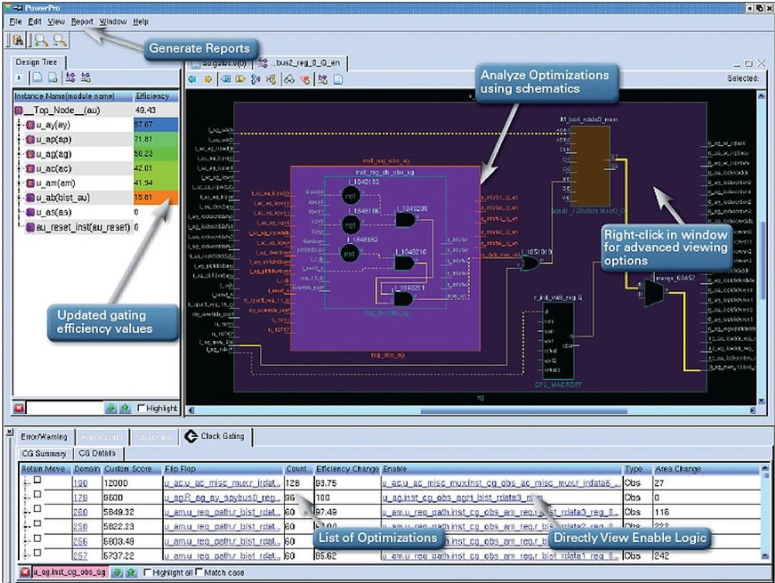

圖 3: Calypto PowerPro MG

Calypto Design Systems、Virage Logic 和半導體技術學術研究中心 (STARC) 共同承擔 SoC 電源的主要組成部分:片上存儲器。Calypto 的 PowerPro MG 使內存門控邏輯與 Virage Logics 的 SiWare 內存編譯器中的淺睡眠、深度睡眠和關機等內存模式協同工作。內存編譯器自動生成 PowerPro MG 模型,STARC 已在無縫、低功耗 EDA 設計流程中實現了該模型。合作公司聲稱通過該方法可降低 50% 的動態功耗和 40% 的泄漏功耗,這對于 SoC 設計人員來說是一個好消息。

審核編輯:郭婷

-

存儲器

+關注

關注

38文章

7522瀏覽量

164104 -

soc

+關注

關注

38文章

4192瀏覽量

218658 -

編譯器

+關注

關注

1文章

1640瀏覽量

49210

發布評論請先 登錄

相關推薦

基于自適應優化的高速交叉矩陣設計

PHY6236—藍牙低功耗 (BLE)/私有 2.4GHz 系統芯片

PHY6235—藍牙低功耗和專有2.4G應用的系統級芯片(SoC)

低功耗SOC芯片的優勢

步進電機如何自適應控制?步進電機如何細分驅動控制?

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

柵極驅動芯片選型低功耗原因

如何在自己的固件中增加wifi自適應性相關功能,以通過wifi自適應認證測試?

LMH1219具有集成時鐘恢復器的低功耗12G UHD自適應電纜均衡器數據表

SN65HVDA54x-Q1 SN65HVDA54x-5-Q1 具有I/O電平自適應和低功耗模式電源優化的5V Can收發器數據表

OTP低功耗語音芯片的工作原理與產品特性

低功耗 高性能M0芯片亮點(1~3): 低功耗 寬電壓 PWM (無須擔心耗電問題!)

什么是自適應光學?自適應光學原理與方法的發展

【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之 Versal 介紹(2)

自適應PLC芯片和低功耗EDA設計流程

自適應PLC芯片和低功耗EDA設計流程

評論