不斷增加的數據速率與有限的頻譜相結合,需要 LDPC FEC 等技術來幫助跟上步伐。

在過去的幾年里,無線行業對使用低密度奇偶校驗 (LDPC) 碼的前向糾錯 (FEC) 的興趣激增。在每秒千兆位傳輸速率和信道容量物理限制的時代,每一個有用的信息比特都有自己的價值。LDPC FEC 已被證明是一種有效的系統組件,可以以非常高的成本提高傳輸魯棒性。在這種情況下,電信網絡的每個元素都必須高效設計,這將具體適用于無線數據傳輸,它具有與頻譜資源的可用性相關的限制。

理論最大信道容量遵循 Claude Shannon 早在 1948 年引入的著名定理。根據他的定理,存在使噪聲信道中的操作能夠任意接近理論信道容量的代碼。從那以后,這個公式引起了很多人的興趣和圍繞搜索能夠在香農容量附近進行操作的代碼的實際工作。

有趣的是,1963 年 Robert G. Gallager 在他的開創性博士論文 Low Density Parity Check Codes 中已經提出了這種高效的代碼。大約在這個時候,引入了 Reed-Solomon 和 Bose-Chaudhuri-Hocquenghem (BCH) 碼,早在 Turbo 碼出現之前。然而,LDPC FEC通過使用碼字比特估計的多次迭代以及相當大的矩陣需要很高的計算復雜度,因此在提出這些代碼時,他們沒有找到任何實際的實現。

LDPC 碼是線性的,具有稀疏奇偶校驗矩陣。這些屬于設計用于在奇偶校驗矩陣的行和列中包含低密度“1”的塊代碼類。使用稀疏分布的奇偶校驗架構背后的意圖是應用概率獨立的 XOR 計算,奇偶校驗值的估計值在奇偶校驗矩陣的每一行中聚合,并且每次后續迭代都會改進估計值。在估計收斂并糾正所有錯誤之前可能需要數十次迭代。然而,確切的迭代次數由代碼設計者根據特定代碼需要在其中運行的系統的應用程序和規范來確定。在確定滿足特定系統規范所需的最小迭代次數之前,可以進行許多權衡。現代 LDPC FEC 使用軟判決算法,進一步提高解碼器增益。

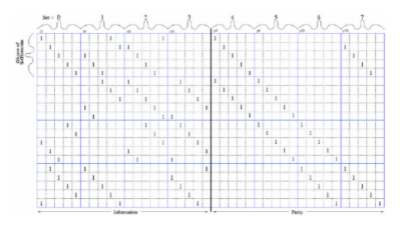

隨著更大的塊長度N,糾錯能力的置信度增加。但是,它通過增加奇偶校驗矩陣的大小來增加計算復雜性,從而增加估計每個位所需的計算次數(圖 1)。

圖 1:示例 LDPC 奇偶校驗矩陣。

使用大塊和迭代的另一個問題是延遲增加,因為這些計算是逐塊進行的。由于處理和內存資源有限,這將成為在延遲敏感的應用程序(例如語音通信)中使用 LDPC 碼的關鍵約束。另一個例子是 3GPP-LTE 中的混合自動重復請求 (HARQ) 傳播時間要求,它將往返時間限制為 5 ms,而基帶用戶設備處理引入的延遲將消耗該延遲預算的很大一部分。隨著新的 Cloud RAN 架構和無線被考慮用于前傳,這種延遲預算對于規劃無線調制解調器中使用的 FEC 的設計限制變得至關重要,這通常是整個信號處理鏈中最大的延遲貢獻者。

在 2003 年引入 DVB-S2 衛星廣播標準后,在無線通信中采用 LDPC FEC 的實際商業突破發生了。在之前的 DVB 標準中使用的卷積編碼上,使用 LDPC FEC 將閾值增益提高了大約 3dB,并能夠遷移到更高的頻譜效率。七到八年后,LDPC FEC 開始進入無線回程鏈路,隨著 3G 的出現以及隨后的數據流量爆炸和回程瓶頸挑戰,更高的頻譜效率已成為重要的設計目標。現在,它已成為回程無線鏈路設計的事實標準。

由于與 50 年前相同的限制,強大的 LDPC FEC 碼的設計仍然是一項復雜的任務。自然地,可以實現這些代碼的硬件平臺在此期間實現了巨大的飛躍,即使計算能力大大增加,設計也必須具有功率和成本效益,并與大多數其他功能模塊集成在一起。負責溝通。此外,帶寬需求已顯著增加,現在我們需要能夠處理更高的吞吐量。因此,在設計 LDPC 碼時,需要在確定架構時在無數不同的優化練習之間取得平衡,以保持低延遲、低功耗和低成本的良好性能。

與 DSP 不同,FPGA 為 LDPC 編碼器和解碼器所需的計算類型提供了高度并行的結構。該 IP 具有高度可配置性,允許用戶選擇不同級別的并行度來優化解碼器大小,還可以定制解決方案以支持各種通道帶寬。LDPC FEC 具有可擴展性,支持窄微波波段(3.5 至 112 MHz)到真正寬的毫米波段(250 Hz 至 1,000 MHz)。所謂的多層編碼技術簡化了 LDPC FEC 架構,并保持代碼庫的大小和功耗在低端 FPGA 平臺上可行。

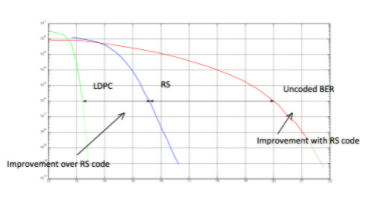

Xilinx 的 FEC 代碼中使用的特殊 X 解碼算法已經以較少的迭代次數實現了顯著的 SNR 增益,從而導致更好的解碼器延遲。圖 2 展示了 LDPC FEC 碼與 RS FEC 相比的示例性能。平均而言,根據碼率、碼字長度和迭代次數,相對于 RS 碼有 2 到 4 dB 的改進。下面的示例在高數據速率下使用低編碼開銷。

圖 2:基于 RS 和 LDPC FEC 的 BER 與 SRN 性能。

FEC 通常與同一 FPGA 上的無線調制解調器和數據包處理模塊一起實現,以從完整的基帶集成中受益。通常,由于與平臺無關的設計實踐和傳統的 ASIC 轉換,這些設計往往太大而無法從采用價格合理的 FPGA 中受益。Xilinx 的 1+Gbps LDPC FEC 編碼器和解碼器 SmartCORE IP 解決了這一設計挑戰,支持將 FEC IP 與調制解調器和數據包處理一起使用。

LDPC 的研究將繼續進行,我們可以期待這些代碼在不同的通信場景中會發現更多的適用性。我們很可能會看到在新一代 CMTS 和數據中心系統中采用低密度奇偶校驗技術。但它們可能會出現在未來的 5G 標準中,其中正在審查更高頻率和單載波波形的使用。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21767瀏覽量

604615 -

解碼器

+關注

關注

9文章

1144瀏覽量

40823 -

asic

+關注

關注

34文章

1205瀏覽量

120600

發布評論請先 登錄

相關推薦

乘用電動車無線充電再突破,無線充電正在成為行業趨勢技術

無線充芯片-手機無線充電芯片-無線充電芯片開發定制

盤點!全息廣告機電機驅動方案,BLDC技術為何成為首選?

6種主流無線通信技術:藍牙,WiFi,2.4G,Zigbee,LoRa和NB-IoT

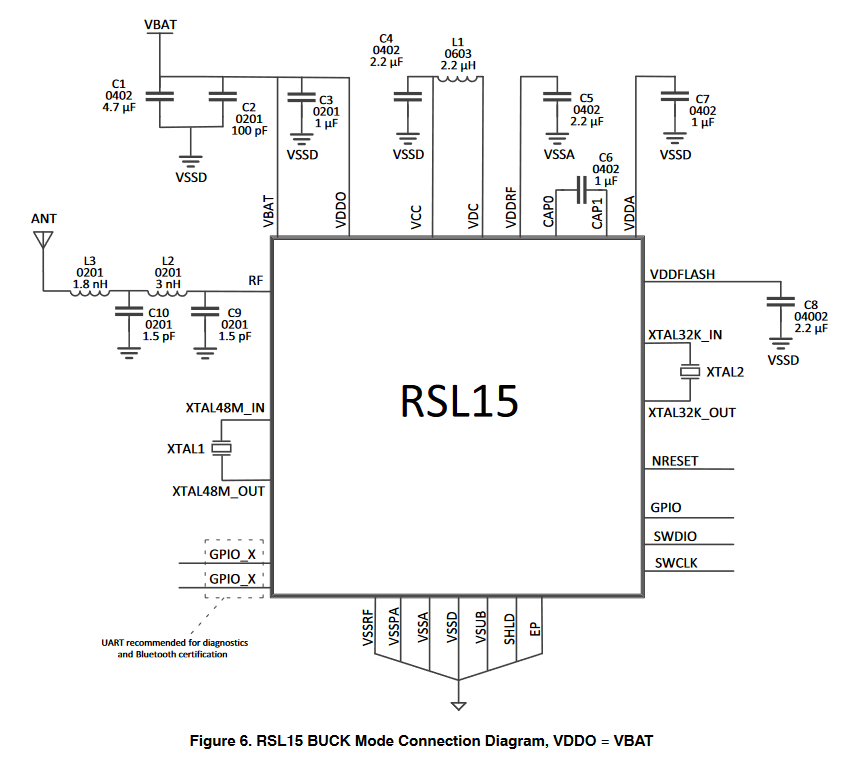

安森美NCV-RSL15藍牙5.2無線MCU在汽車中的應用

亞馬遜云科技成為店匠科技的首選云服務供應商

藍牙Mesh模塊組網時無線回程影響速率嗎?

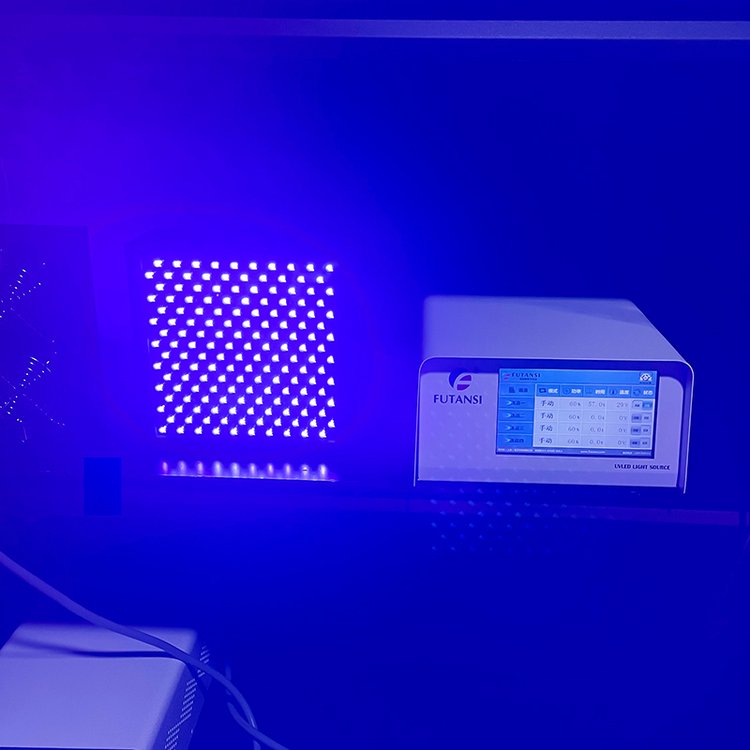

揭秘365nm固化燈:為何它成為工業固化的首選?

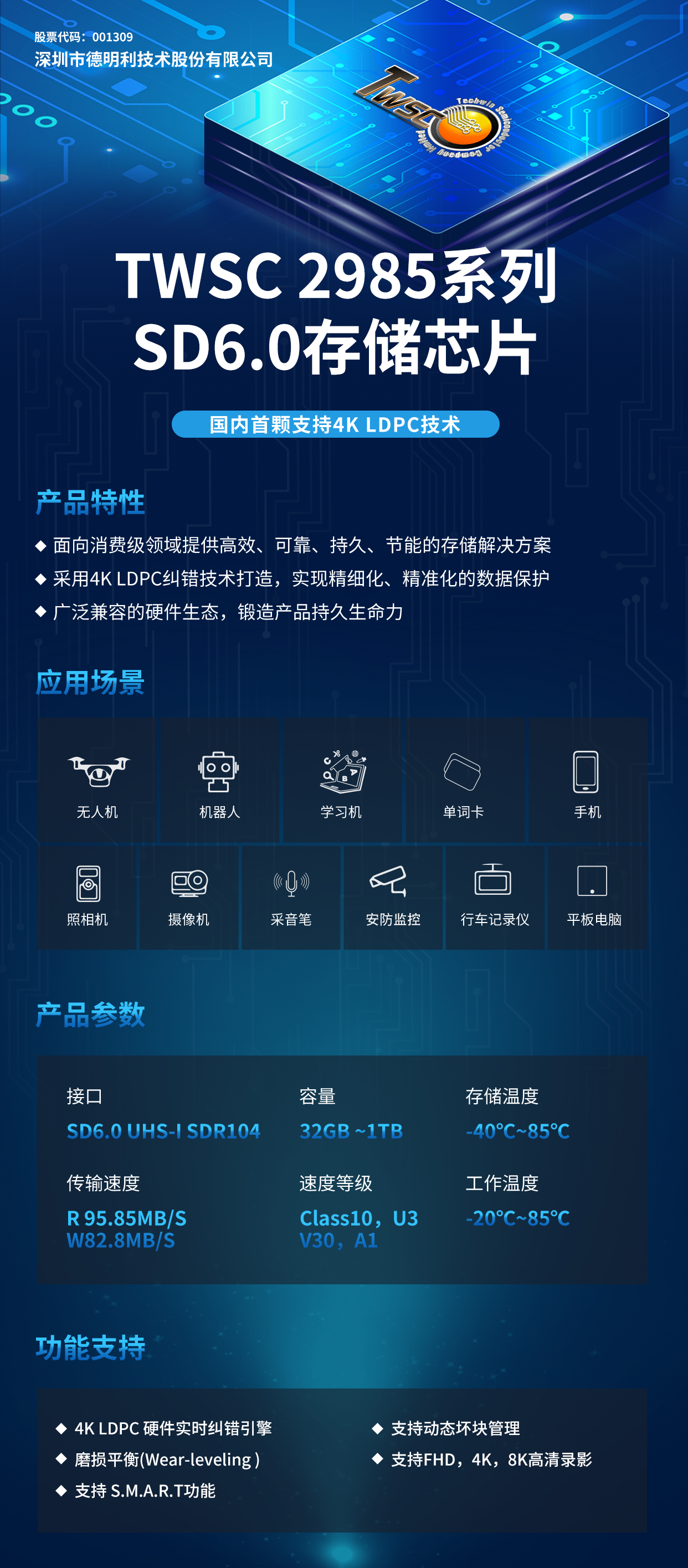

國內首顆,精準糾錯!德明利TWSC2985系列:支持4K LDPC技術的存儲芯片

LDPC FEC成為無線回程的首選技術

LDPC FEC成為無線回程的首選技術

評論