博主將 I2C spec 文章總結為一篇,目錄如下

I2CIntroduction

I2CArchitecture

I2CTransfer

I2CSynchronizationAndArbitration

I2CHs-mode

1、I2C Introduction

1、I2C 歷史

- I2C:Inter-Integrated Circuit,集成電路總線。

- I2C 是 Philips 公司在 1982 年為主機板、嵌入式系統(短距)設計的一種簡單、雙向二線制同步串行總線。

- Philips 半導體事業部就是現在的 NXP。

- I2C 的專利在 2006 年 11 月 1 日已到期,大家可以免費使用。

- Intel 1995 年推出的 I2C 兼容總線(System Managerment Bus),即 SMBus 或 SMB

- 最新版本 I2C spec v.6 于 2014.04.04 推出。

2、I2C 的未來

- MIPI 協會在 2014 年左右定稿了 I3C (improved Inter Integrated Circuit)規范,I3C 在 I2C 的規格上建立了功能超集,支持高傳輸速率模式。

- 當前不論是 Soc 廠商,還是 device 廠商,都已經開始或正在向 I3C 過度。

- I3C spec 有 2016 版本、2018 版本,最新的是 2021 版本(446頁)。

3、I2C 的速度

通信速度如下:

? Bidirectional bus:

- Standard-mode (Sm), 100 kbit/s

- Fast-mode (Fm), 400 kbit/s,用在 sensor、carema、touch 等。

- Fast-mode Plus (Fm+),1 Mbit/s

- High-speed mode (Hs-mode),3.4 Mbit/s,用在 NFC、buck&boost 等

? Unidirectional bus:

- Ultra Fast-mode (UFm),5 Mbit/s

速度由 SCL 決定,不同模式對上升沿的要求不一樣,上升沿斜率受上拉電阻和等效電容影響。

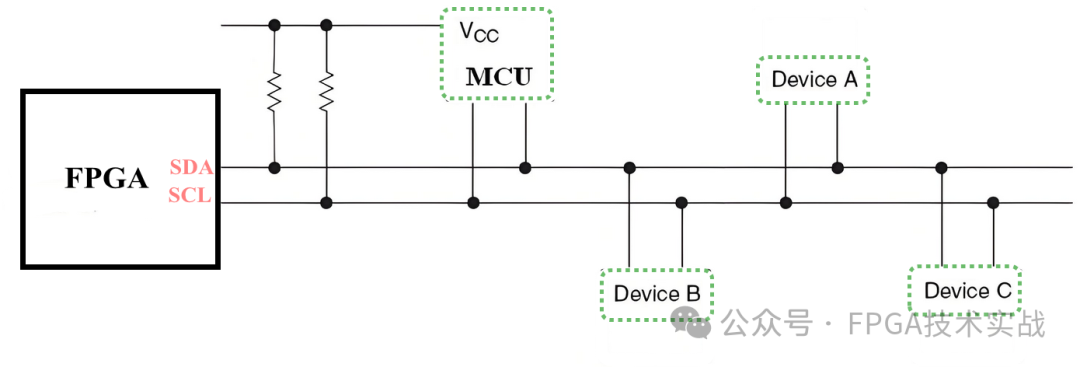

4、I2C 是一種多主從架構總線

- I2C 的讀寫均由 master 端發起。

- I2C 通信的每一個 byte(8bits)都需要 slaver 端的回應 ACK/NACK 作為回應。

- 多 master 端需要引入仲裁機制。

- slaver 端通過設備地址區分,有 7bits 和 10 bits 等地址,還有一種 8bits 地址,實際上是 7bits + 讀寫位。【其中7位地址 = 種類型號(4bit)+ 尋址碼(3bit)】

5、I2C 總線能掛多少設備?

7-bit address :2 的 7 次方,能掛 128 個設備。

10-bit address :2 的 10 次方,能掛 1024 個設備。

但是 I2C 協議規定,總線上的電容不可以超過 400pF。管腳都是有輸入電容的,PCB上也會有寄生電容,所以會有一個限制。實際設計中經驗值大概是不超過 8 個器件。

總線之所以規定電容大小,是因為 I2C 使用的 GPIO 一般為開漏結構,要求外部有電阻上拉,電阻和總線電容產生了一個 RC 延時效應,電容越大信號的邊沿就越緩,有可能帶來信號質量風險(方波變三角波)。傳輸速度越快,信號的窗口就越小,上升沿下降沿時間要求更短更陡峭,所以 RC 乘積必須更小。(可以理解為輸出高電平就是給電容充電,電容越大,充電越慢)

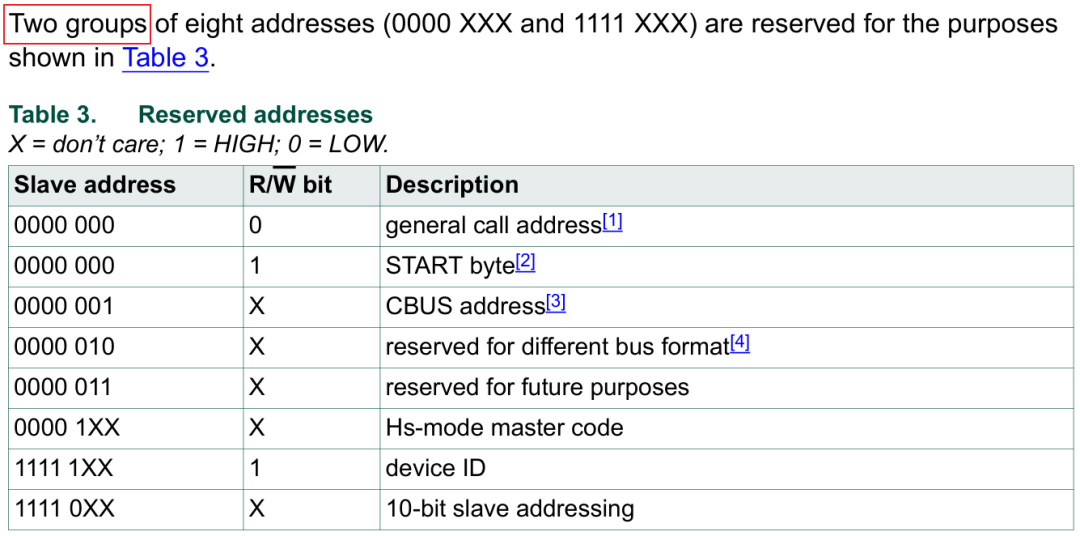

注意,要把 spec 規定的預留設備地址去除,保留地址如下:

note:寫的是 two groups,而不僅僅是八個,0000 XXX 和 1111 XXX 系列地址都是保留的。

note:注意 1111 1XXX 是 Hs-mode master code,1111 0XXX 是 10-bit slave addressing,博主后面會講。

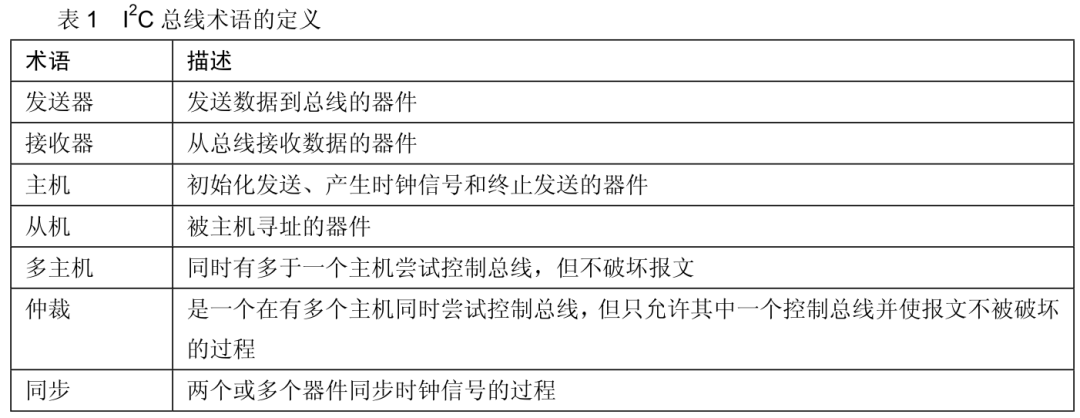

6、定義術語

2、I2C Architecture

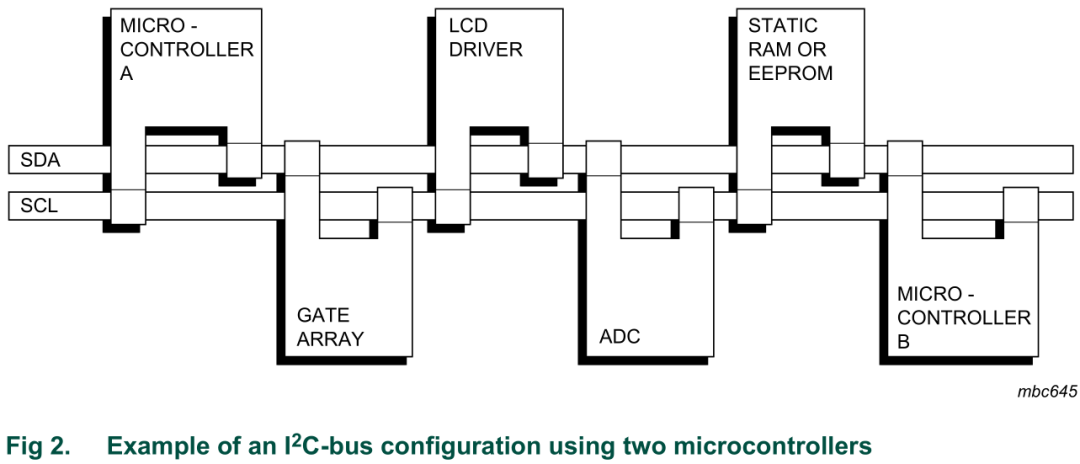

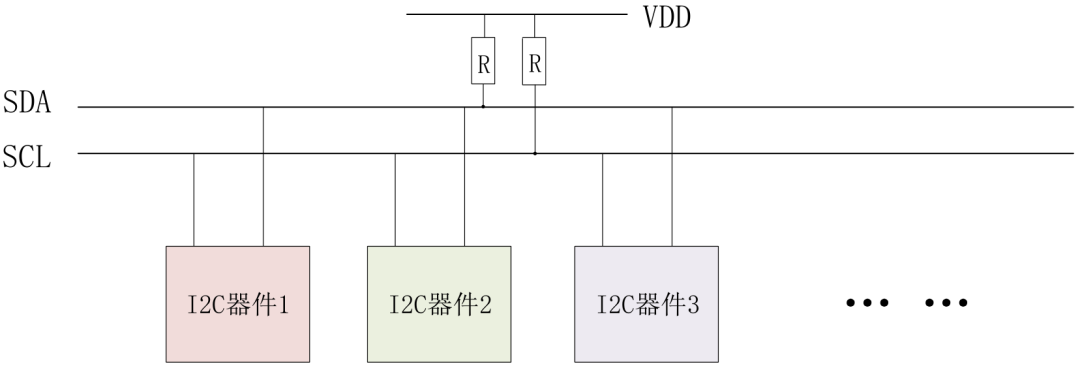

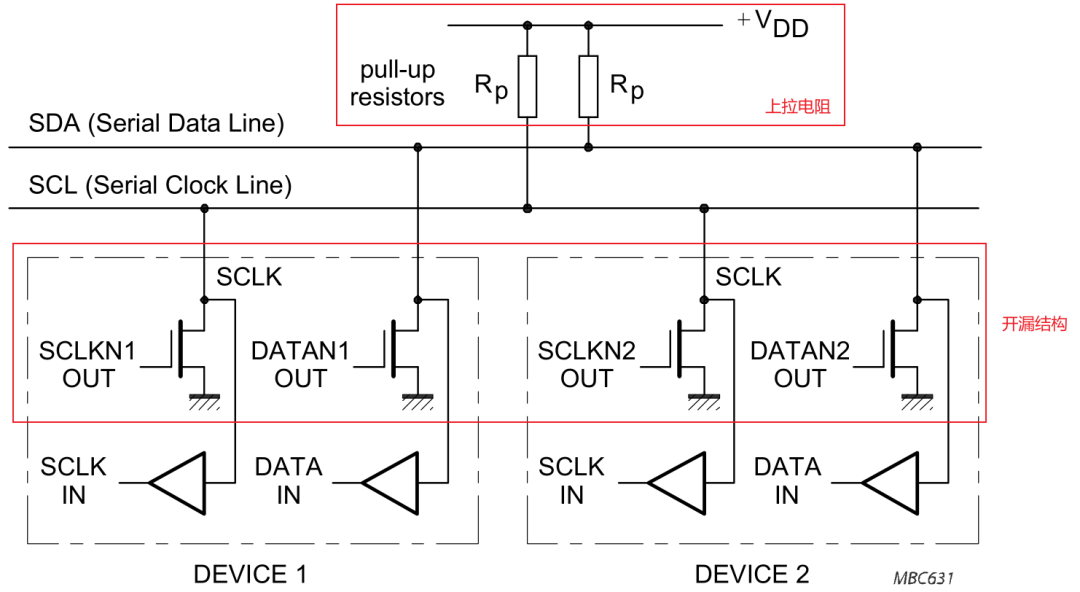

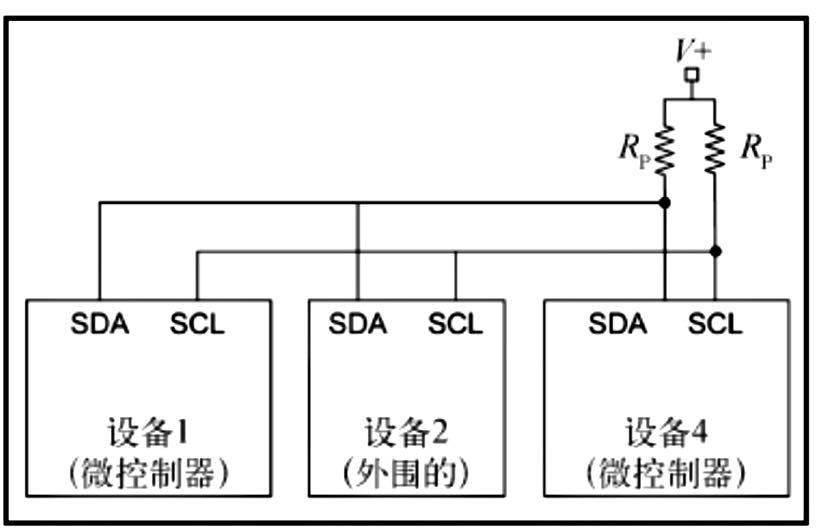

I2C 采用的 GPIO 一般為開漏模式,支持線與功能,但是開漏模式無法輸出高電平,所以需要外部上拉。Vdd 可以采用 5V、3.3V、1.8V 等,電源電壓不同,上拉電阻阻值也不同。

一般認為 I2C 總線上,低于 0.3Vdd 為低電平,高于 0.7Vdd 為高電平。

I2C 協議中每個掛到總線上的設備都有獨一無二的靜態設備地址。

空閑時,I2C 總線上兩根線都是高電平,因為有上拉電阻。

1、推挽結構和開漏結構

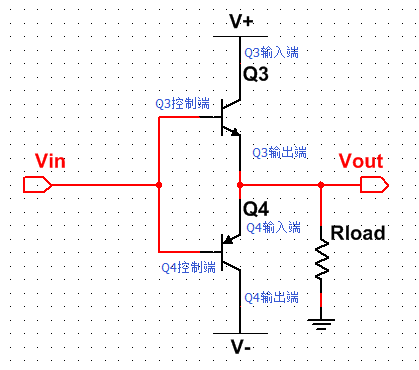

1、推挽結構:使用兩個三極管或 MOSFET,以推挽方式存在于電路中。電路工作時,兩只對稱的開關管每次只有一個導通,所以導通損耗小、效率高。既可以向負載灌電流,也可以從負載抽取電流。推拉式輸出級既提高電路的負載能力,又提高開關速度。

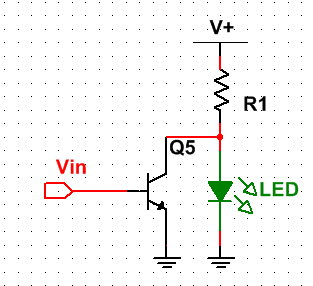

圖中上面是 NPN 型三極管,下面是 PNP 型三極管。分別有以下兩種情況:

輸出高電平:向負載灌電流。

輸出低電平:從負載拉電流。

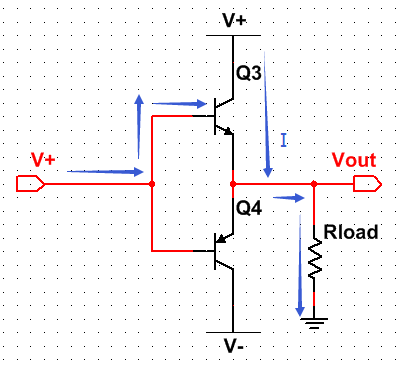

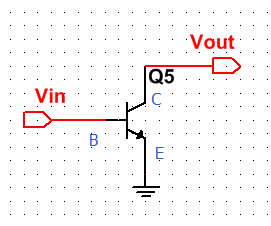

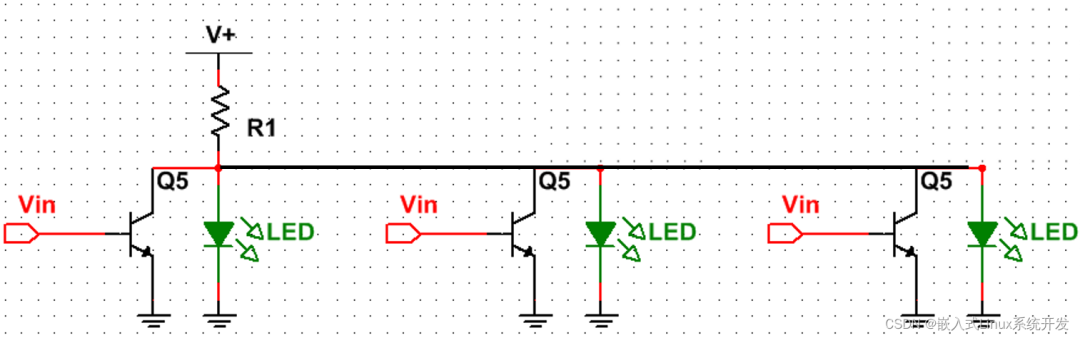

2、開漏結構(OD):對比推挽結構,開漏結構只有一個三極管或者MOS管。

之所以叫開漏,是因為 MOS 管分為三極:源極、柵極、漏極。漏極開路輸出,所以叫開漏;如果是三極管:基極、集電極、發射極,集電極開路,所以叫開集輸出(OC)。

開集輸出,NPN 三極管:

Vin 高電平,三極管導通,對外輸出低電平,外部被直接拉到低。

Vin 低電平,集電極(C)開路,輸出電平狀態由外部決定。

以上分析均采用三極管,MOS 管類似。

因此,推挽結構可以輸出高低電平。開漏輸出只能輸出低電平,高電平由外部電路決定。

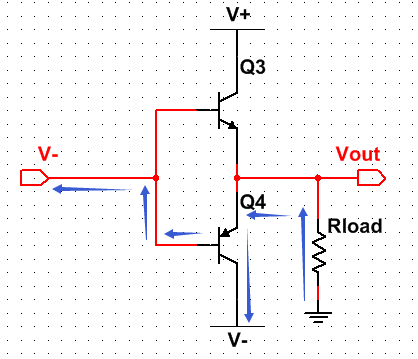

2、線與功能

線與:所有 GPIO 輸出高就是高,只要有一個輸出低,整條線上面的都是低,這就是“與”的意思。

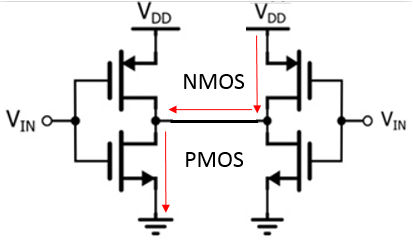

1、推挽結構下,兩個 GPIO 口連接到一根線上,假如左邊的 PMOS 導通,右邊的 NMOS 導通,Vdd 就會通過兩個 MOS 管直接接地,由于 MOS 管導通電阻不大,會導致電流很大,直接損壞這兩個 GPIO口,因此,推挽輸出不支持線與。

note:實際上并不一定是上面 NMOS 下面 PMOS,只要上下兩個管子采用不同類型,即可保證同一時刻只有一個管子導通,即可分別輸出高低電平。

2、開漏結構:假如很多 GPIO 是開漏結構,接到了一根線,如下圖。開漏結構輸出的高電平靠外部上拉,假如有一個 GPIO 接地,那么電流會通過上拉電阻流進地,因為有上拉電阻的存在,所以電流不大,不會損壞 GPIO 口。

線與,是 I2C 協議的基礎!

小節

| mode | open-drain | push-pull |

|---|---|---|

| speed | slower | fsater |

| power | higher | lower |

| slave clock stretching | yes | not supported |

power 功耗上,開漏因為上拉電阻的存在,每次高低電平變換都會消耗能量,因此功耗高。

clock stretching 時鐘延展方面,開漏支持時鐘延展,推挽結構不支持時鐘延展。原因和上面的推挽不支持線與一樣的。有的人會有疑問,時鐘延展不是在 SCL 低電平時,從設備去拉 SCL 線嗎?不應該有問題呀。但如果是推挽 GPIO,此時主控會嘗試拉高 SCL ,才會發現 SCL 被從設備拉低,這時候就會短路。

再次提醒,線與:當總線上只要有一個設備輸出低電平,整條總線便處于低電平狀態,這時候總線被稱為占用狀態。

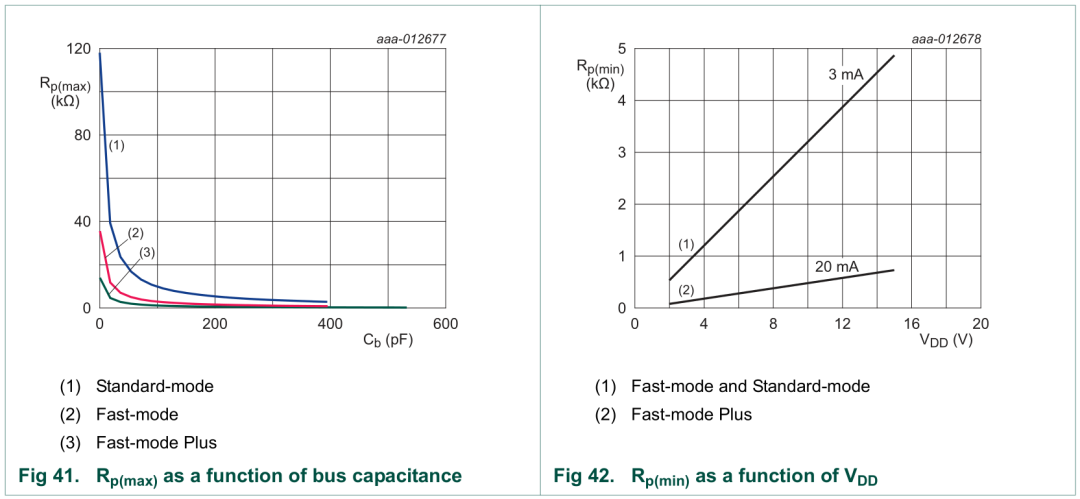

3、上拉電阻計算

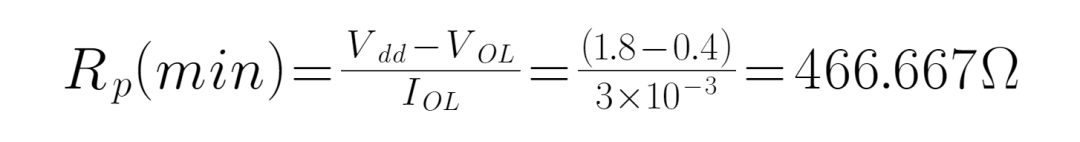

1、上拉電阻過小,電流大,端口低電平 level 增大,會發現總線上電平拉不到 0V。

2、上拉電阻過大,上升沿時間增大,方波可能會變成三角波。

因此計算出一個精確的上拉電阻阻值是非常重要的。計算上拉電阻的阻值,有明確計算公式:

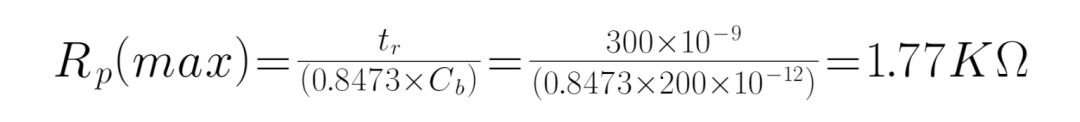

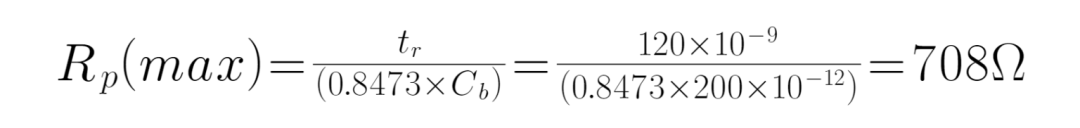

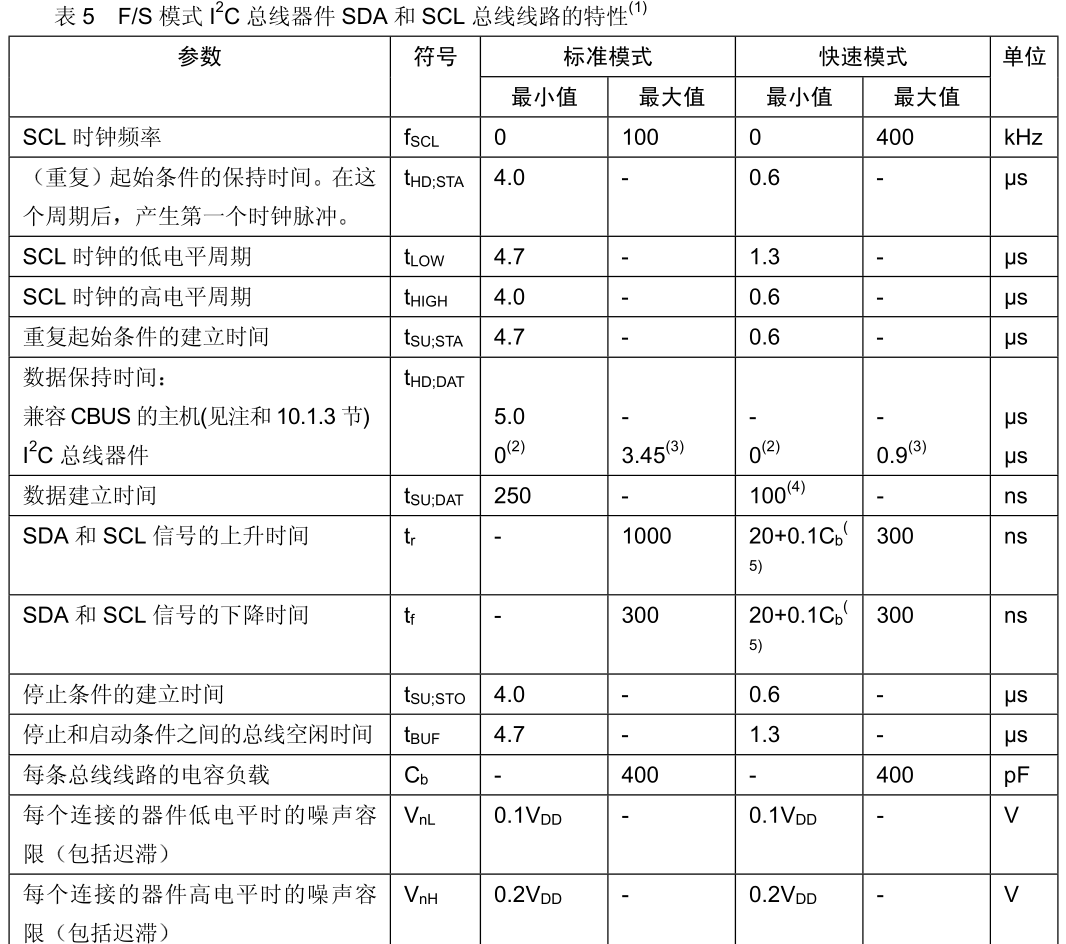

最大電阻和上升沿時間 tr 、總線電容 Cb 、標準上升沿時間 0.8473 有關。

最小電阻和電源 Vdd 電壓、GPIO 最大輸出電壓 Vol、 GPIO 最大電流 Vol 有關。

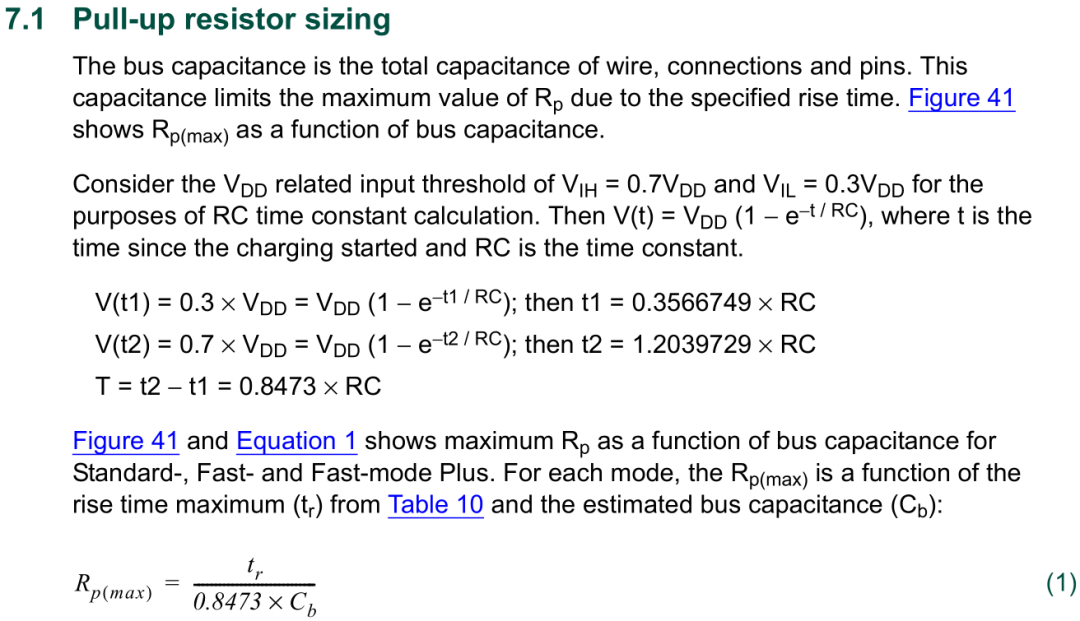

查《I2C-bus specification and user manual.pdf》7.1節:

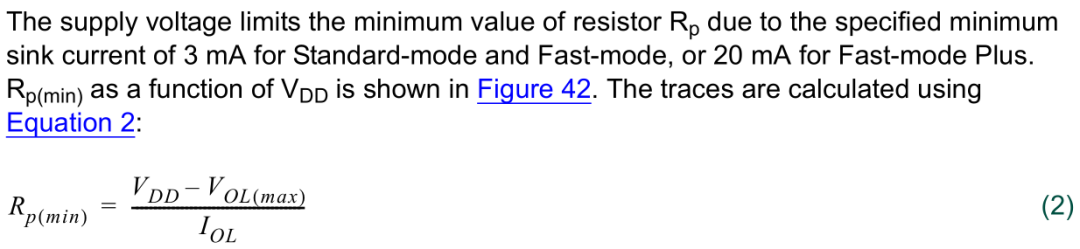

查《I2C-bus specification and user manual.pdf》表10:

從上圖可以得到最大電阻和最小電阻計算公式以及如下數據:

1、標準模式:0~100KHz,上升沿時間要求 tr = 1us

2、快速模式:100~400KHz,上升沿時間要求 tr = 0.3us

3、高速模式:up to 3.4MHz,上升沿時間要求 tr = 0.12us

note:該上升沿時間 tr 是 0.3Vdd 到 0.7Vdd 的時間要求。

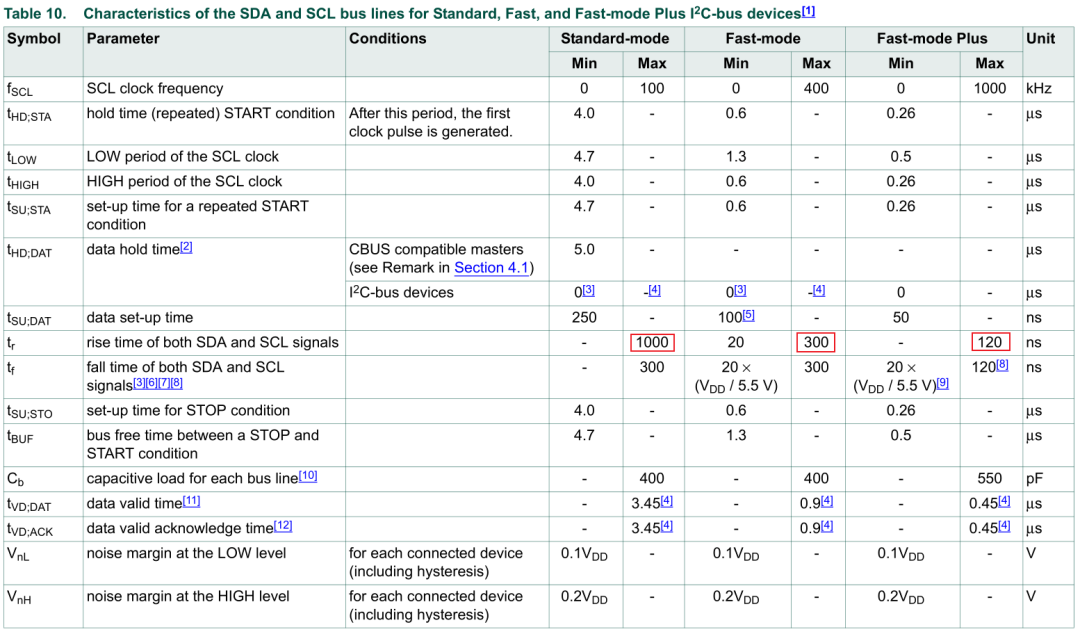

假設:Vdd 是 1.8V,Cb 總線電容 200pF(雖然協議規定負載電容最大 400pF,實際上超過 200pF波形就很不好,我們以 200pF 來計算,實際大家使用時建議以 100pF 計算)

標準模式 :

快速模式:

高速模式:

最小電阻(Vdd越大,上拉電阻就要越大):

注意,高速模式下,電源電壓一般采用 1.8 V,不會采用 3.3V,因為如果用 3.3V 計算你會發現最小電阻比最大電阻大。

采用合適的電源電壓和合適的上拉電阻,才會讓你的 I2C 傳輸信號最優。

大家在不同速率采用的電阻一般有以下幾種:1.5K、2.2K、4.7K。

上拉電阻關系圖

3、I2C Transfer

0、Definition of timing

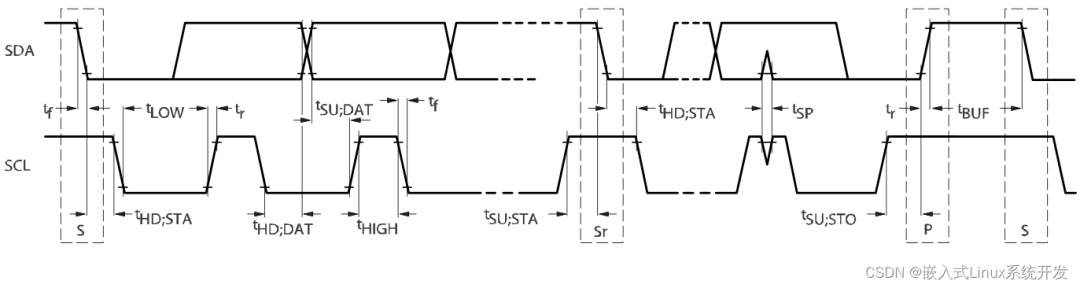

想要深入探討 I2C 協議,必須深刻理解各種時間的定義,如下為 F/S-mode

- 建立時間(Tsu):時鐘上升沿到來之前,輸入端數據已經到來并穩定持續的時間間隔。

- 保持時間(Thd):時鐘上升沿到來之后,輸入端數據繼續保持穩定并持續的時間間隔。

| 標識符 | 定義 |

|---|---|

| tf | 信號下降時間 |

| tr | 信號上升時間 |

| tLOW | 信號低電平時間 |

| tHIGH | 信號高電平時間 |

| tHD;DAT | 數據保持時間 |

| tSU;DAT | 數據建立時間 |

| tSP | 輸入濾波器必須抑制的毛刺脈寬 |

| tBUF | 啟動和停止條件的空閑時間 |

| tHD;STA | 重復起始條件的保持時間 |

| tSU;STA | 重復起始條件的建立時間 |

| tSU;STO | 停止條件建立時間 |

Sr 重新啟動,S 啟動,P 停止。

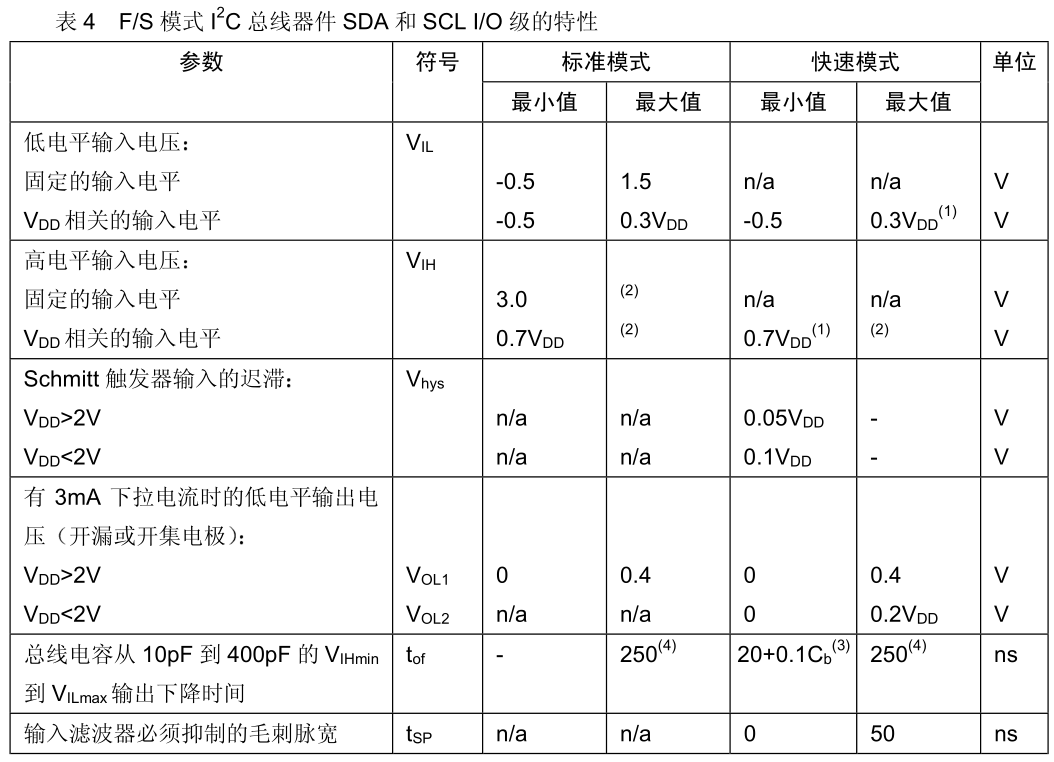

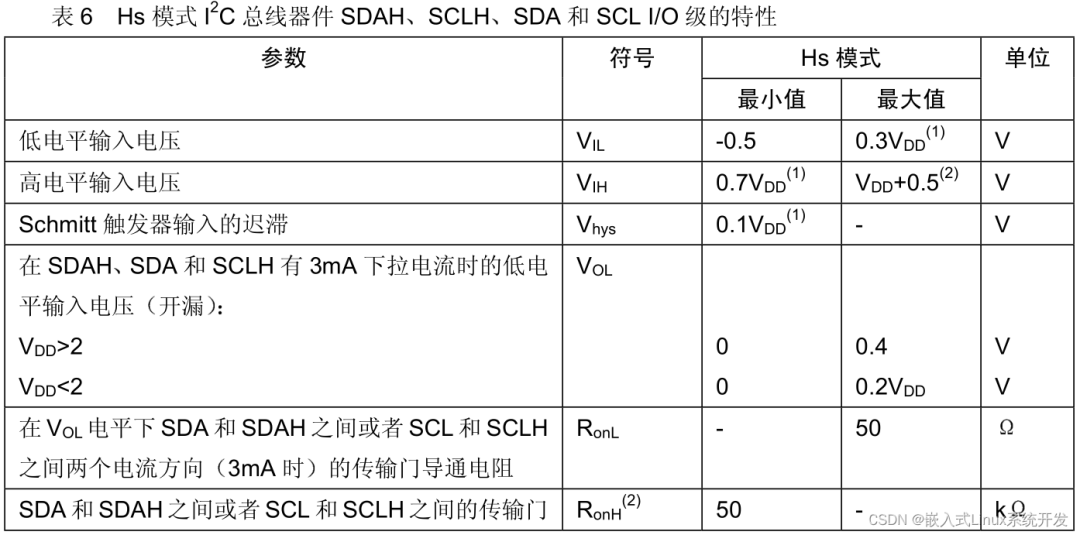

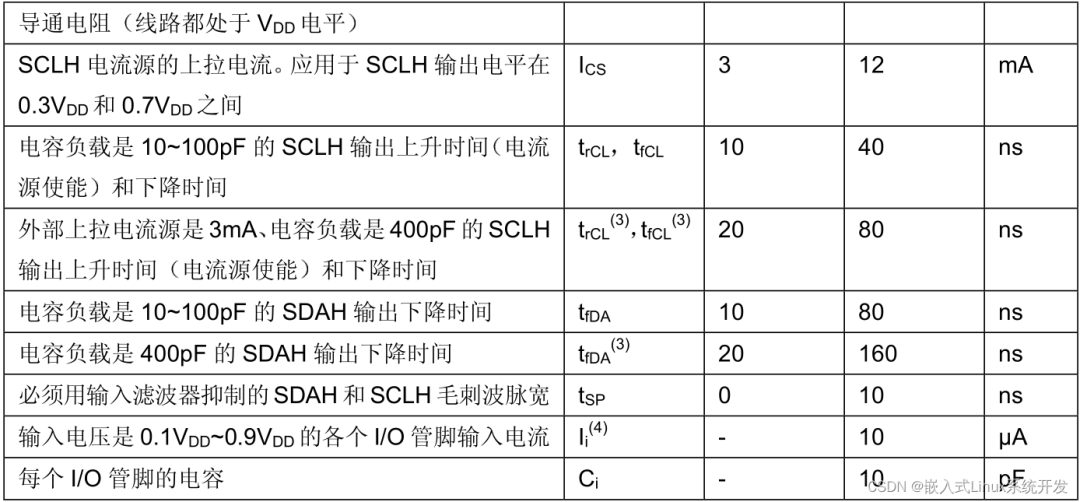

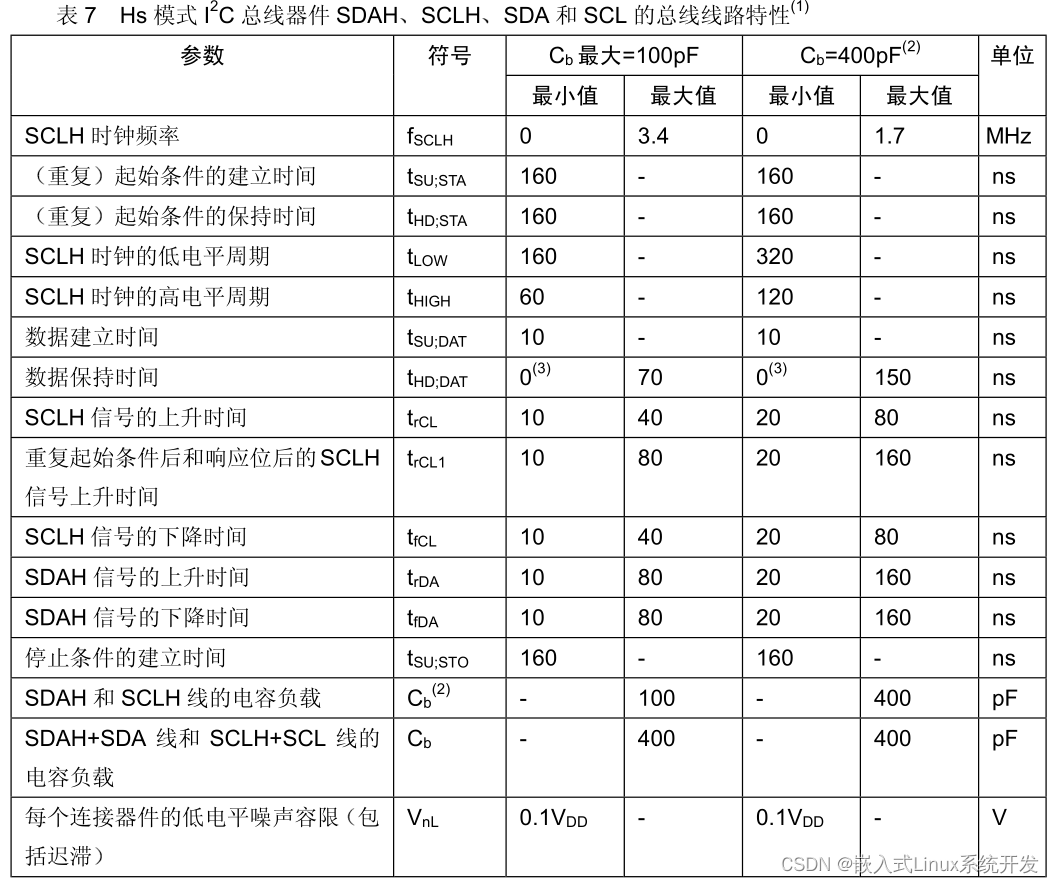

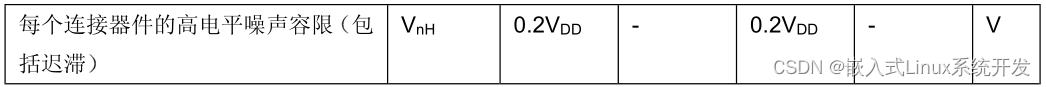

如上參數在 spec 中有嚴格規定,可查表,一般 standard mode 和 Fast mode 在一起,Hs mode 單獨列,表4、表5、表6、表7:

Master

- 提供時鐘 SCL

- 開啟和停止數據傳輸

- 尋址其他設備

slave

- 被主設備尋址

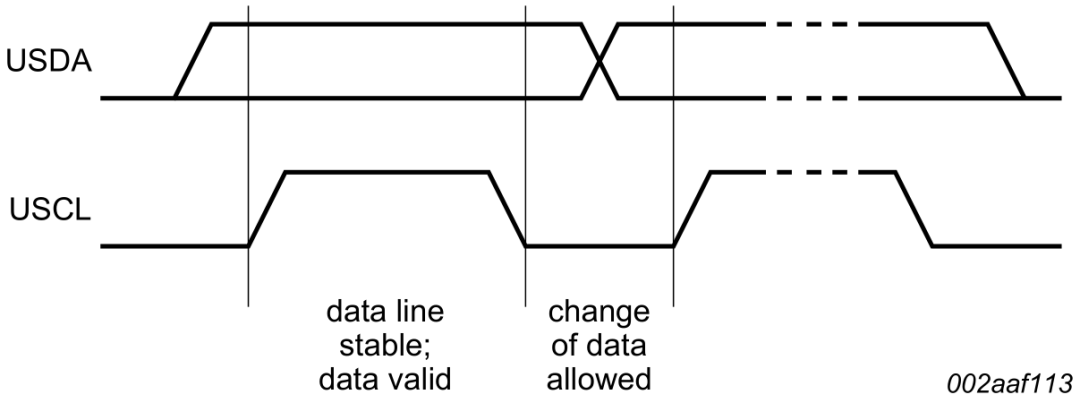

1、數據有效性

在 SCL 高電平期間,SDA 必須穩定,所以一般情況下,SCL 高電平寬度小,SDA 高電平寬度大,用示波器看也是這樣的。

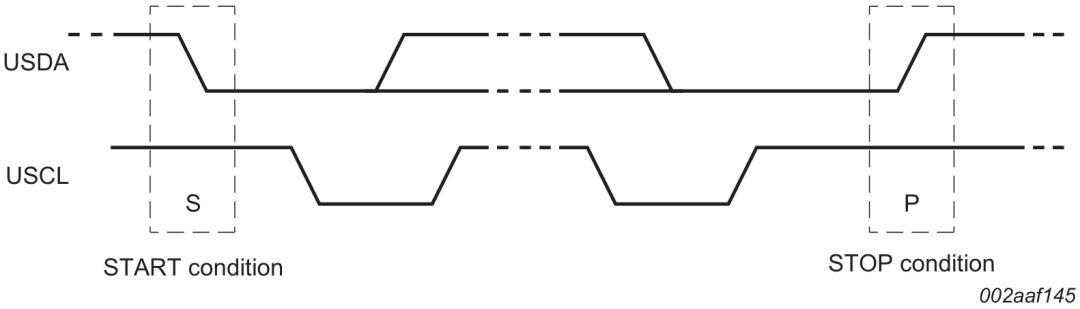

2、起始條件和停止條件

起始條件:SCL 高電平時,SDA 由高變低。

停止條件:SCL 高電平時,SDA 由低變高。

note:因為 SCL 和 SDA 兩根線有上拉電阻,因此空閑時兩根線為高電平。因此,START 條件一定是某條線拉低,spec 規定是 SDA 線拉低為開始條件。這也是開始條件和停止條件不能互換的原因。(至于為什么不是 SCL 線拉低為開始條件,大家看到后面會理解)

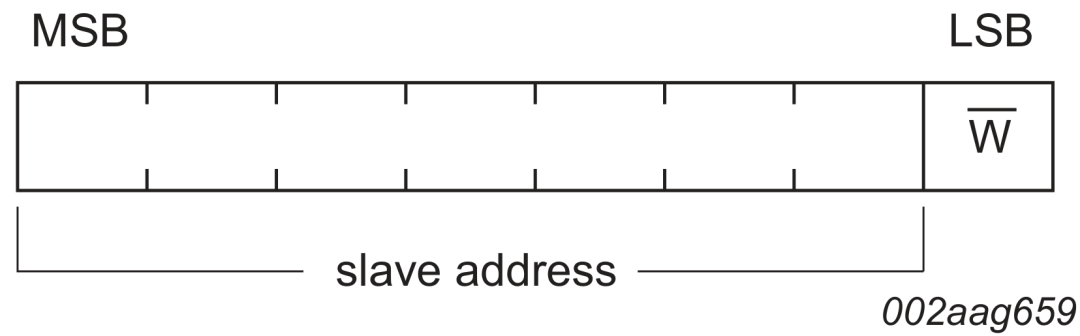

byte format

- 傳輸長度必須是一個字節(8 bit)

- 每次傳輸的字節不受限制

- 數據必須以 MSB 開頭進行傳輸,也就是先傳輸最高位

-

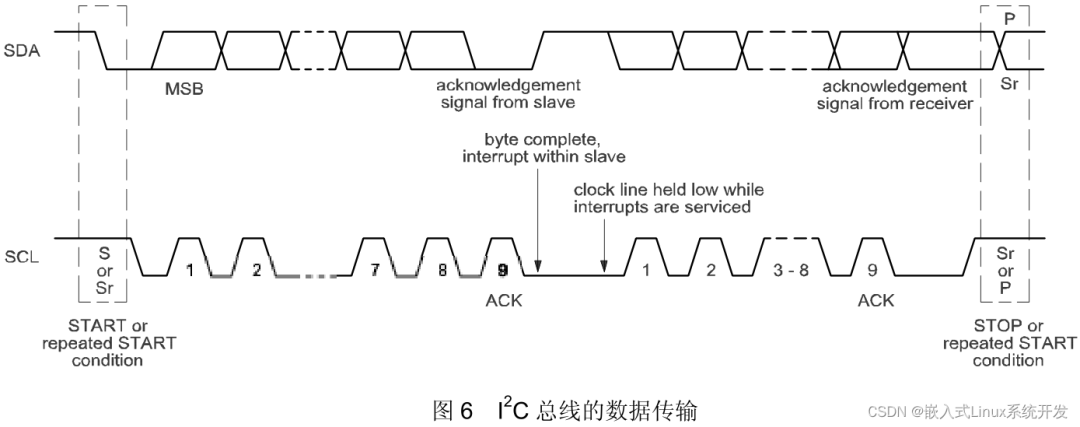

從機可以將時鐘線 SCL 保持在低位,迫使主機進入等待狀態。

在 ACK 后,從設備可以拉低 SCL 線進行時鐘延展(比如從設備需要準備數據等)

note:SCL 高電平的時候,SDA 開始采樣,SDA 是高就是 1,是低就是 0。SCL 低電平期間,SDA 變換數據。不可以在 SCL 高電平期間變換數據,否則會認為是 起始和停止條件。

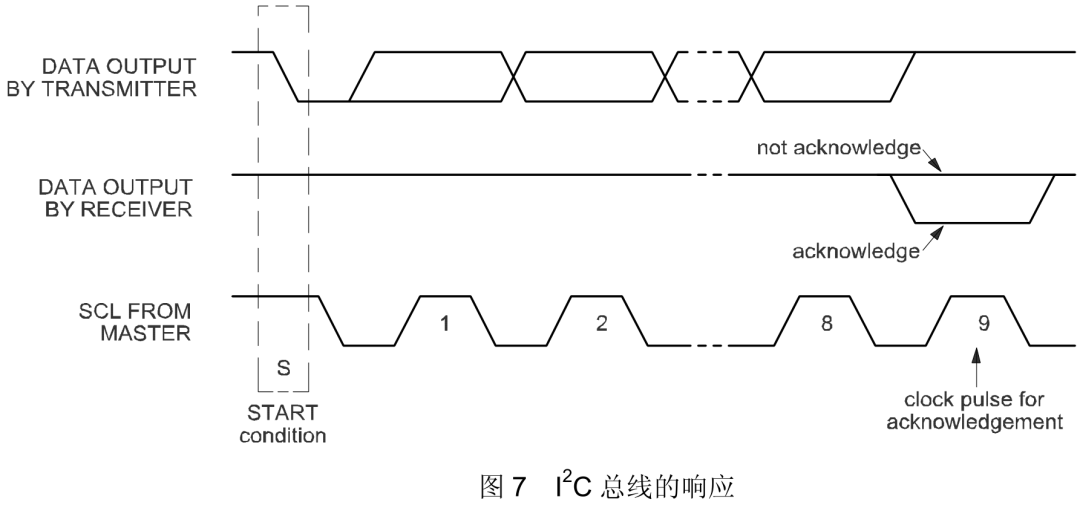

3、ACK or NACK

每次傳輸完一個字節以后,從設備要進行一個回應,回應 ACK 或者 NACK。

ACK :在傳輸 8 bit 以后,在第九個 bit ,SCL 高電平,如果 SDA 是低電平,說明回應了 ACK。

NACK:在傳輸 8 bit 以后,在第九個 bit ,SCL 高電平,如果 SDA 是高電平,說明回應了 NACK。

spec 規定以下五種情況會出現 NACK

- 主機發送到總線上的地址,卻沒有匹配的從機,因此出現 NACK

- 從機處于 busy 狀態,出現 NACK

- 在傳輸過程中,從機獲取其不理解的數據或命令。

- 在傳輸過程中,從機無法再接收任何數據字節。

- 主接收機必須向從發射機發送傳輸結束的信號的時候,會出現 NACK。

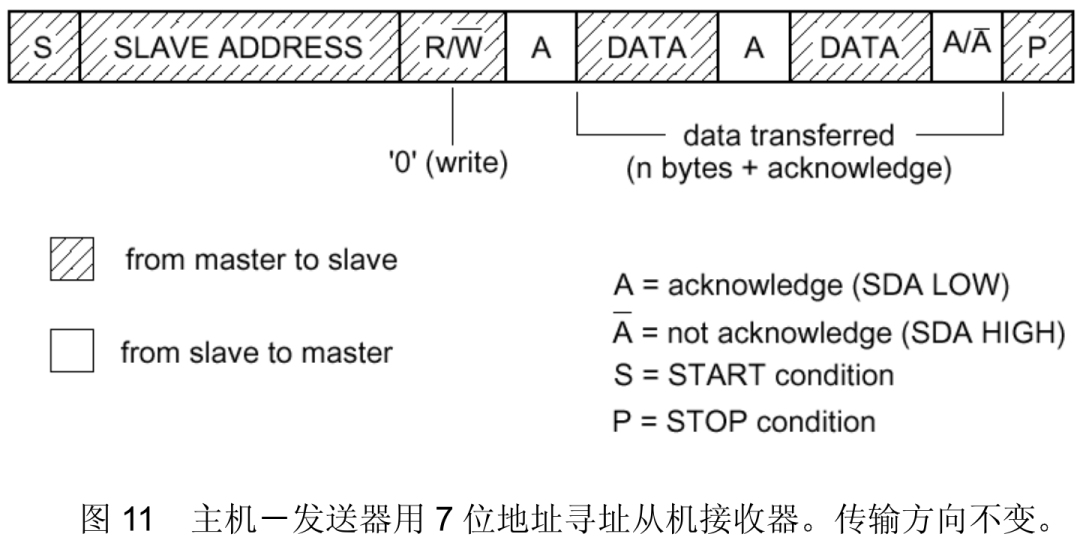

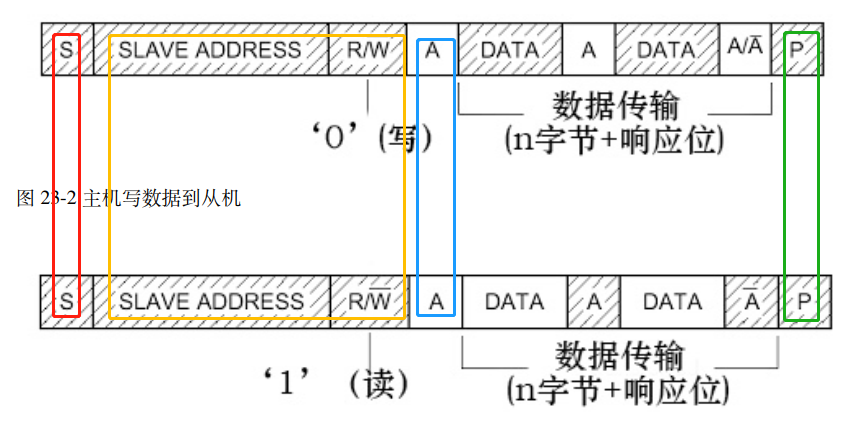

4、write data

主機向從機寫數據,在通信結束的最后一個字節,正常從機都會回應一個 ACK ,告訴主機最后一個字節寫成功,這時候主機會產生 STOP 信號。

主機向從機寫數據,在通信結束的最后一個字節,正常從機都會回應一個 ACK ,告訴主機最后一個字節寫成功,這時候主機會產生 STOP 信號。

如果最后一個字節從機回應一個 NACK ,主機也會產生一個 STOP 信號,并且這時候主機會向上層上報一個 ACK error 。

上層如何處理,是上層的事情,芯片設計時 I2C 外設控制器一定會在這個時候產生一個 ACK error。如果用的是 Linux 操作系統,可以配置在上層忽略最后的這個 ACK error 。

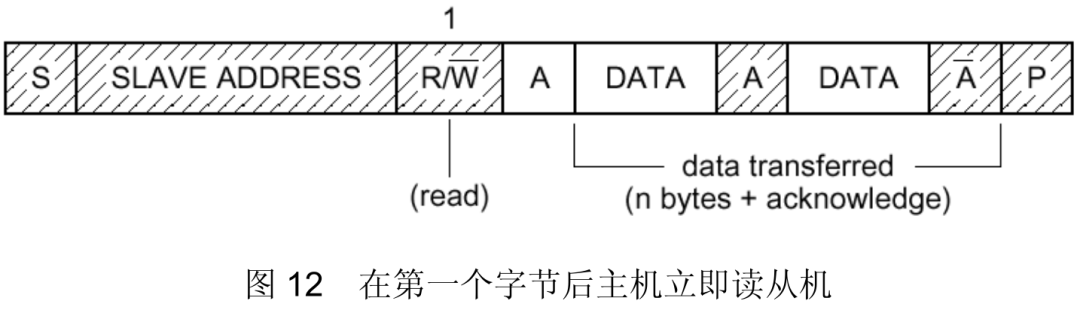

5、read data

主機從從機讀數據,在最后一個字節后,主機會給從機一個 NACK ,告訴從機不再讀數據了,然后主機產生一個 STOP 信號。這是唯一一個在正常傳輸過程中的 NACK

主機從從機讀數據,在最后一個字節后,主機會給從機一個 NACK ,告訴從機不再讀數據了,然后主機產生一個 STOP 信號。這是唯一一個在正常傳輸過程中的 NACK

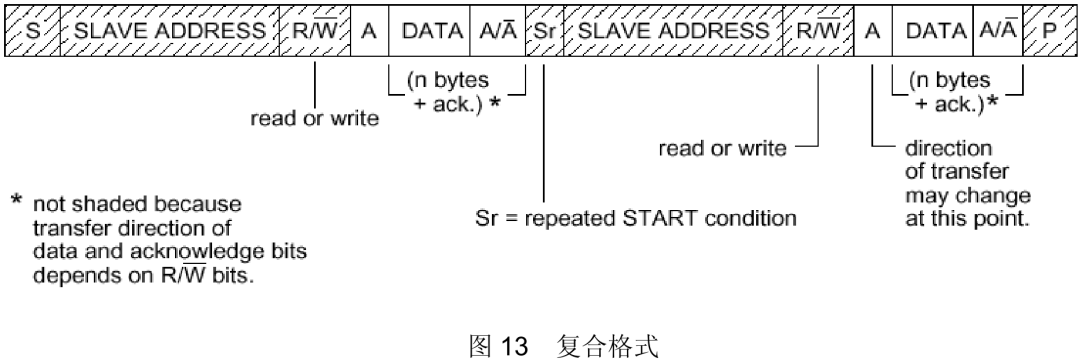

6、復合格式

在重復開始信號 Sr 前后,兩個 slave address 可以不同。也就是說,一個 I2C 主機可以不產生 STOP 信號,直接產生一個重復開始信號去訪問另外一個從機。(如果 I2C 總線上有多個主機,則不用再一次仲裁,節省時間)

在重復開始信號 Sr 前后,兩個 slave address 可以不同。也就是說,一個 I2C 主機可以不產生 STOP 信號,直接產生一個重復開始信號去訪問另外一個從機。(如果 I2C 總線上有多個主機,則不用再一次仲裁,節省時間)

另外,在 Linux 系統中,由于 i2c_msg 結構體的規定,單筆 I2C 傳輸最大 64KB,超過 64KB 也要再來一次 STOP 信號或者 重復開始信號。

7、I2C Transfer Regulation

- 以 START 條件開始

- 以 STOP 條件結束

- 傳輸的第一個字節為 7bit 從機地址 + 1bit 讀寫位

- 每個總線上的設備都會比較 STRAT 信號后面的 7bit 地址與自己的地址是否匹配

- 每個 byte(8 bits) 后面都會有 ACK 或者 NACK

- 在 START 信號或者 repeated START 信號后,從機必須重置自己的總線邏輯

- 一個 START 后面緊跟著一個 STOP 信號,是非法格式

- 主機 master 可以不產生 STOP 信號,而是直接產生一個 repeated START 信號+另外一個設備地址,直接開始訪問另外一個設備

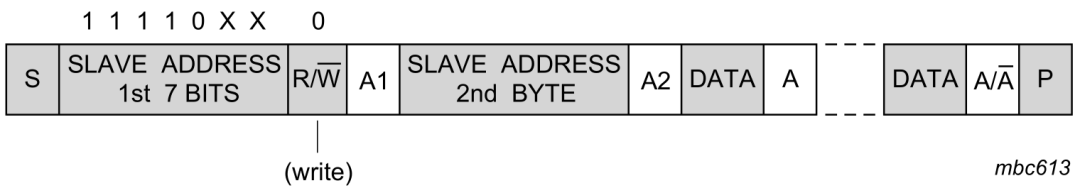

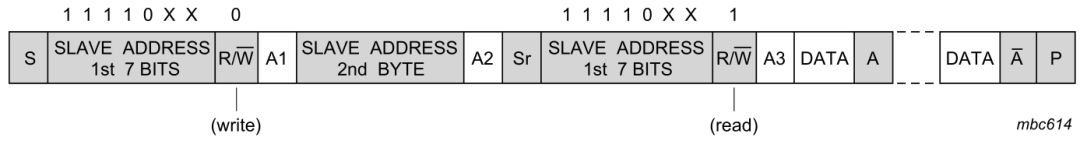

8、10-bit addressing

10 位從機地址規定如下,其中 11110 為 10 位地址的指示信號,A9-A0 表示 10bits 地址:

主機向從機寫數據(需要 2 bytes)

主機從從機讀數據(需要 3 bytes)

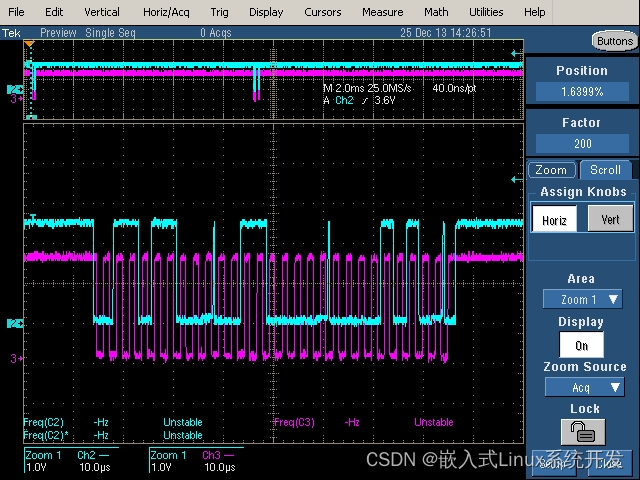

9、示波器波形圖示例

- 主機向從機寫數據

上圖中,大家會在 SDA 線上發現有三個很細的毛刺,每次都是出現在從機回應了 ACK 以后。這是由于從機拉低 SDA 線回應 ACK 后,釋放了 SDA 線,因為有上拉電阻的存在,SDA 線被拉高,然后主機又立刻接管了 SDA 線,把 SDA 線拉低。即該毛刺是由于 slave 和 master 換手有時差導致的。

因為該毛刺是出現在 SCL 低電平期間,而 SCL 低電平期間,SDA 本來就可以變換數據,所以不會對 I2C 通信產生負面影響,該毛刺一般不用關注。

如果覺得波形不美觀,可以找芯片原廠,看能否調整 master 控線的 setup time 和 hold time ,來減小該毛刺的幅值。

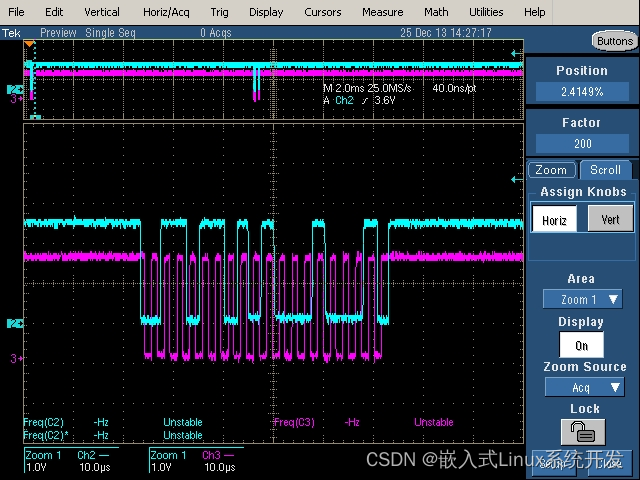

- 主機從從機讀數據

10、補充

I2C 不支持從設備在 SCL 和 SDA 總線上發起一個中斷,通知主設備來讀數據。有中斷需求的從設備需要額外接一根中斷線,通知主控數據已經準備好,讓主控發起讀數據的操作。

這無疑增加了系統復雜性,多占用了 pin 腳。I3C 則不存在這種問題,I3C 允許從設備在 SCL 和SDA 上發起中斷,叫“帶內中斷”,I3C 后面會講。

4、I2C Synchronization And Arbitration

三個概念:時鐘延展、同步、仲裁

1、Clock stretching 時鐘延展

- 時鐘延展:通過將 SCL 線保持在低電平來暫停傳輸。在 SCL 再次拉高之前,傳輸無法進行。

- 從機通過將 SCL 線拉低,強制主機進入等待狀態。

- 時鐘延展功能是可選的,非必須。

byte level

時鐘延展導致需要更多時間來存儲接收到的字節或準備另一個要傳輸的字節

bit level

通過延長每個時鐘低電平周期來降低總線時鐘。任何主機的速度都與該設備的內部運行速度相適應。

在 Hs mode,只能使用 byte level,也就是只能在傳輸完一個字節(8bits)后拉低 SCL 進行時鐘延展。在 Standard-mode 和 Fast-mode,既可以 byte level 也可以 bit level,bit level 意思是哪怕你之傳輸了 2 bits ,從機也可以拉低 SCL 線進行時鐘延展,臨時暫停傳輸。

時鐘延展通俗解釋

I2C 主設備始終控制著時鐘線 SCL,不論是往設備寫還是從設備讀。一般情況下,如果操作對象是 EEPROM 或者其他簡單設備而言,無所謂,但是,如果從設備是處理器,在接到主機命令后要去處理一些運算然后得出結果返回給主機。這個時候可能造成來不及處理。怎么辦?這時,從設備會主動控制時鐘線把它拉低!直到數據準備好之后再釋放時鐘線,把控制權交還給 MASTER。這也是 I2C 通信系統中,從機唯一能控制總線的時候!

關鍵是很多 I2C 主機不支持 clock stretching 功能,所以,無法和帶有 clock stretching 功能的從機通信!所以,各位在選擇主機器件之前,必須要注意這一點,不然整個設計方案可能報廢,影響很大。

2、Synchronization And Arbitration

I2C 是多主從架構,也就是一條總線上可以同時掛多個 I2C 主機和多個 I2C 從機。

但是如果有兩個或兩個以上的主機同時向總線上發送啟動信號并開始傳送數據,這樣就形成了沖突。要解決這種沖突,就要進行仲裁的判決,這就是 I2C 總線上的仲裁。

I2C 總線上的仲裁分兩部分:SCL 線的同步和 SDA 線的仲裁,這兩部分沒有先后關系,是在同時進行。

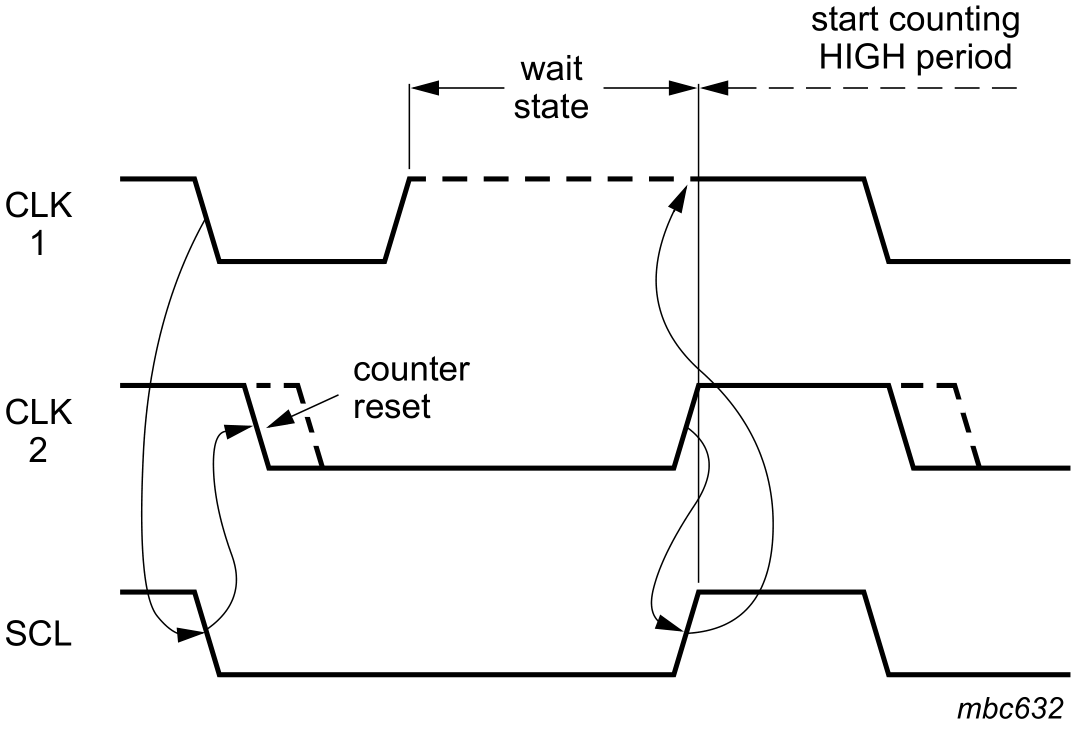

SCL Synchronization

所有主機都在 SCL 線上輸出自己的時鐘,因此同步過程需要定義自己的時鐘。

SCL 同步是由于總線具有線“與”的邏輯功能,即只要有一個節點發送低電平時,總線上就表現為低電平。當所有的節點都發送高電平時,總線才能表現為高電平。正是由于線“與”邏輯功能的原理,當多個節點同時發送時鐘信號時,在總線上表現的是統一的時鐘信號。這就是 SCL 的同步原理。

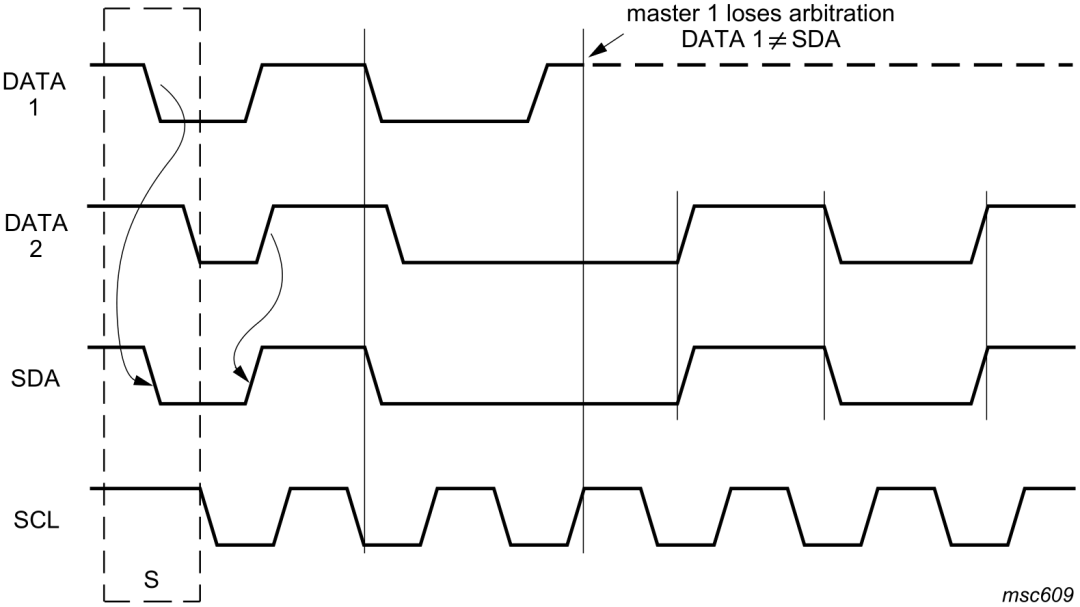

同步過程如下圖:

主機 1 產生 CLK1,主機 2 產生 CLK2,同時向 SCL 線上輸出自己的時鐘,由于 CLK2 的低電平更長,因此 SCL 線上出現的電平和 CLK2 保持一致。因此在第一個周期中,CLK1 后期進入了高電平等待狀態。后面 SCL 上的電平以 CLK2 為準。

SDA Arbitration

SDA 線的仲裁也是建立在總線具有線“與”邏輯功能的原理上的。節點在發送1位數據后,比較總線上所呈現的數據與自己發送的是否一致。是,繼續發送;否則,退出競爭。

SDA 線的仲裁可以保證 I2C 總線系統在多個主節點同時企圖控制總線時通信正常進行并且數據不丟失。總線系統通過仲裁只允許一個主節點可以繼續占據總線。

- 仲裁在 SDA 上進行,此時 SCL 為高電平。

- A 主機傳輸高電平,B 主機傳輸低電平,A 失去仲裁。

- 丟失仲裁的主機將生成時鐘脈沖,直到丟失仲裁的字節結束。

仲裁過程:

DATA1 和 DATA2 分別是兩個主機向總線所發送的數據信號,SDA 為總線上所呈現的數據信號,SCL 是總線上所呈現的時鐘信號。

主機 1、2 同時發送起始信號,在 clock1 ,兩個主機都發送了高電平信號。這時總線上呈現的信號為高電平,兩個主節點都檢測到總線上的信號與自己發送的信號相同,繼續發送數據。

第2個時鐘周期,2個主節點都發送低電平信號,在總線上呈現的信號為低電平,仍繼續發送數據。

在第3個時鐘周期,主節點1發送高電平信號,而主節點2發送低電平信號。根據總線的線“與”的邏輯功能,總線上的信號為低電平,這時主節點1檢測到總線上的數據和自己所發送的數據不一樣,就斷開數據的輸出級,轉為從機接收狀態。這樣主節點2就贏得了總線,而且數據沒有丟失,即總線的數據與主節點2所發送的數據一樣,而主節點1在轉為從節點后繼續接收數據,同樣也沒有丟掉 SDA 線上的數據。因此在仲裁過程中數據沒有丟失。

5、I2C Hs-mode

HS mode 為什么單獨講解?因為高速模式和其他模式有很多不一樣的地方。

- 速度高達 3.4MHz。

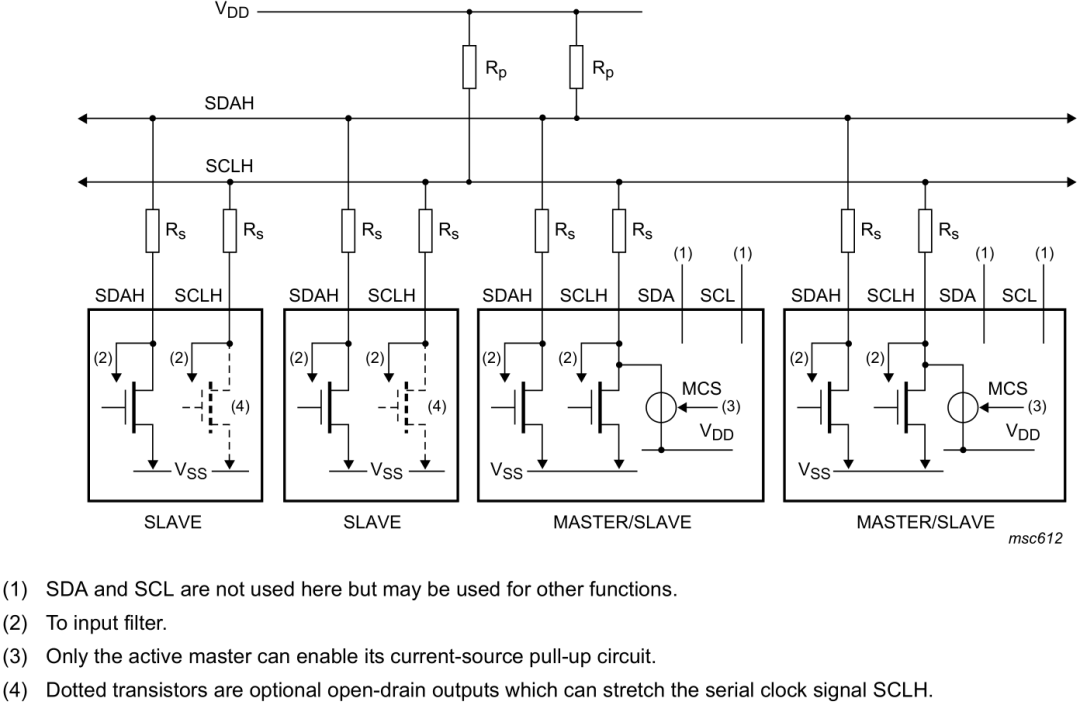

- 用的是 SDAH 和 SCLH 信號線,不是 SDA 和 SCL

Master device

- SDAH/SCLH 有一個開漏輸出 buffer, SCLH 有一個電流源上拉電路,這個電流源電路縮短了 SCLH 信號的上升時間。任何時侯在 Hs 模式只有一個主機的電流源有效。

- 沒有仲裁和時鐘同步,以加速位處理能力。仲裁過程一般在前面用 F/S 模式傳輸主機碼后結束。

- 以高電平和低電平是 1:2 的比率產生一個串行時鐘信號。解除了建立和保持時間的時序要求。

- 高速數據 SDAH 和高速串行時鐘 SCLH 線通過這個電橋與 F/S 模式器件的 SDA 和 SCL 線分隔開來。減輕了SDAH 和 SCLH 線的電容負載,使上升和下降時間更快。

Slave device

- Hs 模式從機器件與 F/S 從機器件的唯一差別是它們工作的速度。Hs 模式從機在 SCLH 和 SDAH輸出有開漏輸出 buffer 。SCLH 管腳可選的下拉晶體管可以用于拉長 SCLH 信號的低電平,但只允許在 Hs 模式傳輸的響應位后進行。

- Hs 模式器件的輸出可以抑制毛刺,而且 SDAH 和 SCLH 輸出有一個 Schmitt 觸發器

- Hs 模式器件的輸出緩沖器對 SDAH 和 SCLH 信號的下降沿有斜率控制功能

- 調整了串行數據 SDA 和串行時鐘 SCL 信號的時序。沒有必要與其他總線系統如 CBUS 兼容,它們不能在增加的位速率下工作。

- 如果快速模式器件的電源電壓被關斷,SDA 和 SCL 的 I/O 管腳必須懸空,不能阻塞總線。

- 連接到總線的外部上拉器件必須調整以適應快速模式 I2C 總線更短的最大允許上升時間。對于負載最大是 200pF 的總線,每條總線的上拉器件可以是一個電阻;對于負載在 200pF~400pF 之間的總線,上拉器件可以是一個電流源(最大值 3mA)或者是一個開關電阻電路,如下圖:

只有 Hs 模式器件的系統的物理 I2C 總線配置

(可選)串聯電阻器 Rs 保護 I2C 總線設備的 I/O 免受總線上的高壓尖峰影響,并將振鈴和干擾降至最低。

右下角兩個設備,不光是從設備,也可以當主設備。這種器件有一個 MCS 電流源。如果總線上器件較多,會導致總線電容較大,拉升總線電壓相當于給電容充電,這需要時間,這會導致波形上升沿過緩,所以加了電流源可以使上升沿很快。

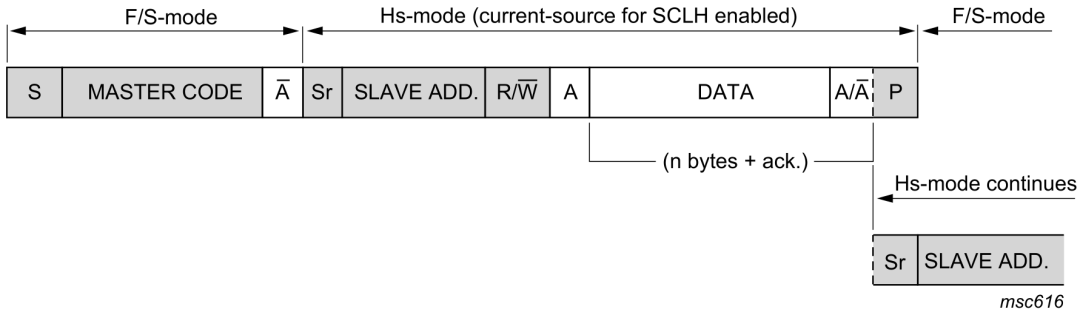

1、data transfer format in Hs-mode

- START condition (S)

- 8-bit master code (0000 1XXX)

- Not-acknowledge bit (A)

2、在 Hs 模式下啟用電流源上拉電路

3、在下一次重復啟動條件后,依舊在 Hs-mode

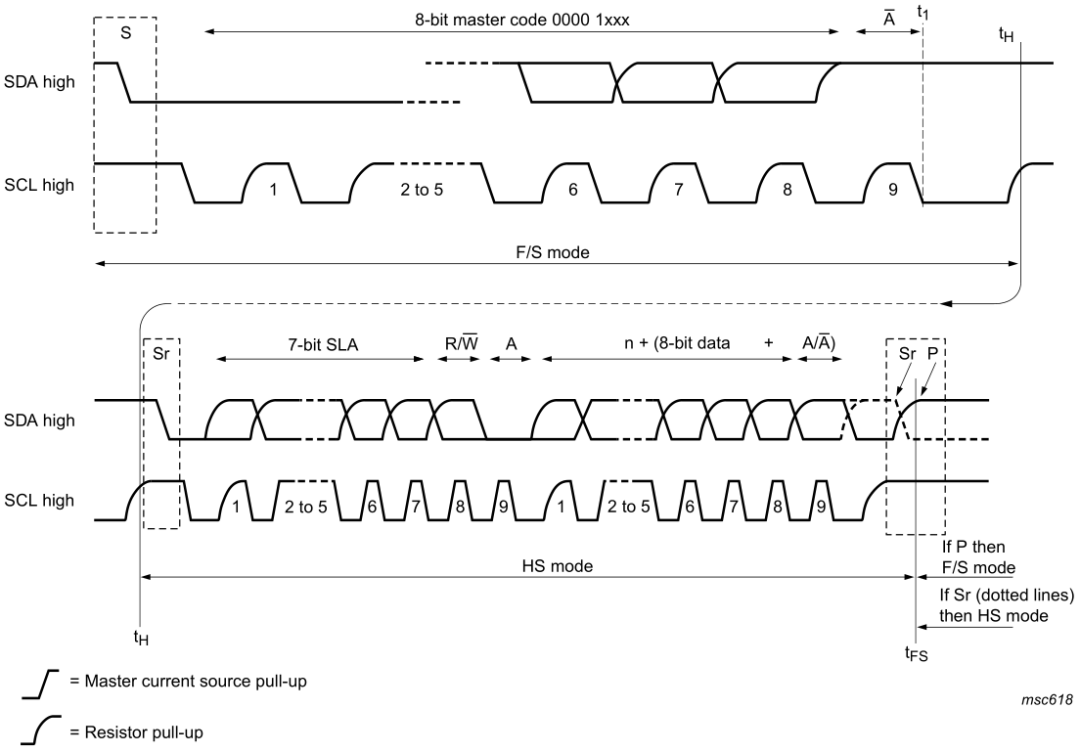

由上圖可以看出,在快速模式(FS mode)下發送一個 Master code,然后切換到高速模式(HS mode),發送從設備地址。

在第一階段 FS mode 時候,發送主機碼(0x0000 1xxx),這時候會進行仲裁。因此 Hs mode 階段沒有時鐘同步和仲裁。

在中間的 HS mode 傳輸結束后,如果是一個 STOP 信號,則立刻回到 F/S mode,如果是 Sr 重復開始i信號,則依舊留在 Hs mode(右下角有說明)

上圖為 Hs mode 完整通信波形示意圖。先在快速模式下發送主機碼,不需要從機回復。然后切換到高速模式,會發送一個 reSTART,然后進行數據傳輸。

需要注意如下幾點:

- 右上角 t1 到 tH 時間之內,可以進行時鐘延展。

- Hs mode 中,只能在 byte level 級別進行時鐘延展,也就是一個 byte 傳輸結束后進行時鐘延展。

- 注意左下角的示意圖,如果是直上直下的這種波形,是主機電流源上拉。如果是緩坡上升沿,則是電阻上拉。

博主將 I2C spec 單獨總結出來,意思是說,不管你是單片機平臺,還是 FreeRTOS 平臺,還是 Linux 平臺,I2C spec 都是一樣的,所以總結為一文方便大家查看。

原文標題:I2C spec 總結

文章出處:【微信公眾號:一口Linux】歡迎添加關注!文章轉載請注明出處。

-

總線

+關注

關注

10文章

2881瀏覽量

88090 -

I2C

+關注

關注

28文章

1487瀏覽量

123777 -

I2C總線

+關注

關注

8文章

391瀏覽量

60941

原文標題:I2C spec 總結

文章出處:【微信號:yikoulinux,微信公眾號:一口Linux】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

I2C總線原理詳解

I2C總線詳解

I2C基礎知識入門簡單介紹

一文看懂I2C協議

一文詳解I2C總結的基礎知識

一文詳解I2C總結的基礎知識

評論