電子行業(yè)正在從硬件定義向系統(tǒng)定義轉(zhuǎn)變,而電子產(chǎn)品越來越受應用驅(qū)動。結(jié)果,產(chǎn)品差異化已經(jīng)轉(zhuǎn)移到系統(tǒng)(基于軟件)的內(nèi)容上,而硬件平臺及其開發(fā)過程變得越來越商品化。在這個新興領域中抓住新機遇需要在電子行業(yè)的基礎上進行擴展。必須解決系統(tǒng)開發(fā)人員的需求,并且必須將對這些需求的響應集成到一個解決方案中。

與進度延誤和產(chǎn)品質(zhì)量有關的潛在風險已經(jīng)變得巨大。上市時間壓力和軟件定義產(chǎn)品功能的趨勢使得傳統(tǒng)的順序流程,其中系統(tǒng)級芯片 (SoC) 開發(fā)之后是電路板和設備開發(fā),然后是軟件開發(fā),已經(jīng)過時了。在系統(tǒng)啟動時滿足功能、功率和性能已成為最具挑戰(zhàn)性的任務。對于許多 OEM 公司來說,系統(tǒng)啟動占用了整個開發(fā)周期的三分之一到二分之一,產(chǎn)品質(zhì)量和可預測性成為第二和第三優(yōu)先事項。系統(tǒng)啟動是 OEM 高管最關心的問題,因為它可以決定或破壞其產(chǎn)品的盈利能力。

如果你參與過關于系統(tǒng)實現(xiàn)的辯論,你的問題可能是這樣的:

系統(tǒng)級驗證的最佳方法是什么?

我們是否應該投資于更快的虛擬平臺的承諾,同時處理它們固有的時間不準確性?

基于 FPGA 的原型設計方法——成本低但啟動時間長——是否足以完成工作?

我們應該僅僅依靠系統(tǒng)仿真還是仿真加速?

如何利用這些技術與我們的 IP 供應商和客戶進行協(xié)作?

在過去的 15 年里,我參加了幾十個小組和圓桌會議,提出了這樣的問題。答案很大程度上取決于具體負責人的責任或他或她公司的產(chǎn)品,有些人在更換公司時會改變答案。多年來,我們(在 Cadence)意識到所提供的特定產(chǎn)品并不那么重要。重要的是客戶獲得的價值以及他們需要花費的資源、時間和金錢。我們也意識到?jīng)]有一種產(chǎn)品或平臺可以解決所有的系統(tǒng)驗證和確認問題。需要多個平臺的組合。

成功完成下一代設計的最大挑戰(zhàn)是避免芯片重新旋轉(zhuǎn)、按時完成越來越多的軟件,還是找到驗證硬件和軟件之間交互的方法?

許多驗證團隊使用臨時的技術組合以及脫節(jié)的環(huán)境和平臺,以至于他們無法完成工作。為了跟上高級系統(tǒng)開發(fā)的需求,傳統(tǒng)的方法根本不夠高效。驗證吞吐量無法滿足當今日益復雜的設計要求。根據(jù)最近與大型復雜系統(tǒng)驗證團隊的討論,使用寄存器傳輸語言 (RTL) 仿真完成復雜的驗證任務不再有效。需要的是一個高性能環(huán)境,適用于整個設計過程中的系統(tǒng)上下文中的硬件驗證、低級固件和軟件開發(fā)。

大圖解決方案必須提供統(tǒng)一的流程,為用戶提供熟悉的環(huán)境,能夠最大化和擴展子系統(tǒng)和系統(tǒng)級仿真的仿真能力。環(huán)境和性能需要對系統(tǒng)、軟件和硬件驗證團隊具有吸引力和吸引力。Cadence 設想的流程結(jié)合了開放、連接、可擴展和一流的硬件/軟件平臺,包括硬件輔助驗證和基于軟件的工具。集成流程需要在為設計團隊和企業(yè)級客戶提供可擴展的可用性方面開辟新天地,在多個抽象層次上連接設計和驗證流程,提供高性能和靈活的建模環(huán)境。想象一下您可以使用集成流程為系統(tǒng)實現(xiàn)。

業(yè)務痛點

上市時間是系統(tǒng)開發(fā)商和系統(tǒng)公司面臨的第一大挑戰(zhàn)。公司(尤其是在消費市場)面臨著滿足其市場窗口并將其整體設計周期從 12 個月縮短至 6 個月的壓力。這些公司需要能夠以可預測的時間表與供應商和合作伙伴進行有效的溝通和互動。CEO 希望走上革命性的道路,將他們的組織從芯片或 IC 制造商轉(zhuǎn)變?yōu)橄到y(tǒng)公司。

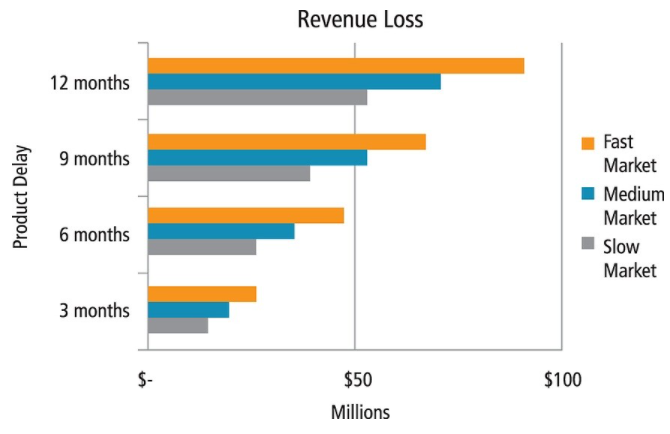

在這一轉(zhuǎn)型過程中,公司領導者需要將他們的硬件和軟件團隊整合為一個。開發(fā)服務并贏得市場特定應用的標準產(chǎn)品的方法將讓位于在正確的時間進入市場,同時滿足規(guī)范。與此同時,這些具有前瞻性的公司將與正在生成內(nèi)容的合作伙伴(Facebook、谷歌、Netflix 以及類似的組織或運營商,如 AT&T、Comcast 和 Verizon)合作。因此,電子行業(yè)參與者很可能錯過他們的市場窗口,除非他們改變他們開發(fā)系統(tǒng)的方式。圖 1 顯示了由于在慢速、中速和快速細分市場中缺少市場窗口而導致的潛在收入損失風險。六個月的延遲可能導致平均損失 5000 萬美元。

圖 1:沒有在正確的時間進入市場的風險隨著市場的快速發(fā)展而增加。

技術痛點

隨著系統(tǒng)設計復雜性(想想多核、多線程、多任務和快速增加的軟件內(nèi)容)的增長,滿足應用程序驅(qū)動的需求變得更具挑戰(zhàn)性。一個關鍵挑戰(zhàn)是從芯片流片到上市時間。系統(tǒng)硬件/軟件啟動和集成是關鍵瓶頸。當前旨在緩解這些瓶頸的產(chǎn)品是專有儀器,采用不可配置的模型,并且不容易準備好插入第三方工具。更重要的是,這些產(chǎn)品是分散的,帶有不連貫的點工具,將集成和從一個開發(fā)階段遷移到另一個開發(fā)階段的負擔留給了用戶。這些產(chǎn)品僅限于解決單個抽象級別。

客戶的理想是能夠滿足他們所有需求的單一平臺。不幸的是,沒有單一的硬件/軟件開發(fā)平臺可以解決所有設計階段。因此,需要基于多個平臺組合的單一解決方案/流程。每個平臺都專注于具有不同優(yōu)化特性的流程的每個階段。

例如,在設計的早期,用戶需要一個可以在硬件抽象模型之上運行他們的軟件的平臺。在這個過程的后期,他們需要在硬件的準確表示之上運行他們的軟件。客戶花費數(shù)月和許多美元手動跨平臺遷移。他們需要一組連續(xù)的開放和連接平臺。選擇的開放平臺應基于標準并具有第三方支持。互聯(lián)平臺應具有集成的產(chǎn)品、方法和流程,以允許用戶自動從一個平臺遷移到另一個平臺。成功的平臺將支持整個流程中的硬件/軟件驗證和集成過程,具有可擴展的性能和容量,以支持多個抽象級別。

一套全面的開放、連接和可擴展的系統(tǒng)實現(xiàn)平臺

Cadence 通過開發(fā)和交付一整套稱為系統(tǒng)開發(fā)套件的硬件/軟件平臺來解決前面提到的技術挑戰(zhàn)。該套件是開放的、連接的和可擴展的,具有強大的生態(tài)系統(tǒng)合作伙伴關系、服務和集成方法。基于其在高級驗證和加速/仿真方面的行業(yè)領先產(chǎn)品,這一連續(xù)統(tǒng)一體在市場上創(chuàng)造了一種解決關鍵系統(tǒng)開發(fā)挑戰(zhàn)的方法。如圖 2 所示,這種方法包括四個具有性能權衡的硬件/軟件平臺。盡管所有這些平臺都支持硬件和軟件的驗證和集成,但有些平臺更側(cè)重于硬件驗證和驗證,而另一些平臺則針對軟件開發(fā)人員的更高性能。

圖 2:設計團隊需要針對離散開發(fā)階段優(yōu)化的集成平臺集,以滿足上市時間目標。

每個平臺都唯一地連接到下一個平臺,以便在用戶從一個開發(fā)階段遷移到另一個開發(fā)階段時加快硬件/軟件環(huán)境的啟動時間。

虛擬系統(tǒng)平臺

虛擬系統(tǒng)平臺為系統(tǒng)開發(fā)人員提供的工具可幫助他們創(chuàng)建和分析虛擬平臺/原型設計。軟件開發(fā)人員獲得了一個平臺,可以在用于早期軟件開發(fā)和軟件分發(fā)的抽象模型之上運行他們的軟件。它是開放的(基于標準)并提供可擴展的性能和卓越的硬件/軟件調(diào)試功能。它通過統(tǒng)一的模擬器和通用的驗證IP連接到Incisive Verification Platform。

Incisive 驗證平臺(帶有 Incisive Enterprise Simulator)

該平臺的高級驗證工具基于開放式方法 (UVM) 進行塊/芯片級驗證,具有豐富的優(yōu)化驗證 IP 組合,可擴展到其他平臺。它幫助驗證工程師啟動固件并提供硬件/軟件指標驅(qū)動的驗證功能,該功能也可與虛擬系統(tǒng)平臺和驗證計算平臺一起使用。

驗證計算平臺(Palladium XP)

用戶將發(fā)現(xiàn)該平臺提供具有可擴展容量和性能的周期精確系統(tǒng)驗證(仿真)和加速功能,其中包括硬件/軟件調(diào)試功能。該平臺是開放的,提供快速啟動和周轉(zhuǎn)時間,并提供低功耗驗證和分析以及度量驅(qū)動的驗證功能。它通過熱插拔、通用調(diào)試、運行時、編譯和驗證IP連接到Incisive Verification Platform。

快速原型制作平臺

基于 FPGA 的快速原型開發(fā)平臺作為一個周期精確的軟件開發(fā)平臺,能夠連接到現(xiàn)實世界的接口以運行詳盡的回歸。它允許向軟件開發(fā)人員分發(fā)多個負擔得起的原型。它是開放的,支持基于標準的 ASIC 流程,并提供高度準確的可擴展啟動和調(diào)試。結(jié)合驗證計算平臺,組合解決方案提供通用編譯流程、SpeedBridge 適配器和強大的調(diào)試功能。

概括

電子和半導體行業(yè)在過去十年中發(fā)生了重大轉(zhuǎn)變,軟件已經(jīng)超越硬件,成為系統(tǒng)開發(fā)成本、進度和風險的主要驅(qū)動因素。

系統(tǒng)集成時間是系統(tǒng)開發(fā)商和系統(tǒng)公司面臨的主要挑戰(zhàn)。

目前市場上的產(chǎn)品是封閉的、分散的和有限的。

為了解決系統(tǒng)開發(fā)成本、進度和風險挑戰(zhàn),需要一套全面的開放、連接和可擴展的硬件/軟件平臺,以加速從一個平臺到另一個平臺的遷移。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21767瀏覽量

604616 -

半導體

+關注

關注

334文章

27563瀏覽量

220396 -

asic

+關注

關注

34文章

1205瀏覽量

120600

發(fā)布評論請先 登錄

相關推薦

AI Agent智能體平臺:如何助力實現(xiàn)從制造到“智造”的飛躍?

智慧園區(qū)一體化管理平臺的功能應用

網(wǎng)約車管理平臺如何實現(xiàn)與一體化導航系統(tǒng)的無縫對接

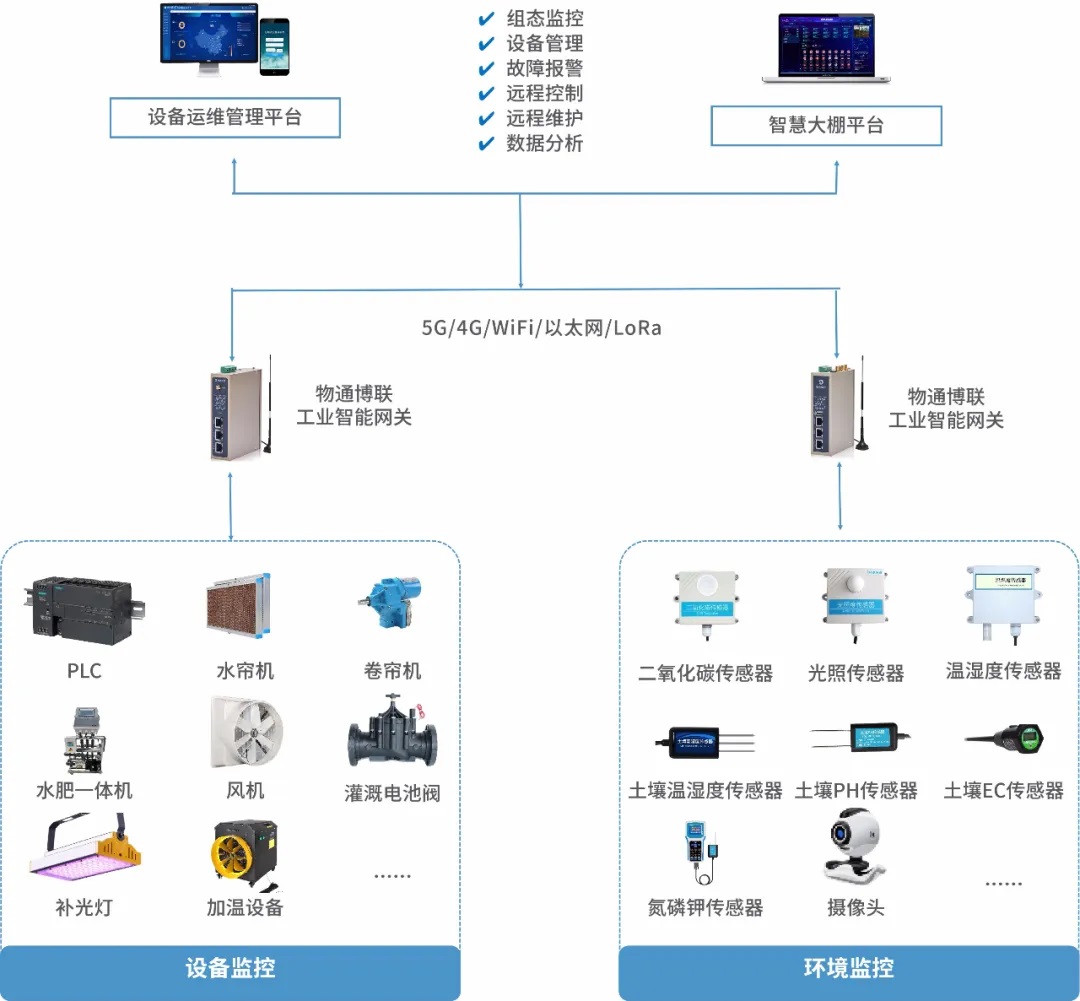

【智慧農(nóng)業(yè)】水肥一體化物聯(lián)網(wǎng)系統(tǒng),助力實現(xiàn)節(jié)能智能灌溉

功率MOSFET體二極管連續(xù)載流能力

基于OpenRTI的空天一體化平臺系統(tǒng)

《嵌入式機電一體化系統(tǒng)設計與實現(xiàn)》讀后感

智慧園區(qū)一體化管理平臺功能

國產(chǎn)麒麟系統(tǒng) NTP網(wǎng)絡時間服務器實現(xiàn)信創(chuàng)平臺自主可控

用于系統(tǒng)實現(xiàn)的平臺連續(xù)體

用于系統(tǒng)實現(xiàn)的平臺連續(xù)體

評論