3電源控制(PWR)

3.1綜述

PWR列舉了芯片內(nèi)部與電源相關(guān)的所有資源,包括內(nèi)部的電源電壓調(diào)節(jié)器、可編程的電源電壓監(jiān)測(cè)器、低功耗模式。

3.2特性

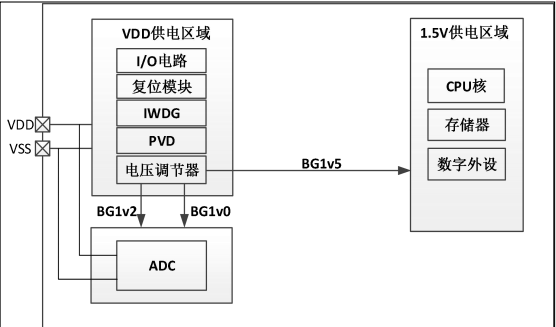

l集成的電源調(diào)節(jié)器,提供3路內(nèi)部電源、均可通過ADC內(nèi)部通道進(jìn)行訪問:

uBG1v5 1.5V精度5%

uBG1v2 1.2V精度5%

uBG1v0 1.0V精度0.5%

l多擋位、支持復(fù)位或中斷的可編程電源電壓檢測(cè)器

l在低功耗模式下,提供兩種低功耗模式:

u睡眠模式

u深度睡眠模式

l深度睡眠下、典型功耗僅為0.8uA

3.3電源調(diào)節(jié)器

PT32x00x支持在超寬電壓范圍內(nèi)工作、工作電壓(VDD)詳見《PT32x00x數(shù)據(jù)手冊(cè)》。通過內(nèi)置的電源調(diào)節(jié)器提供內(nèi)部所需的 1.5V電源BG1v5、1.2V參考電源BG1v2以及1.0V參考電源BG1v0。所有的內(nèi)部電源均可通過ADC內(nèi)部通道進(jìn)行訪問、詳見ADC(控制寄存器ADC_CR)的”CHS”位描述。

3.3.1電源調(diào)節(jié)器

復(fù)位后電源調(diào)節(jié)器總是使能的。根據(jù)系統(tǒng)運(yùn)行狀態(tài)、它以 2種不同的模式工作。

1.運(yùn)行模式:調(diào)節(jié)器以正常功耗模式提供BG1v5、BG1v2、BG1v0三路電源;BG1v5作為核 心電源共給內(nèi)部CPU、存儲(chǔ)器和數(shù)字外設(shè),并且與BG1v2、BG1v0一起接入ADC的內(nèi)部模擬通道中.

2.低功耗模式:提供睡眠和深度睡眠兩種低功耗模式,電源調(diào)節(jié)器將遞進(jìn)的關(guān)閉片內(nèi)電源、時(shí)鐘、外設(shè),以使系統(tǒng)功耗大大降低。

3.3.2電源復(fù)位條件

PT32x00x內(nèi)部有一個(gè)完整的上電復(fù)位(PUR)和掉電復(fù)位(PDR)電路,當(dāng)VDD電壓達(dá)到工作電壓時(shí)系統(tǒng)就能正常工作。 當(dāng)VDD低于指定的限位電壓VPUR/VPDR時(shí),系統(tǒng)保持為復(fù)位狀態(tài)。

3.3.3可編程的電源電壓監(jiān)測(cè)器(PVD)

用戶可以利用PVD對(duì)VDD電壓進(jìn)行監(jiān)測(cè),(電源電壓監(jiān)測(cè)器配置寄存器PWR_PVDR)中的”PLS”位用于設(shè)定PVD監(jiān)控VDD電壓的閾值。通過將(PWR_PVDR寄存器)中的PVDE位置’1’以使能PVD。

PVD事件支持用戶通過復(fù)位和中斷兩種形式進(jìn)行訪問,其對(duì)應(yīng)的中斷事件在內(nèi)部被連接到 NVIC的第20號(hào)中斷,如果該中斷在系統(tǒng)中斷使

能寄存器ISER中被使能,一旦發(fā)生該事件、NVIC就會(huì)響應(yīng)PVD的中斷請(qǐng)求。PVD事件的觸發(fā)/解除機(jī)制由硬件自動(dòng)控制,當(dāng)VDD下降到”PLS位”所設(shè)定的閾值時(shí),PVD中斷被觸發(fā),當(dāng)VDD上升到PVDUV時(shí),PVD中斷被解除。這一特性可用于用于執(zhí)行緊急關(guān)閉任務(wù)。

3.4低功耗模式

系統(tǒng)或電源復(fù)位以后,系統(tǒng)處于運(yùn)行模式。當(dāng)系統(tǒng)無需繼續(xù)運(yùn)行時(shí),可以利用多種低功耗模式來節(jié)省功耗;例如等待某個(gè)外部事件時(shí),用戶可以根據(jù)最低電源消耗、喚醒時(shí)間和可用的喚醒源等條件,選定一個(gè)最佳的低功耗模式。

PT32x00x提供了兩種低功耗模式:

l睡眠狀態(tài)(Cortex?-M0內(nèi)核停止,但包括Cortex-M0核心的外設(shè)在內(nèi)的所有外設(shè),如NVIC、SysTick等仍在運(yùn)行,IFMC無法訪問)

l深度睡眠狀態(tài)(除LSI外的所有時(shí)鐘均已停止工作,相關(guān)的片內(nèi)電源以及外設(shè)被強(qiáng)制關(guān)閉)。此外,在運(yùn)行模式下,還可以通過以下方式降低功耗:

l失能未被使用的時(shí)鐘源

l失能未被使用但已被使能的外設(shè)。

l將不使用的GPIO做內(nèi)部下拉處理

3.4.1進(jìn)入低功耗模式

通過將配置系統(tǒng)控制寄存器(SCR)中的SLP位置’1’以選定系統(tǒng)進(jìn)入低功耗模式時(shí)、系統(tǒng)處于睡眠狀態(tài)還是深度睡眠狀態(tài)。系統(tǒng)進(jìn)入低功耗模式有兩種方法:

l執(zhí)行WFI或WFE指令以進(jìn)入低功耗模式

l將系統(tǒng)控制寄存器(SCR)中的SOE位置’1’,當(dāng)系統(tǒng)從最低優(yōu)先級(jí)的中斷處理程序中退出時(shí),立即進(jìn)入低功耗模式

注意:進(jìn)入低功耗模式前,應(yīng)該將所有未使用到的管腳配置為下拉輸入,并清除所有管腳的復(fù)用功能可使系統(tǒng)功耗得到最大優(yōu)化。

3.4.2睡眠狀態(tài)

表3-1羅列了系統(tǒng)處于睡眠狀態(tài)時(shí)、片內(nèi)資源的工作狀態(tài)。如需優(yōu)化功耗、在進(jìn)入睡眠狀態(tài)前,用戶可手動(dòng)關(guān)閉無需在低功耗模式下工作的外設(shè)以降低功耗。

3.4.3深度睡眠狀態(tài)

表3-1羅列了系統(tǒng)處于深度睡眠狀態(tài)時(shí)、片內(nèi)資源的工作狀態(tài)。在深度睡眠狀態(tài)下,只有 LSI時(shí)鐘掛載的外設(shè)可以正常運(yùn)行,內(nèi)核的寄存器、內(nèi)存的信息仍保存,程序在喚醒后仍從上一次停止處執(zhí)行;除表 3-1所羅列的在深度睡眠狀態(tài)下被強(qiáng)制關(guān)閉外設(shè)外,其他外設(shè)均不會(huì)被強(qiáng)制關(guān)閉,在運(yùn)行模式下使能的外設(shè)、在進(jìn)入深度睡眠前應(yīng)該手動(dòng)關(guān)閉以避免額外功耗;如需進(jìn)一步的優(yōu)化功耗,可將 LSI時(shí)鐘關(guān)閉,但LSI時(shí)鐘掛載外設(shè)將無法工作,此時(shí)、低功耗

模式的喚醒僅支持外部中斷喚醒。

注意:GPIO外部中斷喚醒深度睡眠時(shí),僅支持雙沿中斷、高電平中斷和低電平中斷。

3.4.4喚醒方式

當(dāng)系統(tǒng)處于低功耗模式時(shí),如果是睡眠狀態(tài),根據(jù)進(jìn)入低功耗模式的指令,有相應(yīng)的喚醒方式:

lWFI指令:任意一個(gè)被NVIC響應(yīng)的外設(shè)中斷都能將系統(tǒng)從睡眠模式喚醒。

lWFE指令:包括所有中斷在內(nèi)、所有內(nèi)核支持的事件特別地、當(dāng)(系統(tǒng)控制寄存器SCR)的”SWC”位為’1’時(shí):所有中斷或事件均可喚醒。

注意:使用WFE喚醒睡眠狀態(tài),需要在(中斷掛起清除寄存器ICPR)中清除相應(yīng)的掛起標(biāo)志。

如果是深度睡眠狀態(tài),根據(jù)進(jìn)入低功耗模式的方法,有相應(yīng)的喚醒方式:

lWFI指令:LSI時(shí)鐘掛載外設(shè)的中斷或者外部中斷

lWFE指令:LSI時(shí)鐘掛載外設(shè)的中斷、外部中斷、復(fù)位事件或調(diào)試模式請(qǐng)求事件特別地、當(dāng)(系統(tǒng)控制寄存器SCR)的”SWC”位為’1’時(shí):LSI時(shí)鐘掛載外設(shè)的中斷、外部中斷、復(fù)位事件或者調(diào)試模式請(qǐng)求事件均可喚醒。

審核編輯:湯梓紅

-

電源控制

+關(guān)注

關(guān)注

2文章

138瀏覽量

26620 -

電源調(diào)節(jié)器

+關(guān)注

關(guān)注

0文章

13瀏覽量

7889 -

PWR

+關(guān)注

關(guān)注

0文章

28瀏覽量

10035

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TMS320x2805x微控制器技術(shù)參考手冊(cè)

TMS320x2806x微控制器技術(shù)參考手冊(cè)

TMS320C6472 12路數(shù)字電源控制器和LDO(8x C6472)的電源參考設(shè)計(jì)

CC3x00電源管理優(yōu)化和措施

MSP430x41x混合信號(hào)微控制器數(shù)據(jù)表

MSP430x43x MSP430x43x1 MSP430x44x混合信號(hào)微控制器數(shù)據(jù)表

TMS320F2833x、TMS320F2823x數(shù)字信號(hào)控制器(DSC)TMS320C2834x Delfino微控制器數(shù)據(jù)表

MSP430x461x1, MSP430x461x混合信號(hào)微控制器數(shù)據(jù)表

MSP430x11x1/MSP430F11x1A混合信號(hào)微控制器數(shù)據(jù)表

MSP430x12x混合信號(hào)微控制器數(shù)據(jù)表

MSP430F15x, MSP430F16x, MSP430F161x混合信號(hào)微控制器數(shù)據(jù)表

MSP430x23x MSP430x24x(1)MSP430x2410混合信號(hào)微控制器數(shù)據(jù)表

MSP430F14x、MSP430F14x1、MSP430F13x混合信號(hào)微控制器數(shù)據(jù)表

TMS320F2833x、TMS320F2823x實(shí)時(shí)微控制器數(shù)據(jù)表

PT32x00x電源控制器簡(jiǎn)介

PT32x00x電源控制器簡(jiǎn)介

評(píng)論