在Hot Chips 2021上,英特爾、AMD、IBM、ARM、英偉達、三星、高通等科技巨頭,Skydio、EdgeQ、Esperanto等初創公司,均對其最新芯片技術做了詳細解讀。

本屆Hot Chips會議上,除了IBM、三星、高通等芯片制造巨頭向世界展示了他們最新一代的芯片以外,還有臺積電分享其最先進的3D封裝技術、新思科技CEO談如何借助AI設計芯片、Cerebras研發出世界上最大的芯片等諸多亮點。

臺積電介紹了SoIC、InFO和CoWoS等臺積電3DFabric技術平臺的封裝技術,公布了CoWoS封裝技術的路線圖,并且展示了為下一代小芯片架構和內存設計做好準備的最新一代CoWoS解決方案,包括先進熱處理和COUPE異構集成技術。

以下為臺積電芯片封裝技術演講PPT:

臺積電 CSoIC、InFO和CoWoS等3DFabric技術

3DFabric概述

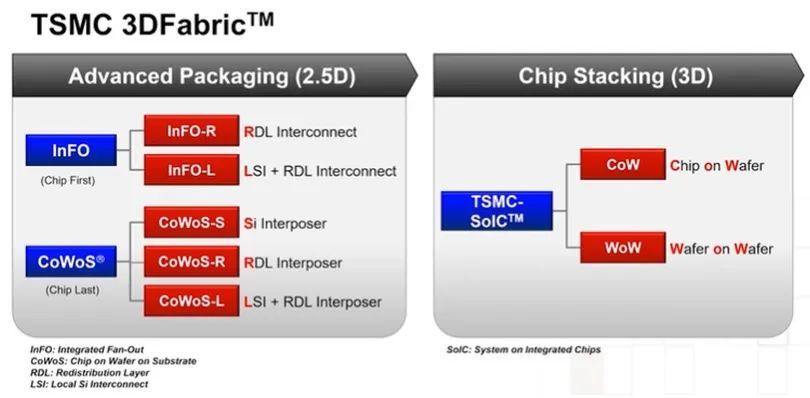

臺積電3D Fabric先進封裝技術涵蓋2.5D和垂直模疊產品,如下圖所示。

集成的FanOut (InFO)封裝利用了由面朝下嵌入的模具組成的重構晶圓,由成型化合物包圍。 在環氧晶片上制備了再分布互連層(RDL)。(InFO- l是指嵌入在InFO包中的模具之間的硅“橋晶片”,用于在RDL金屬化間距上改善模具之間的連接性。) 2.5D CoWoS技術利用microbump連接將芯片(和高帶寬內存堆棧)集成在一個插入器上。最初的CoWoS技術產品(現在的CoWoS- s)使用了一個硅插入器,以及用于RDL制造的相關硅基光刻;通過硅通道(TSV)提供與封裝凸點的連接。硅插入器技術提供了改進的互連密度,這對高信號計數HBM接口至關重要。最近,臺積電提供了一種有機干擾器(CoWos-R),在互連密度和成本之間進行權衡。 3D SoIC產品利用模塊之間的混合粘接提供垂直集成。模具可能以面對面的配置為向導。TSV通過(減薄的)模具提供連接性。

InFO和CoWoS產品已連續多年大批量生產。CoWoS開發中最近的創新涉及將最大硅插入器尺寸擴展到大于最大光罩尺寸,以容納更多模具(尤其是HBM堆棧),將RDL互連拼接在一起。

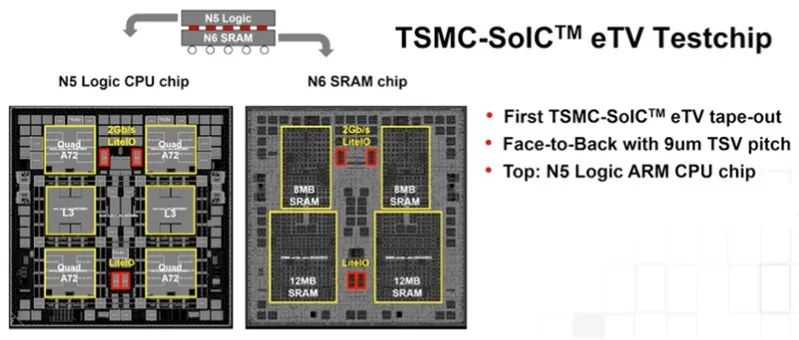

SoIC Testchip

臺積電分享了最近的SoIC資格測試工具的結果,如下所示。

使用的配置是(N5)CPU裸片與(N6)SRAM裸片在面對背拓撲中的垂直接合。(事實上,一家主要的CPU供應商已經預先宣布了使用臺積電的SoIC將垂直“最后一級”SRAM緩存芯片連接到CPU的計劃,該芯片將于2022年第一季度上市。)

SoIC設計流程

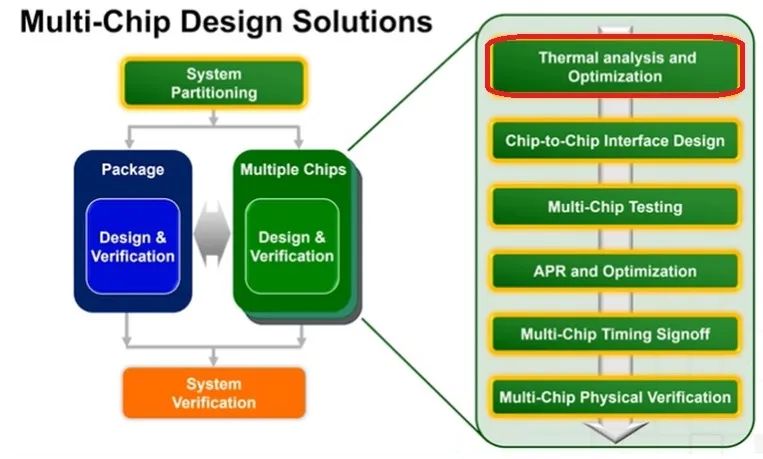

垂直模具集成的高級設計流程如下圖所示:

該流程需要同時關注自上而下的系統劃分為單獨的芯片實施,以及對復合配置中的熱耗散的早期分析,如上所述。

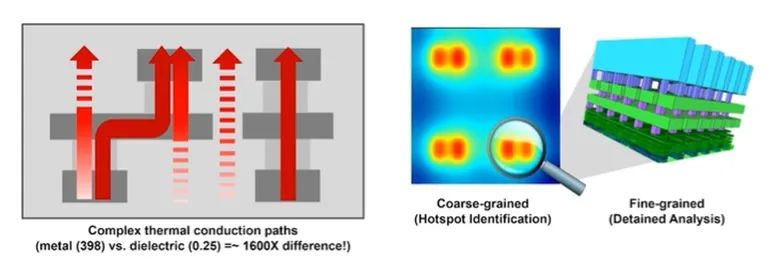

熱分析的討論強調了BEOL PDN和互連的低熱阻路徑與周圍電介質相比的“chimney”性質,如上所示。具體而言,臺積電與EDA供應商合作提高SoIC模型離散化技術的準確性,在最初通過粗網格分析確定的特定“熱點”區域應用更詳細的網格。 臺積電還提出了一種方法,將熱分析結果納入SoIC靜態時序分析降額因子的計算。就像片上變化(OCV)依賴于(時鐘和數據)時序路徑所跨越的距離一樣,SoIC路徑的熱梯度也是一個額外的降額因素。臺積電報告說,一個路徑的模上溫度梯度通常為~5-10C,一個小的平滑降額溫度時間裕度應該足夠了。對于SoIC路徑,~20-30C的大梯度是可行的。對于溫差較小的路徑,覆蓋此范圍的平坦降額將過于悲觀——應使用 SoIC 熱分析的結果來計算降額因子。

SoIC測試

IEEE 1838標準化工作與模對模接口測試(link)的定義有關。 與用于在印刷電路板上進行封裝到封裝測試的芯片上邊界掃描鏈的IEEE 1149 標準非常相似,該標準定義了每個芯片上用于堆棧后測試的控制和數據信號端口。該標準的主要重點是驗證在SoIC組裝過程中引入的面對面鍵合和TSV的有效性。 對于SoIC芯片之間的低速I/O,這個定義已經足夠了,但是對于高速I/O接口,需要更廣泛的BIST方法。

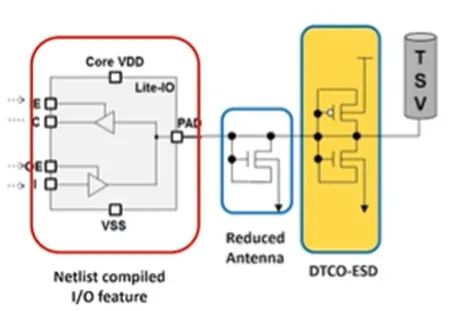

用于SoIC的TSMC Foundation IP–LiteIO

TSMC的庫開發團隊通常為每個硅工藝節點提供通用I/O單元(GPIO)。對于SoIC配置中的die-to-die連接,驅動程序負載較少,臺積電提供了“LiteIO”設計。如下圖所示,LiteIO設計側重于優化布局以減少寄生ESD和天線電容,從而實現更快的裸片之間的數據速率。

EDA啟用

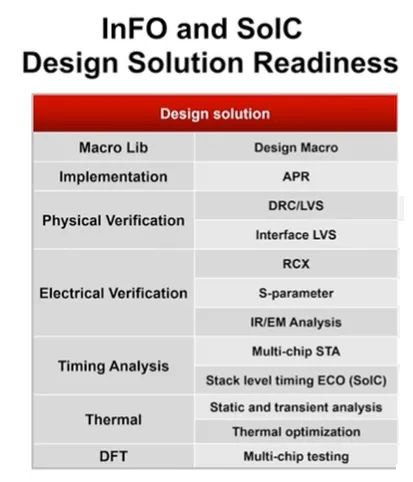

下圖列出了最近與主要EDA供應商合作為InFO和SoIC封裝技術開發的關鍵工具功能。

總結

臺積電繼續大力投資2.5D/3D先進封裝技術開發。最近的主要舉措集中在3D SoIC直接芯片貼裝的方法上——即分區、物理設計、分析。具體來說,早期熱分析是必須的步驟。此外,臺積電還分享了他們的SoIC eTV資質測試芯片的測試結果。2022年將見證3D SoIC設計的快速崛起。

審核編輯 :李倩

-

芯片

+關注

關注

455文章

50817瀏覽量

423680 -

封裝技術

+關注

關注

12文章

549瀏覽量

67991

原文標題:詳解臺積電3DFabric封裝技術

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

臺積電3D Fabric先進封裝技術

臺積電3D Fabric先進封裝技術

評論