1 引言

??

本文通過以高速AD9361芯片為例進行數據接口邏輯代碼的編寫,利用SelectIO IP快速高效完成芯片驅動的生成。

2 AD9361

2.1 芯片簡介

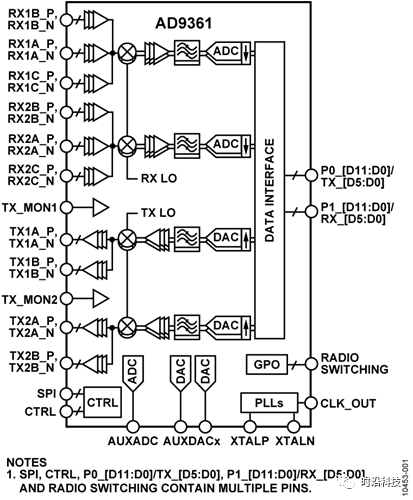

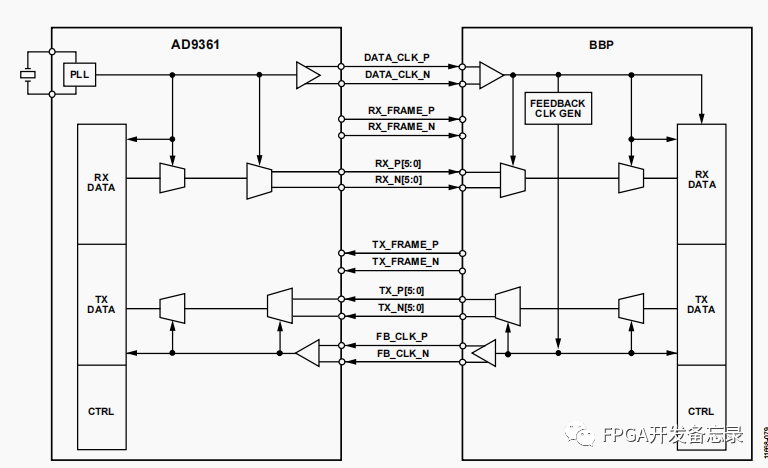

??AD9361是一款面向3G和4G基站應用的高性能、高集成度的射頻(RF)Agile Transceiver捷變收發器。該器件的可編程性和寬帶能力使其成為多種收發器應用的理想選擇。該器件集RF前端與靈活的混合信號基帶部分為一體,集成頻率合成器,為處理器提供可配置數字接口,從而簡化設計導入。AD9361接收器LO工作頻率范圍為70 MHz至6.0 GHz,發射器LO工作頻率范圍為47 MHz至6.0 GHz,涵蓋大部分特許執照和免執照頻段,支持的通道帶寬范圍為200 kHz以下至56 MHz,整體結構圖如圖 1 AD9361整體結構圖所示。

圖 1 AD9361整體結構圖

圖 1 AD9361整體結構圖

?集成12位DAC和ADC的RF2×2收發器 ? TX頻段:47MHz至6.0GHz ? RX頻段:70MHz至6.0GHz ?支持TDD和FDD操作 ?可調諧通道帶寬:<200?kHz至56?MHz ??雙通道接收器:6路差分或12路單端輸入 ??出色的接收器靈敏度,噪聲系數為2?dB?(800?MHz?LO) ??RX增益控制 ??o?實時監控和控制信號用于手動增益 ??o?獨立的自動增益控制 ??雙發射器:4路差分輸出 ??高線性度寬帶發射器 ? o TX EVM:≤?40?dB ? o TX噪聲:≤?157?dBm/Hz本底噪聲 ? o TX監控器:動態范圍≥66?dB,精度=1?dB ??集成式小數N分頻頻率合成器 ??2.4?Hz最大本振(LO)步長 ??多器件同步 ??CMOS/LVDS數字接口

2.2 參數配置

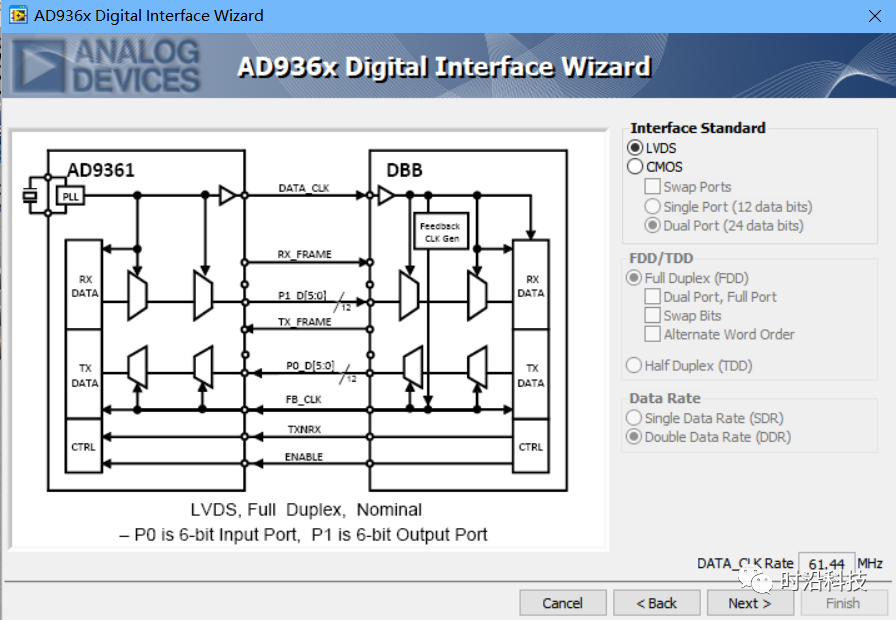

??用戶可以根據自己的需求將數據接口通過SPI配置成LVDS或CMOS接口,也可以還可以選擇FDD或TDD工作方式,以及數據速率可以選擇SDR或DDR。只需要通過配置軟件設置即可,如圖 2 AD9361數據接口配置參數所示,詳細的配置教程見AD936x Evaluation Software 詳細配置。

圖 2 AD9361數據接口配置參數

圖 2 AD9361數據接口配置參數

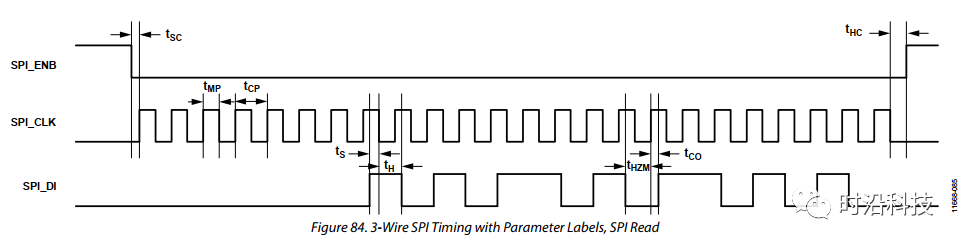

??在進行數據驗證時,也可以使用測試模式,對收發數據進行驗證以保證系統的正確性。另外,還可以對輸入時鐘進行延時調節或者通過SelectIO的delay、delayctrl功能對時鐘信號進行微調,以滿足時序要求。芯片數據時鐘與數據之間的時序可靠性也可以通過芯片內部的延時寄存器0x006、0x007進行條件,以此達到要求,具體的SPI配置寄存器時序如圖 3 AD9361 寄存器配置接口SPI時序所示。此方面不是本文重點,不做展開,更多內容參考官方data sheet。

圖 3 AD9361 寄存器配置接口SPI時序

圖 3 AD9361 寄存器配置接口SPI時序

??本小節使用的數據接口參數:LVDS、FDD、DDR,對應的時序邏輯也是根據該參數進行設計。

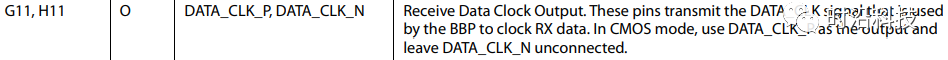

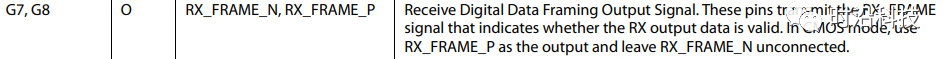

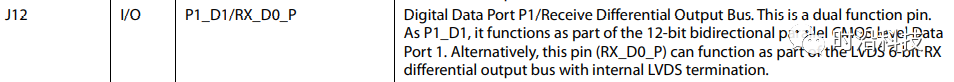

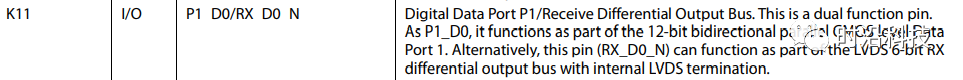

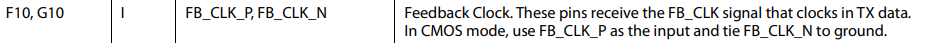

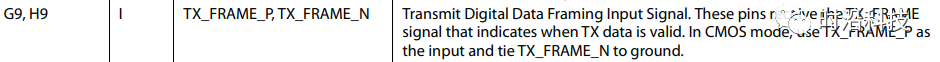

2.3 引腳

RX數據時序接口如下:

TX數據時序接口如下:

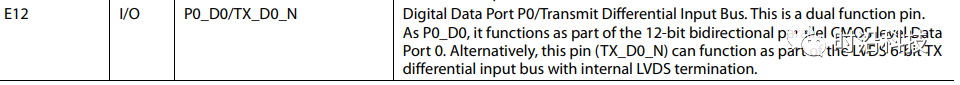

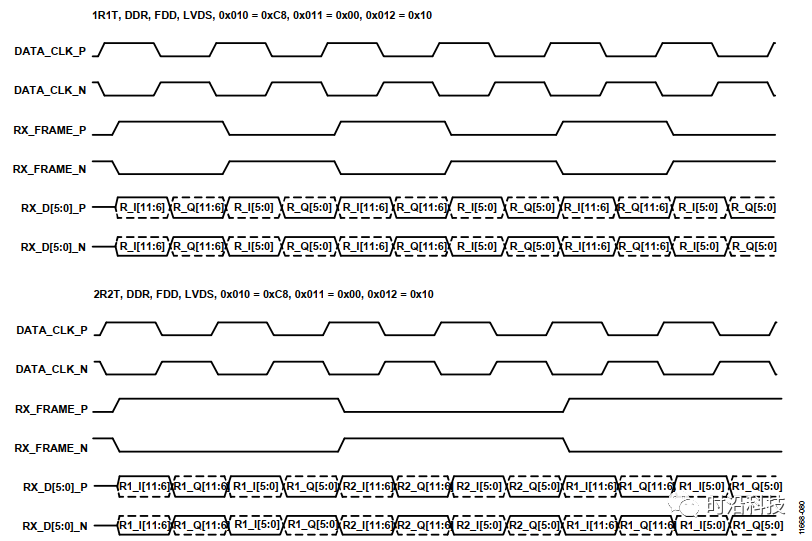

2.4 接口時序

??以下使用的數據接口參數:LVDS、FDD、DDR,根據不同的通道數可以得到不同的數據時序,用戶在解析數據時只要按照對應的結構進行拼接即可。

圖 4 AD9361接收數據路徑

圖 4 AD9361接收數據路徑  圖 5 AD9361發射接口路徑

圖 5 AD9361發射接口路徑

3 參考代碼

3.1 SelectIO配置

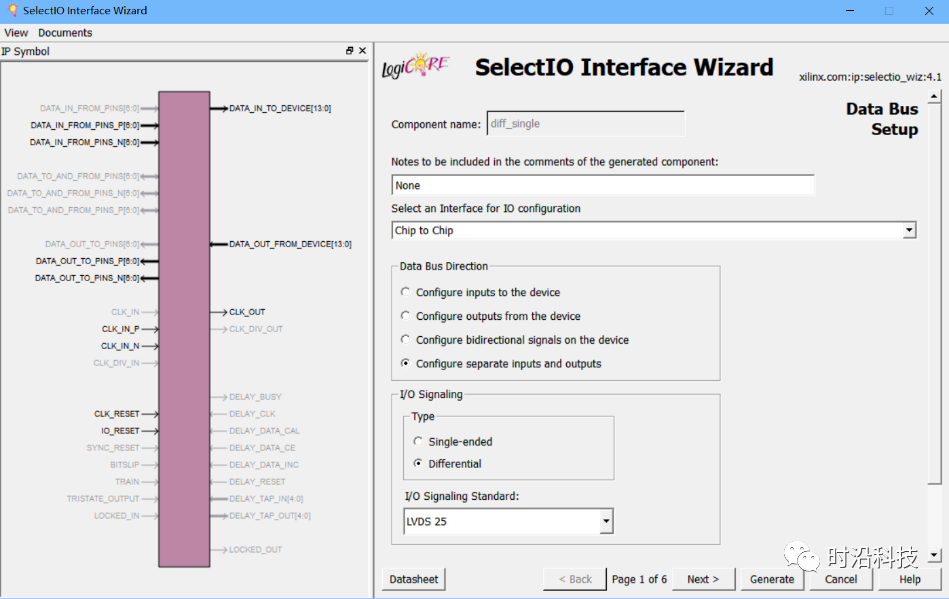

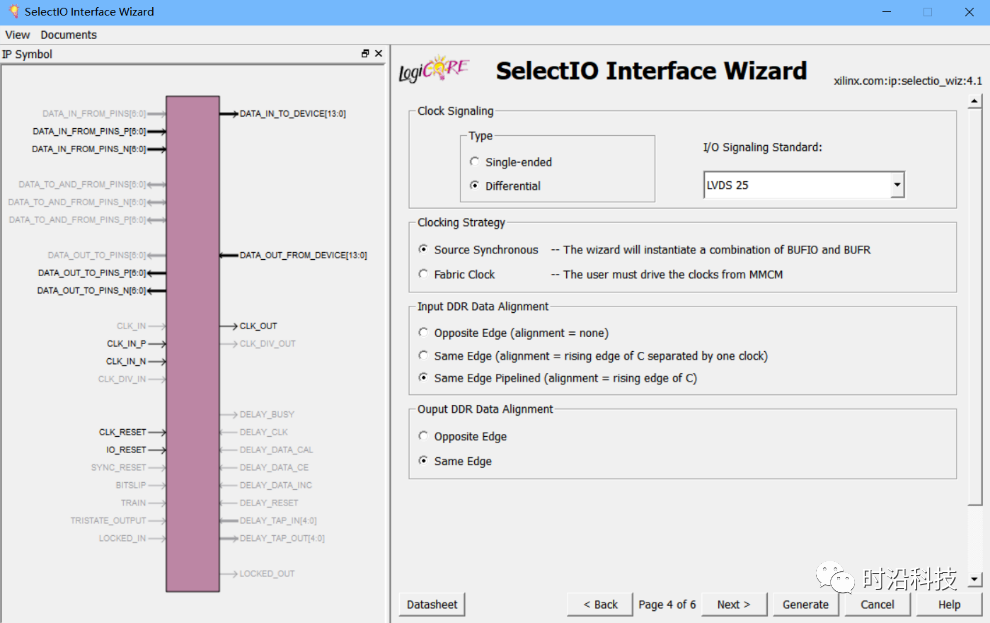

??根據以上對AD9361的了解,就可以輕松的配置SelectIO IP的GUI界面了。芯片既包括發射模塊TX又包括接收模塊RX,所以IO類型選擇chip to chip。

圖 6 SelectIO配置界面1

圖 6 SelectIO配置界面1

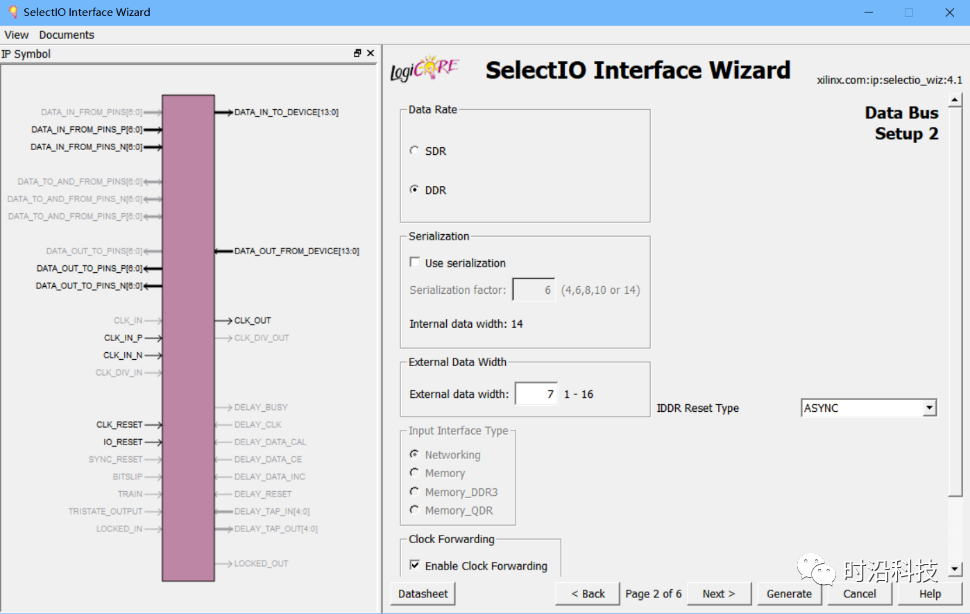

??根據上述參數配置部分,自然就選擇DDR。數據接口包括時鐘CLK、Frame對齊信號與差分數據端Data[05:0],要同時對Frame與Data信號進行時序解析,所以端口寬度設置為7.

圖 7 SelectIO配置界面2

圖 7 SelectIO配置界面2

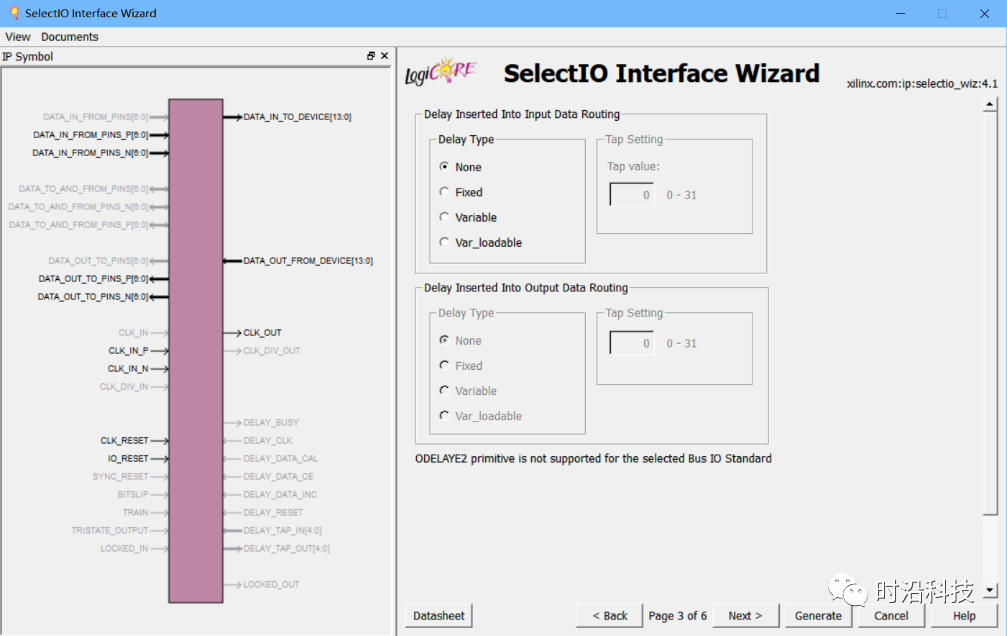

??由于芯片內部寄存器0x006、0x007可以確保時鐘與數據滿足時序要求,所以不需要延時模塊,以節約FPGA邏輯資源。

3.2 數據解析

//------------------------------------------------------------------- //用于將接收時鐘與數據進行單端與差分的變換 //------------------------------------------------------------------- selectio_ipu_selectio_ip( //Fromthesystemintothedevice .DATA_IN_FROM_PINS_P(ad_rx_data_in_p), //從AD接收端接收到的單端數據與標志 .DATA_IN_FROM_PINS_N(ad_rx_data_in_n), //從AD接收端接收到的單端數據與標志 .DATA_IN_TO_DEVICE(ad_rx_data), //將AD接收端接收到的數據與標志轉換為單端數據 //Fromthedeviceouttothesystem .DATA_OUT_FROM_DEVICE(ad_tx_data), //將要發送的DA數據與標志轉換為單端數據 .DATA_OUT_TO_PINS_P(ad_tx_data_out_p), //發送端的單端DA數據與標志 .DATA_OUT_TO_PINS_N(ad_tx_data_out_n), //發送端的單端DA數據與標志 .CLK_TO_PINS_P(ad_fb_clk_p), //將AD接收端的輸入時鐘用于發射時鐘 .CLK_TO_PINS_N(ad_fb_clk_n), //將AD接收端的輸入時鐘用于發射時鐘 .CLK_IN_P(ad_data_clk_p), //AD接收端的單端輸入時鐘 .CLK_IN_N(ad_data_clk_n), //AD接收端的單端輸入時鐘 .CLK_OUT(ad9361_data_clk), //將AD接收端的差分輸入時鐘轉變為單端時鐘 .CLK_RESET(reset), //用于AD輸入時鐘的復位,高有效 .IO_RESET(reset) //用于單端、差分變換的復位,高有效 ); //------------------------------------------------------------------- //發送數據的生成 //------------------------------------------------------------------- assignad_tx0_msb_q=ad_tx0_data[23:18]; assignad_tx0_lsb_q=ad_tx0_data[17:12]; assignad_tx0_msb_i=ad_tx0_data[11:06]; assignad_tx0_lsb_i=ad_tx0_data[05:00]; assignad_tx1_msb_q=ad_tx1_data[23:18]; assignad_tx1_lsb_q=ad_tx1_data[17:12]; assignad_tx1_msb_i=ad_tx1_data[11:06]; assignad_tx1_lsb_i=ad_tx1_data[05:00]; reg[13:0]ad_tx_data; //------------------------------------------------------------------- //選擇要發送的I與Q數據 //------------------------------------------------------------------- always@(posedgead9361_data_clkorposedgereset)begin if(reset) ad_tx_data<=0; ??else?if((ad_tx_frame_reg==0)&&(ad_tx_frame==1)) ???ad_tx_data<={ad_tx_frame,ad_tx0_msb_q,ad_tx_frame,ad_tx0_msb_i}; ??else?if((ad_tx_frame_reg==1)&&(ad_tx_frame==1)) ???ad_tx_data<={ad_tx_frame,ad_tx0_lsb_q,ad_tx_frame,ad_tx0_lsb_i}; ??else?if((ad_tx_frame_reg==1)&&(ad_tx_frame==0)) ???ad_tx_data<={ad_tx_frame,ad_tx1_msb_q,ad_tx_frame,ad_tx1_msb_i}; ??else?if((ad_tx_frame_reg==0)&&(ad_tx_frame==0)) ???ad_tx_data<={ad_tx_frame,ad_tx1_lsb_q,ad_tx_frame,ad_tx1_lsb_i};?? ?end? //------------------------------------------------------------------- //選擇接收的I與Q數據 //------------------------------------------------------------------- ?always?@(posedge?ad9361_data_clk?or?posedge?reset)?begin ??if(reset)?begin ???ad_rx0_msb_i<=0; ???ad_rx0_msb_q<=0; ???ad_rx0_lsb_i<=0; ???ad_rx0_lsb_q<=0; ???ad_rx1_msb_i<=0; ???ad_rx1_msb_q<=0; ???ad_rx1_lsb_i<=0; ???ad_rx1_lsb_q<=0;??? ??end ??else?if((ad_rx_frame_reg==0)&&(ad_rx_frame==1))?begin ???ad_rx0_msb_i<=ad_rx_data[05:0]; ???ad_rx0_msb_q<=ad_rx_data[12:7]; ??end ??else?if((ad_rx_frame_reg==1)&&(ad_rx_frame==1))?begin ???ad_rx0_lsb_i<=ad_rx_data[05:0]; ???ad_rx0_lsb_q<=ad_rx_data[12:7]; ??end ??else?if((ad_rx_frame_reg==1)&&(ad_rx_frame==0))?begin ???ad_rx1_msb_i<=ad_rx_data[05:0]; ???ad_rx1_msb_q<=ad_rx_data[12:7]; ??end ??else?if((ad_rx_frame_reg==0)&&(ad_rx_frame==0))?begin ???ad_rx1_lsb_i<=ad_rx_data[05:0]; ???ad_rx1_lsb_q<=ad_rx_data[12:7]; ??end? ?end ? ?wire?[23:0]??ad_rx0_fifo_data; ?wire?[23:0]??ad_rx1_fifo_data; ?assign?ad_rx0_fifo_data={ad_rx0_msb_q,ad_rx0_lsb_q,ad_rx0_msb_i,ad_rx0_lsb_i}; ?assign?ad_rx1_fifo_data={ad_rx1_msb_q,ad_rx1_lsb_q,ad_rx1_msb_i,ad_rx1_lsb_i};

原文標題:FPGA實現AD9361數據接口邏輯

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1638文章

21857瀏覽量

609734 -

芯片

+關注

關注

459文章

51726瀏覽量

430965 -

數據接口

+關注

關注

1文章

80瀏覽量

18001 -

代碼

+關注

關注

30文章

4862瀏覽量

69726 -

AD9361

+關注

關注

8文章

35瀏覽量

37435

發布評論請先 登錄

相關推薦

評論