近年來先進封裝(Advanced Package)成為了高性能運算客制化芯片(High Performance Computing ASIC)成功與否的關(guān)鍵。隨著市場需求不斷升級,世芯電子致力于投資先進封裝關(guān)鍵技術(shù),將其更有效率的整合到芯片設(shè)計供應(yīng)鏈中, 以實現(xiàn)全客制化的合作模式。

隨著高階應(yīng)用市場的發(fā)展,科技系統(tǒng)大廠開始必須透過軟硬體系統(tǒng)整合來實現(xiàn)創(chuàng)新,使其產(chǎn)品達到更強大的功能與強化的系統(tǒng)效能。也因為如此,現(xiàn)今各個系統(tǒng)大廠與OEM對客制化芯片(ASIC)的需求呈現(xiàn)高度成長。特別是在高性能運算系統(tǒng)芯片(SoC)領(lǐng)域,IC設(shè)計本身非常復(fù)雜且成本已經(jīng)相當(dāng)昂貴,如果再加上后端設(shè)計包含封裝,測試,供應(yīng)鏈整合等等會是更大規(guī)模的投資。在成本及效率的考慮下,各大企業(yè)選擇與專業(yè)高階ASIC設(shè)計公司合作已是必然的趨勢。

高性能運算IC的成功關(guān)鍵取決于先進封裝技術(shù)

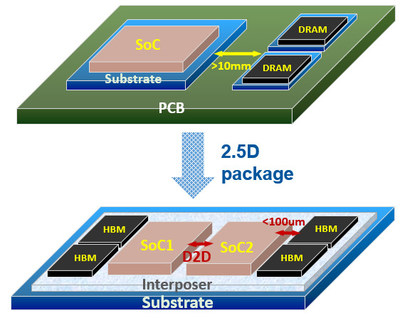

高階應(yīng)用市場的高性能運算系統(tǒng)芯片成長強勁,伴隨的是前所未有對先進封裝技術(shù)的依賴。由臺積電所研發(fā)的先進封裝技術(shù)CoWoS 及InFO 2.5D/3D封裝對于成功部署當(dāng)今的HPC SoC ASIC至關(guān)重要。CoWoS封裝可以實現(xiàn)把數(shù)個小芯片(Chiplets)黏合在同一中介片(Interposer)同一封裝基板(Substrate)上,以達到“系統(tǒng)級微縮”的境界,大大提升了SoC之間互連密度和性能,是科技史上的一大突破。

另一先進封裝技術(shù)為多芯片模組(Multi-Chip-Module,簡稱MCM)也是類似概念。與傳統(tǒng)封裝不同,先進封裝需要與電路設(shè)計做更多的結(jié)合,加上必須整合產(chǎn)業(yè)的中下游,對設(shè)計整合能力是一大挑戰(zhàn),也是門檻相當(dāng)高的投資。

先進封裝CoWoS, 2.5D Package - 世芯的高性能運算設(shè)計解決方案能無縫整合系統(tǒng)芯片設(shè)計和先進封裝技術(shù), 進而提升互連密度和性能

世芯看到了高性能系統(tǒng)運算ASIC設(shè)計服務(wù)市場對先進封裝需求的急速成長。“如今,各個科技大廠正大量投資于IC前端設(shè)計,以求跟自家產(chǎn)品完美結(jié)合以最大程度區(qū)別市場差異性及市場領(lǐng)先地位。他們此刻需要的是與杰出的專業(yè)ASIC設(shè)計服務(wù)公司合作,才不會讓他們的大量投資及時間成本付諸流水。”世芯電子總裁兼首席執(zhí)行官沈翔霖說到。

世芯是客戶在高性能運算市場客制化芯片的重要伙伴

世芯電子提供的高性能運算設(shè)計方案能無縫整合高性能運算系統(tǒng)芯片設(shè)計和先進封裝技術(shù)。世芯的MCM 于2020年量產(chǎn),CoWoS 于2021 年量產(chǎn)。現(xiàn)有大尺寸系統(tǒng)芯片幾乎是光罩的最大尺寸(Reticle Size,800mm2)。

中介片(Interposer)設(shè)計為 3~4倍于光罩最大尺寸(3~4X Reticle Size),而先進封裝尺寸甚至達到 85x85mm2是現(xiàn)有封裝技術(shù)的極限。這都是經(jīng)過多項客戶產(chǎn)品成功量產(chǎn)驗證過的。也證明了世芯的高性能運算設(shè)計方案滿足高性能運算IC市場需求,是其取得市場領(lǐng)先地位的重要關(guān)鍵。

審核編輯 :李倩

-

IC

+關(guān)注

關(guān)注

36文章

5960瀏覽量

175769 -

電路設(shè)計

+關(guān)注

關(guān)注

6678文章

2455瀏覽量

204630 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

550瀏覽量

67998

原文標題:世芯電子提高先進封裝研發(fā)投資以滿足高性能運算IC市場需求

文章出處:【微信號:gh_81c202debbd4,微信公眾號:世芯電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

聯(lián)電獲得高通高性能計算先進封裝大單

先進封裝技術(shù)推動半導(dǎo)體行業(yè)繼續(xù)前行的關(guān)鍵力量

高速點焊工藝中先進控制電源的關(guān)鍵技術(shù)探究與應(yīng)用

分流電阻的大小取決于什么因素,分流電阻的大小如何確定

組合邏輯電路輸出狀態(tài)取決于哪些因素

先進封裝與傳統(tǒng)封裝的區(qū)別

極化繼電器是狀態(tài)改變取決于什么

先進封裝技術(shù)綜述

數(shù)控機床的性能很大程度上取決于什么的性能

先進IC載板市場的變革與機遇

全球先進IC載板市場分析

濾波器的頻率范圍取決于什么因素?

高性能運算IC的成功關(guān)鍵取決于先進封裝技術(shù)

高性能運算IC的成功關(guān)鍵取決于先進封裝技術(shù)

評論