隨著時間的推移,該行業已轉向虛擬化功能和軟件定義網絡 (SDN),以便在數據中心和網絡中的各種硬件平臺上實現靈活部署。軟件現在必須能夠跨多個軟件和硬件環境進行轉移,以既具有成本效益又提供所需的靈活性以滿足一系列不斷變化的性能需求。

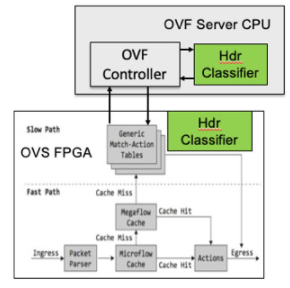

Open vSwitch (OVS) 是一個高級功能的例子,它曾經是硬件,但通過虛擬化交換功能帶來了部署的靈活性。在此過程中,一些更適合硬件的功能(如數據包解析和分類)已成為瓶頸。尋找使用硬件加速這些虛擬功能同時保持部署靈活性的方法可以大大提高吞吐量并減少延遲。

帶有 FPGA 或專用芯片的 SmartNIC 正在成為一種硬件和軟件混合的解決方案。為了與軟件功能一起發揮作用,關鍵的硬件功能必須虛擬化。

目前在使用 FPGA 加速虛擬環境時存在幾個挑戰,主要歸因于存儲容量、內存的聚合隨機訪問性能和內存訪問延遲:

第一個挑戰在于難以支持需要大量內存并且需要以真正隨機訪問模式訪問的系統。即使現在的 FPGA 支持更大的芯片資源,甚至那些支持高帶寬內存 (HBM) 的 FPGA,問題也變成了需要多少這些資源來支持高速隨機訪問要求。甚至還有第三種常見情況,即使用片外 QDR SRAM 來增加片上資源,它使用許多 I/O 資源來實現相對較低的密度。問題是,如何僅使用一個設備替換多個具有相同或更多內存的 QDR 設備?

第二個挑戰可以概括為投資利用率或可移植性。許多需要數據包分類或 DPI 等功能的 最終用戶客戶在軟件方面投入了大量的開發工作。如果這些客戶需要中期性能提升或擴大產品供應范圍,除了可能重新設計相關硬件外,還需要大量的軟件返工。

虛擬加速器引擎方法

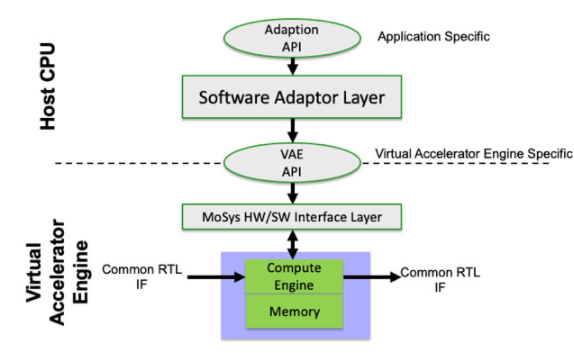

虛擬加速器引擎 (VAE) 方法允許用戶設計 API 和 RTL 模塊接口,將軟件和系統設計的其余部分與底層實現隔離開來。這可以升級以支持性能提升,同時節省軟件開發和調試的工作量。此外,虛擬加速器方法在 OVS 等分層解決方案中表現良好,這些解決方案具有“回退”到較慢路徑的快速路徑,所有這些都使用相同的編程模型來管理表。

目前,有多種方法可以加速基于 FPGA 的設計。當客戶特別基于 FPGA 設計系統時,有兩種方法可以解決最常見的瓶頸挑戰。

該策略一直是定義一個通用 API 函數接口,該接口由一系列具有可擴展性能的硬件環境支持。由于 API 有不同的性能規格可供選擇,因此不必知道硬件是什么。因此,從本質上講,它本質上是一種虛擬硬件解決方案。

在這里,硬件不會驅動軟件決策。定義了軟件性能,選擇了硬件環境。因此:軟件定義,硬件加速。

由于軟件系統設計是在 API 級別使用未選擇的硬件環境執行的,因此這些解決方案稱為虛擬加速器引擎。這允許系統在一系列硬件平臺選項上執行這個軟件定義的功能,每個選項都可以提供不同的性能點。

虛擬加速器引擎的主要優勢在于需要通過使用通用 API 來保護軟件投資的應用程序,以便在許多不同的硬件環境中實現可傳輸性或性能擴展。通過設計通用 API,系統設計人員可以將其無縫移植到一系列性能平臺上。

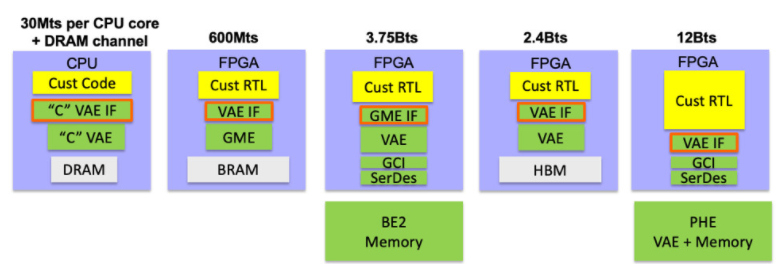

可能的 VAE 平臺

下圖描述了 VAE 的可擴展硬件環境,該環境將執行通用 API 和模塊接口。通過從低端、更具成本效益的硬件環境遷移到性能驅動、硬件定義的系統,一個常見的應用程序可以體驗高達 400 倍的性能提升。每個的基本性能取決于底層內存在總的聚合隨機讀取和寫入方面的能力。

這種靈活性允許系統設計人員選擇實施適當的 VAE 平臺來實現所需的系統性能。

許多市場正在轉向軟件可移植的世界。雖然這在云計算中很常見,但在較低級別的系統功能中并不常見。

虛擬加速器引擎:軟件 + 固件 + 硬件

虛擬加速器引擎被定義為在系統功能級別提供縮放加速。通用 API 與硬件無關。它可以在未連接到專用 IC 的 CPU 或 FPGA 或連接到加速器 IC 的 FPGA 上運行,例如 MoSys 加速器 IC 系列,包括帶寬引擎或具有內存計算能力的可編程超高速引擎。

虛擬加速器引擎旨在支持諸如“數據包分類”之類的功能平臺。它是“虛擬的”,因為它是一種抽象功能,可以是獨立軟件、FPGA RTL 或基于嵌入式固件的。

使用 MoSys 的通用軟件接口 (API) 和跨多個硬件環境的 RTL 模塊接口,系統設計人員可以重用內部開發的軟件代碼來調整所需的性能。此外,所有基于 FPGA 的 VAE 都使用允許硬件可移植性的通用 RTL。具有通用 API 的 VAE 可以在 CPU 或通用 RTL 模塊接口上運行,其中 FGPA 未連接到 MoSys IC 或 FPGA 連接到 MoSys 加速器引擎 IC。

軟件定義系統的時代

隨著軟件可移植性的發展,不僅在云中而且在獨立系統中,設計人員需要快速進入具有不同性能/價格點的新系統設計。這就要求系統設計人員將應用程序放入具有不同性能級別的硬件環境中,從而針對每個平臺進行設計。

VAE 允許工程師在系統/應用程序級別進行思考,而無需擔心“我的硬件做什么?” 借助“功能平臺”,這些工程師可以先開發軟件定義的系統,然后再從一系列性能環境中選擇硬件。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21767瀏覽量

604615 -

cpu

+關注

關注

68文章

10888瀏覽量

212362 -

接口

+關注

關注

33文章

8664瀏覽量

151509

發布評論請先 登錄

相關推薦

RAID 5 在虛擬化環境中的應用

如何實現軟件的emulate功能 emulation和虛擬化的區別是什么

深入KVM虛擬化之構建高效、可擴展的虛擬化環境

虛擬化數據恢復—XenServer虛擬機數據恢復案例

emc虛擬化技術的應用場景

華納云:OpenStack是虛擬化管理平臺嗎?其工作原理是什么?

什么是虛擬機?什么是虛擬化?

虛擬化數據恢復—XenServer虛擬化平臺數據恢復案例

存儲虛擬化有哪些常見類型?有什么優點?

虛擬化軟件棧有哪些防御措施

美格智能LXC容器化解決方案,輕松玩轉多系統虛擬化

使用虛擬化硬件功能加速虛擬化環境

使用虛擬化硬件功能加速虛擬化環境

評論