2021 年嵌入式處理器報告:隨著晶體管擴展的可靠每瓦性能增益接近尾聲,未來幾代處理器將如何訪問有效執行要求苛刻的工作負載所需的計算?我的答案來自異構 SoC 上的并行處理。

“我們已經在 7 nm 上工作了很長時間,在那段時間里,我們不僅看到了摩爾定律的終結,而且還看到了阿姆達爾定律和丹納德縮放的終結,”硅營銷總監 Manuel Uhm 說在賽靈思。“這意味著,如果我們所做的只是采用 FPGA 并將這些晶體管從我們之前的節點(即 16 納米)縮小到 7 納米,然后收工,許多試圖遷移完全相同的設計的客戶可能很可能最終得到的設計坦率地說沒有任何性能提升,實際上可能會增加功耗。

“很明顯,這是完全錯誤的方式。”

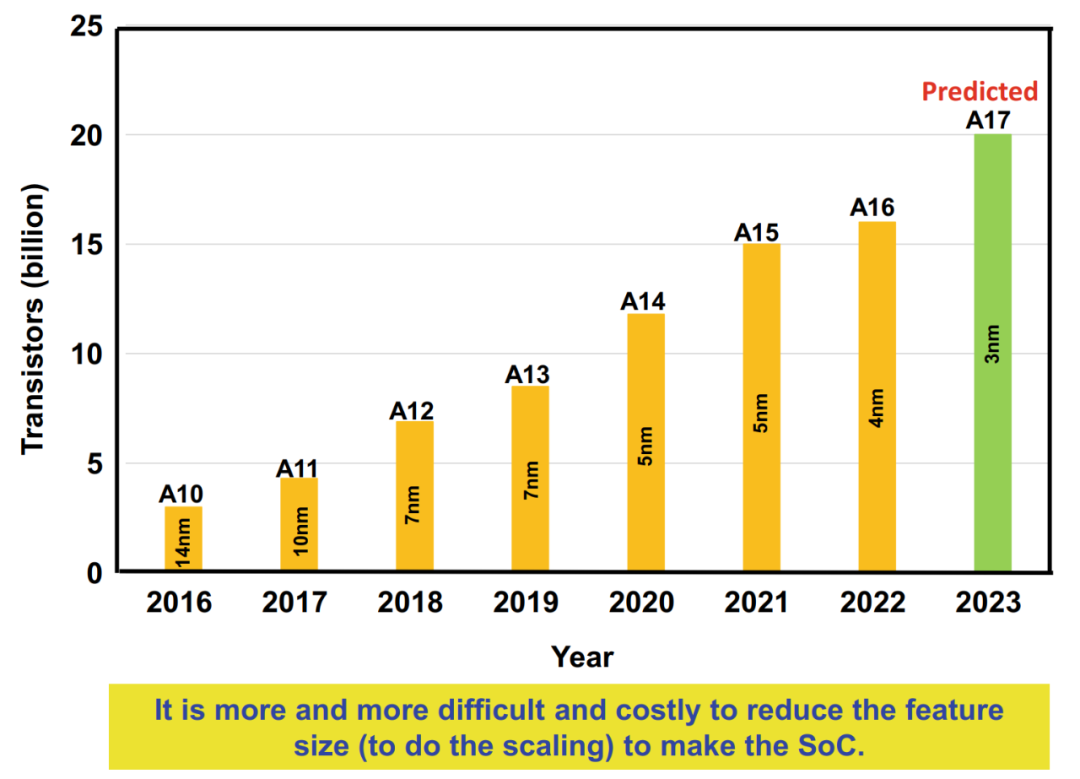

需要明確的是,將硅晶體管縮小到 7 nm 以下并非不可能;5nm 器件已經投入生產。這是因為底層金屬沒有更快地運行,并且電流泄漏正在上升。

同時,在另一個方向上,傳統的多核設備自身也遇到了擴展限制。當然,這些并行處理器在歷史上一直是同質的,“而現實情況是,沒有一個處理器架構可以優化地完成每項任務,”Uhm 爭辯道。“不是 FPGA,不是 CPU,不是 GPU。”

這并不是說并行性在處理現代應用程序呈現的復雜處理任務方面沒有優勢。事實上,除了摩爾定律和丹納德定標之外,并行計算可能是我們在高性能計算 (HPC) 和其他要求苛刻的用例中的最佳選擇。

是的,我們仍然需要并行處理。但屬于異類。

異構處理:不僅適用于數據中心

如前所述,異構并行處理技術的前沿是對高端應用中性能壁壘的回應。但這些架構在嵌入式計算環境中也變得越來越普遍。

VDC Research 高級分析師 Dan Mandell 指出,雖然“許多異構處理架構確實專注于高端應用,特別是數據中心和 HPC……FPGA SoC 和其他異構加速芯片的小型化是最重要的。讓 Microsemi 和 Xilinx 等公司將更多此類設備帶入智能邊緣基礎設施,如邊緣/工業服務器和物聯網網關。”

根據 Mandell 的說法,嵌入式市場中通用異構計算平臺的一個關鍵驅動因素“是當今 OEM 和其他廠商對硬件架構的承諾猶豫不決。” 他說,這種猶豫是專用加速芯片快速發展的產物,以及未來幾年邊緣軟件和人工智能生態系統將產生的框架和工作負載的不確定性。

他預計所有這些情況都會“對未來的半導體采購產生重大影響”,以及芯片供應商如何處理他們的處理器路線圖。

“當今大多數 FPGA SoC 的價格和功率范圍將迫使供應商最初專注于相對高端、資源豐富的嵌入式和邊緣應用,”Mandell 假設。“然而,正在積極努力使 FPGA SoC ‘尺寸不可知’,最終甚至支持電池供電的連接設備。”

因此,隨著異構并行處理變得越來越多常見的問題是,嵌入式工程師是否應該為系統設計的范式轉變做好準備?英偉達副總裁兼嵌入式與邊緣計算總經理 Deepu Talla 不這么認為。

“如果你仔細想想,嵌入式處理器總是使用加速器,”Talla 說。“即使在 20 年前,也有 Arm CPU,有 DSP,然后在特定硬件中完成視頻編碼/解碼,對吧?它們在某種意義上是固定功能的,但它們都在并行處理事物。

“你需要這樣做的原因是成本、功率、尺寸,”他繼續說道。“并行處理器的效率比 CPU 高出幾個數量級。”

Nvidia 的 Xavier SoC 是其 Jetson Xavier 嵌入式平臺的核心設備,以及公司將于 2021 年底或 2022 年推出的下一代 Orin 架構,均配備 GPU、Arm CPU、深度學習加速器、視覺加速器、編碼器/解碼器和其他專門的處理模塊(圖 3)。

【圖3 | Nvidia Xavier SoC 配備了基于 Arm 的 Carmel CPU、Volta GPU、深度學習和視覺加速器以及其他可以并行處理工作負載的固定功能計算模塊。]

然而,隨著高級異構 SoC 變得越來越普遍,嵌入式開發人員可以期待的一個變化是使用片上網絡 (NoC) 互連,在過去十年中,這種互連從傳統的片上總線(如 AMBA 接口)發展而來。這提供了“控制如何連接 CPU、GPU、視頻編碼器、深度學習加速器、顯示處理器、相機處理器、安全處理器,所有這些東西,”Talla 說。

NoC 有助于加速和優化跨 SoC 的塊到塊的數據流,這有助于盡可能高效地執行工作負載。例如,NXP 在其多功能 i.MX SoC 系列中利用了 NoC 和傳統總線架構。

“異構計算是我們多年來一直在實施的東西。NXP Semiconductors, Inc. 邊緣處理業務和技術戰略主管 Gowrishankar Chindalore 博士說,我相信現在是我們真正開始達到最佳使用點的地方。機器學習,因為我們今天使用的是 CPU、GPU、DSP 和神經處理單元 (NPU)。

“但優化的一部分,不僅僅是計算元素。系統周圍的一切都需要發生,”他繼續說道。“因此,除了異構計算之外,我們專注于提高效率的地方,正在關注芯片分割流水線、視頻流水線、圖形流水線中整個流程的浪費。

“因為我們做得越多,我們在性能方面獲得的效率就越高,顯然,用于執行相同功能的能量就越少,”他補充道。

(編者按:閱讀《異構多核實現十倍嵌入式內存性能的三種方法》)

走向異質世界

Mandell引用 VDC Research 的 2020 年物聯網、嵌入式和移動處理器技術報告,預計嵌入式 SoC 的全球市場將“在未來幾年繼續超過 MPU、MCU、GPU 等分立半導體的商業市場”,因為 OEM 看起來整合計算資源和多芯片實現。他說,從長遠來看,對工作負載加速和處理器優化的需求只會“推動進一步增長”。

與此同時,我們衡量性能和功耗的方式將不得不改變。正如 The Linley Group 的高級分析師 Mike Demler 在其公司的《深度學習處理器指南》中所說,即使是像 TOPS/W 這樣的以 AI 為中心的新基準測試也“具有誤導性,因為真正的 AI 工作負載從未達到接近 100% 的利用率。”

他說,我們將不得不用“一個真實的工作負載,比如 Bert NLP 模型,而不是一個基于理論的、基于架構的規范”來衡量諸如電源效率之類的東西。

但是,孤立地測量處理器復合體是否有意義?它真的很重要嗎?一如既往,重點將放在它在您的系統環境中提供的內容上。

“在使用每個流程節點之前,就像‘哦,太好了。我得到兩倍的性能,一半的功耗!‘”Uhm 說。“那些日子已經一去不復返了。那些日子對每個人來說都已經一去不復返了。在 7 nm 時,這些晶體管現在開始泄漏。你只會遇到其他類型的問題在許多情況下,我們認為這是無法克服的。

“因此,在意識到這一點后,我們現在正在研究系統級問題,”他繼續說道,“我們將所有這些東西放在一起,了解所有這些權衡,并確保我們能夠涵蓋以允許滿足性能和功率預算的方式進行盡可能多的處理。再說一次,這些不再是容易的事情了。我們意識到我們將能夠提供更高的性能或降低功耗,在某些情況下它是非此即彼的。你會得到兩者并不總是給定的。

“再說一次,沒有任何處理器是最適合所有事情的。您不能總是提高性能并降低功耗,”Uhm 繼續說道。“但專注于這種新架構,一種異構處理器,基本上可以讓他們做到這一點。”

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19384瀏覽量

230487 -

晶體管

+關注

關注

77文章

9721瀏覽量

138594 -

AI

+關注

關注

87文章

31271瀏覽量

269634

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

石墨烯互連技術:延續摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

“芯合”異構混合并行訓練系統1.0發布

后摩爾定律時代,提升集成芯片系統化能力的有效途徑有哪些?

異構集成封裝類型詳解

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

“自我實現的預言”摩爾定律,如何繼續引領創新

封裝技術會成為摩爾定律的未來嗎?

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

通過并行處理和異構SoC超越摩爾定律

通過并行處理和異構SoC超越摩爾定律

評論