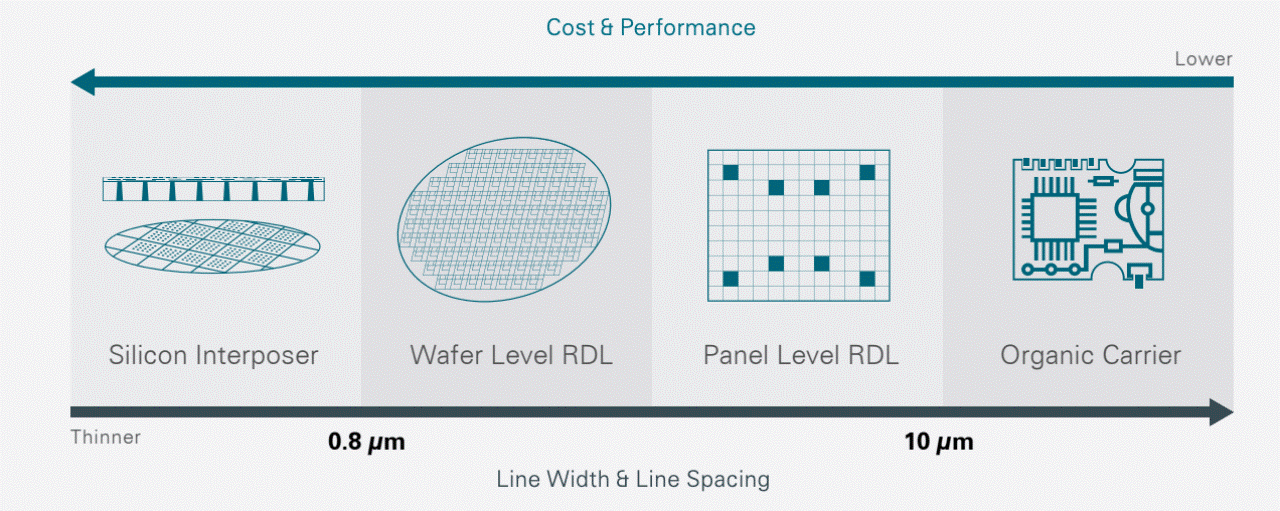

近幾年中,芯片特征尺寸已接近物理極限,而先進封裝技術成為延續摩爾定律的重要途徑。一系列新型封裝技術出現在人們視野之中。而其中扇出型晶圓級封裝(FOWLP)被寄予厚望,它將為下一代緊湊型、高性能的電子設備提供堅實而有力的支持。

扇出型晶圓級封裝技術無需使用中介層或硅通孔(TSV),即可實現外形尺寸更小芯片的封裝異構集成。在嵌入每個裸片時,裸片間的空隙會有一個額外的I/O連接點,在提高I/O數量的同時,也會使得硅的利用率有所提升。在扇出型晶圓級封裝技術的加持下,具有成千上萬I/O點的半導體器件可通過兩到五微米間隔線實現無縫連接,從而使互連密度最大化。

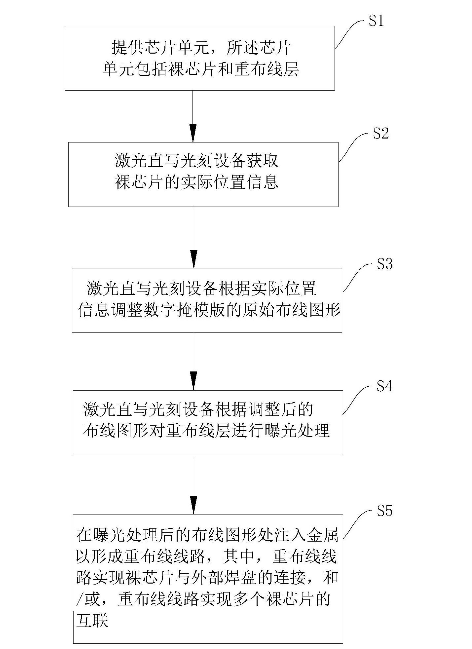

工藝步驟

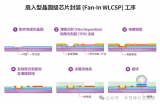

從晶圓代工廠(Foundry)生產完成的晶圓(Wafer)經過測試后進入生產線類似傳統封裝,扇出型封裝第一步也需要將來料晶圓切割成為裸晶。

扇出型封裝的主要特點是將切割后的裸晶組合成為重構晶圓,與來料晶圓相比,重構晶圓上裸晶之間的距離相對更大,因此方便構造單位面積更大,輸入輸出(I/O)更多的芯片成品。

塑封、去除載片

完成重構晶圓的貼片后,對重構晶圓進行塑封以固定和保護裸晶。然后將重構晶圓載片移除,從而將裸晶對外的輸入輸出接口(I/O)露出。

制作再布線層

為了將裸晶上的接口(I/O)引出至方便焊接的位置,在晶圓上通過金屬布線工藝制作再布線層(RDL)。

晶圓減薄

為使芯片成品更輕薄,對晶圓進行減薄加工。

植球

在再布線層(RDL)所連接的金屬焊盤上進行植球,方便后續芯片在印刷電路板(PCB)上的焊接。

晶圓切割、芯片成品

最后將重構晶圓進行切割,以得到獨立的芯片。

芯片制造工藝的發展不會停滯,長電科技在先進封測領域深耕多年,擁有深厚的技術積累和堅實的平臺。無論是現在還是未來,長電科技都將精準把握市場趨勢、緊扣科技脈搏,為推動芯片成品制造技術的突破與發展盡一份力量。

審核編輯:劉清

-

半導體

+關注

關注

334文章

27363瀏覽量

218713 -

晶圓

+關注

關注

52文章

4912瀏覽量

127988 -

FOWLP

+關注

關注

1文章

15瀏覽量

9977

原文標題:硬核科普 | 一文看懂扇出型晶圓級封裝(FOWLP)

文章出處:【微信號:gh_0837f8870e15,微信公眾號:長電科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

先進封裝技術- 6扇出型晶圓級封裝(FOWLP)

科普一下扇出型晶圓級封裝(FOWLP)

科普一下扇出型晶圓級封裝(FOWLP)

評論