引言:我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開發(fā)人員提供使用。通過本文,可以了解到:

Xilinx 7系列FPGA管腳是如何定義的

原理圖設(shè)計(jì)時(shí)如何下載FPGA管腳文件(Pinout文件)

1.Xilinx7系列FPGA管腳定義

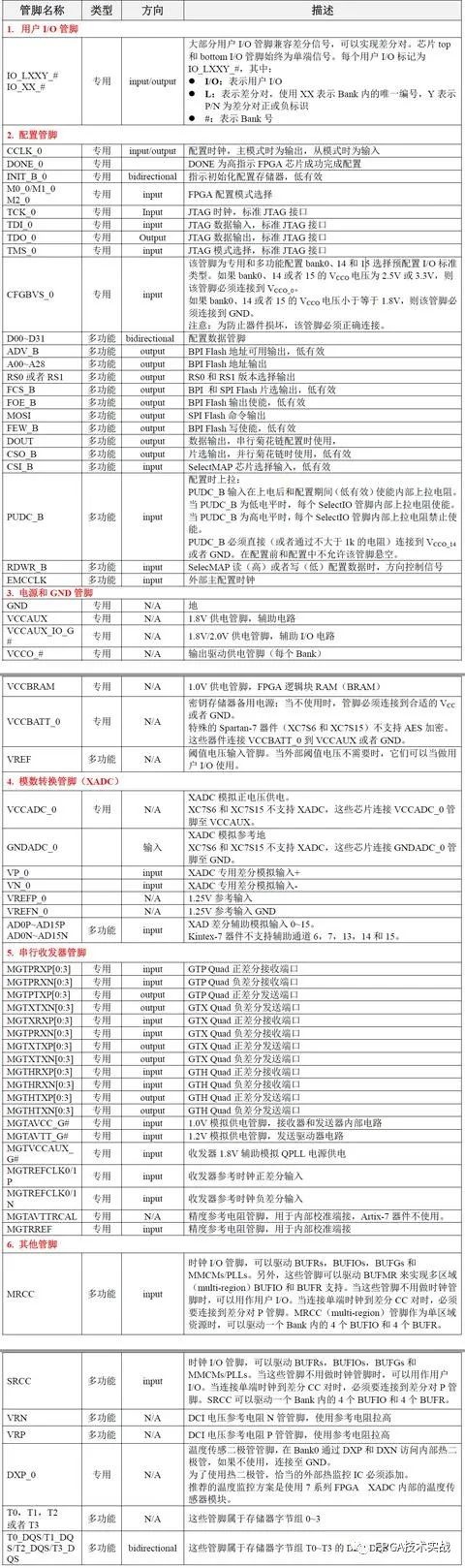

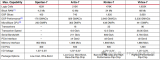

表1-1列出了7系列FPGA封裝中的管腳定義。注意:表1-12有單獨(dú)列出的專用通用用戶I/O,也有標(biāo)記IO_LXXY_ZZZ#或者I/O_XX_ZZZ_#標(biāo)識(shí)的多功能I/O,其中ZZZ代表一種或幾種附加的功能。如果多功能I/O不用做特殊用途,它們可以當(dāng)作普通I/O使用,這一點(diǎn)我們?cè)谟布O(shè)計(jì)時(shí)要注意。

表1-1、Xilinx 7系列FPGA管腳定義

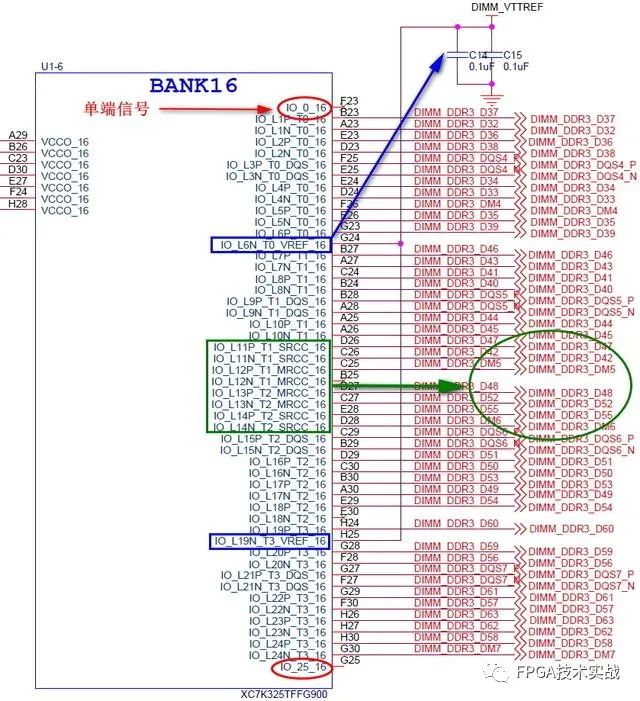

FPGA的器件管腳按照Bank進(jìn)行劃分,每個(gè)Bank獨(dú)立供電,以使FPGA I/O適應(yīng)不用電壓標(biāo)準(zhǔn),增強(qiáng)I/O設(shè)計(jì)的靈活性。每個(gè)用戶Bank包括50個(gè)I/O管腳或者24對(duì)差分對(duì)管腳(48個(gè)差分信號(hào)),Top和Bottom各一個(gè)單端管腳。圖1給出了K325T芯片用戶Bank IO原理圖舉例。

圖1、K325T芯片用戶Bank IO原理圖

在圖中,我們可以看到紅色圈住的兩個(gè)單端信號(hào),綠色線條圈住的_CC時(shí)鐘管腳不用作時(shí)鐘輸入時(shí)可以作為用戶I/O來使用,另外,還可以看到藍(lán)色標(biāo)記的VREF管腳,當(dāng)該BANK I/O用作DDR內(nèi)存接口時(shí),需要提供偽差分所需的閾值電壓,此時(shí)_VREF_管腳需要接DDR外設(shè)要求的參考電壓。其他I/O管腳分析,可以參考表1-1管腳定義說明。

2.Xilinx7系列FPGA管腳Pinout文件下載

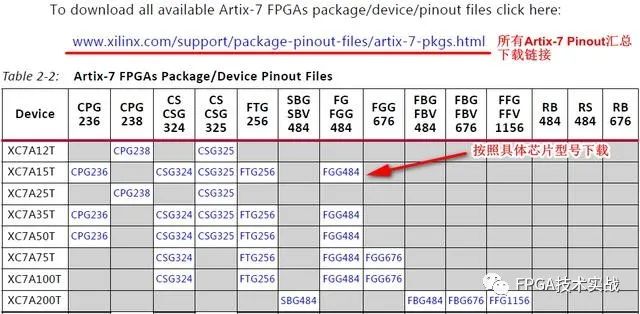

我們?cè)谶M(jìn)行原理圖庫設(shè)計(jì)時(shí),如何獲得FPGA每個(gè)管腳定義呢?在UG475官方文檔第二章7 Series FPGAs Package Files的ASCII Pinout Files子節(jié)中,按照FPGA器件家族和器件封裝分類,給出了7系列所有器件Pinout定義鏈接地址。官網(wǎng)給出CSV和TXT兩種格式Pinout文件,我們可以靈活選擇。

圖2、FPGA Pinout下載鏈接

圖3、Xilinx官網(wǎng)下載Pinout

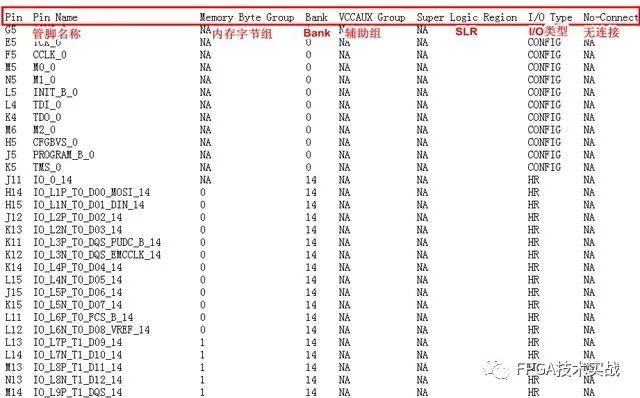

我們打開一個(gè).TXT形式的Pinout,如圖4所示。可以看到,文件分為8列,包含所有設(shè)計(jì)原理圖所需的關(guān)鍵信息:管腳編號(hào)、管腳名稱、管腳DDR內(nèi)存分組、管腳BANK編號(hào)、輔助組(VCCAUX)、超級(jí)邏輯域(SLR)、I/O管腳類型(配置、HR、HP、收發(fā)器管腳等)以及與器件Pin-to-Pin兼容相關(guān)的NC管腳信息。

圖4、Pinout文件內(nèi)容舉例

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1629文章

21746瀏覽量

603751 -

pcb

+關(guān)注

關(guān)注

4319文章

23108瀏覽量

398182 -

Xilinx

+關(guān)注

關(guān)注

71文章

2167瀏覽量

121539

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】測(cè)試一

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒有?

采用Xilinx FPGA的AFE79xx SPI啟動(dòng)指南

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+01.開箱(zmj)

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

Xilinx 7系列FPGA PCB設(shè)計(jì)指導(dǎo)

國產(chǎn)FPGA核心板!米爾紫光同創(chuàng)Logos-2和Xilinx Artix-7核心板

FPGA核心板 Xilinx Artix-7系列XC7A100T開發(fā)平臺(tái),米爾FPGA工業(yè)開發(fā)板

FPGA核心板上市!紫光同創(chuàng)Logos-2和Xilinx Artix-7系列

Xilinx FPGA的約束設(shè)置基礎(chǔ)

Xilinx 7系列FPGA功能特性介紹

Xilinx fpga芯片系列有哪些

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Xilinx 7系列FPGA管腳是如何定義的

Xilinx 7系列FPGA管腳是如何定義的

評(píng)論