全球大部分 IP 流量都經過數據中心,不斷增長的數據處理、存儲和傳輸量正在推動對數據中心服務的需求快速增長。提供這些服務需要能源,隨著服務器數量的增長以及這些服務器切換到新的高性能、耗電的處理器,能源需求有可能快速增長。因此,數據中心運營商正在尋找方法來提高處理能力,同時保持盡可能低的功耗。

為了滿足這一要求,系統架構師和設計人員在設計處理器電源方案時需要考慮整體系統效率。解決這一挑戰的一種方法是提高數據中心機架的功率密度,這可以通過對用于轉換和調節直流電壓的電源管理 IC (PMIC) 技術采用新方法來幫助實現。

提高效率的動力

幾乎每件電子設備中都有一個 DC/DC 轉換階段,實際上,這會損失一些能量。在便攜式設備中,這會降低電池壽命和產生過多的熱量,而在交流輸入設備中,這也意味著增加公用事業能源供應的額外美元成本,從而對環境產生更大的影響。產生的額外熱量需要額外的冷卻裝置,如果不能有效消散,可能會降低產品的可靠性。

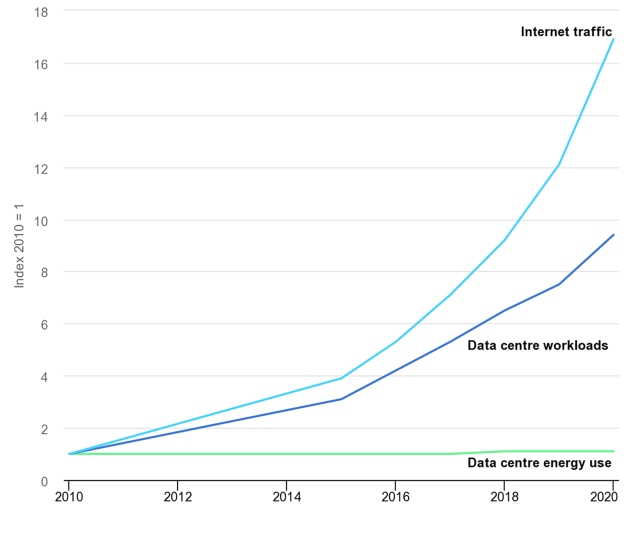

因此,有各種動機來提高 DC/DC 轉換效率,尤其是在數據中心,據 IEA 報告稱,數據中心消耗了全球約 1% 的能源供應,或 2020 年消耗了 200-250 TWh,可能還會使用另外 100 TWh用于加密貨幣挖掘。與此同時,數據傳輸網絡在同一時期消耗了 260-340 TWh。1盡管互聯網流量以每年約 30% 的速度增長,但由于電力轉換效率的提高,這些能源消耗數據在過去 10 年中保持相對平穩(圖 1)。

圖 1:2010-2020 年互聯網流量、數據中心工作負載和數據中心能源使用的全球趨勢

然而,情況正在發生變化:最好的超大規模數據中心現在的整體電力使用效率約為 1.1,這意味著 IT 設備每消耗 10 千瓦時,系統供應和冷卻僅損失 1 千瓦時。雖然未來功率轉換效率會逐步提高,特別是隨著寬帶隙半導體使用的增加,但隨著數據中心升級到最佳實踐,進一步的全球收益受到限制。因此,在未來幾年,能源需求將開始更直接地隨著數據吞吐量而擴大。這給已經面臨嚴重空間限制并需要將更多處理能力(因此,更高的散熱量)打包到每個機架中的系統設計人員提出了一個問題。如果功率轉換元件也需要增加空間,

DC/DC 功率密度越來越受到關注

因此,在給定體積內測量功率轉換器的輸出正成為一個重要的設計問題。如果可以提高功率密度,那么可以在不成比例地增加轉換器尺寸的情況下增加機架功能。由于電源管理是提高功率密度的關鍵,因此提高執行工作的 PMIC 的性能已成為一個越來越重要的目標。當涉及到高效率和高功率密度時,提供端負載電壓的 DC/DC 轉換器是一個焦點。此處的任何損耗都會在電源系統中向上游傳播,因為在總線轉換器和 AC/DC 以及功率因數校正階段會進一步損耗能量。同時,這些負載點 (PoL) 轉換器還需要盡可能靠近其負載以避免電壓下降。由于現代處理器在大電流下需要低于 1V 的電源軌,公差已經很緊了。如果事情還不夠困難,負載 IC 需要在其周圍的 PCB 中為數據和地址總線提供空間,并且需要高性能冷卻,從而為電源轉換器留下很小的空間。

因此,PoL 轉換器需要最大化功率并最小化尺寸。當開關穩壓器從固有損耗的線性類型中接管時,可以看到一條清晰的路徑,以接近零損耗;半導體開關在關閉時不會消耗任何能量,而在開啟時幾乎不會消耗,隨著技術的進步和設備并聯,即使這種損耗也會減少。雖然半導體效率有所提高,但實際上無源元件已成為尺寸的限制,因此也限制了功率密度。大多數開關穩壓器都需要一個電感器和輸入/輸出電容器,這些電容器的尺寸往往會隨著所需功率而增大,而隨著開關頻率而減小。出于這個原因,更高的頻率可以更好地減少占位面積,但隨后半導體動態損耗開始增加,從而損害效率。此外,在較高的開關速率下,電感器磁芯損耗和電容器寄生損耗會顯著增加。因此,PoL 轉換器必須以折衷的頻率運行,通常最多不超過幾兆赫茲。

誘人的是,在非常高的頻率下,必要的電感可以非常低,以至于不需要有損耗的磁芯,并且在減小的環路直徑中只需要幾匝——這可以在 PCB 跟蹤的小區域內實現。最新的電容器技術還導致高頻所需的低值進一步小型化。剩下的問題是半導體開關損耗將效率降低到一個不可行的值。現在,Empower Semiconductor 開發的一種新的集成穩壓器 (IVR) 技術改變了這種情況。3

功率密度突破

新的 IVR 技術通過使用獲得專利的、可數字配置的多相諧振開關方法解決了開關損耗挑戰,該方法可最大限度地減少導致開關轉換時耗散的電壓和電流重疊。基于具有嵌入式硅電容器的先進 CMOS 幾何結構,這允許在低數百兆赫范圍內運行,并且在整個負載范圍內具有幾乎平坦的高效率。器件的效率峰值為 91%,其輸入電壓為 1.8V,可編程輸出電壓范圍為 0.5V 至 1.2V,額定電流為 10A 連續電流,15A 峰值電流。所有這些都是在具有 5 × 5-mm PCB 占位面積和僅 0.75 mm 輪廓的倒裝芯片芯片級封裝 (FcCSP) 中實現的。全額定性能不需要分立的外部元件,與形成在主板銅跟蹤中的無芯電感器,通常在 IVR 封裝下方。采用 8 × 10-mm LGA 封裝的部件具有集成電感器。與競爭部件相比,所實現的 FcCSP 芯片占位面積減少了 10 倍,這意味著它可以安裝在更靠近負載的位置,甚至可以直接安裝在 SoC 基板上。

其他優勢

一個設計經驗法則是,開關電源控制環路的帶寬不應大于開關頻率的大約五分之一到十分之一,以避免不穩定。這導致在亞和低兆赫范圍內看到的典型開關頻率的環路響應時間為數百微秒。輸出電流壓擺率也受到低頻所需的大輸出電感的限制。Empower 設計以非常低的電感值在如此高的頻率下切換,使得環路響應約為 500 ns。此時電流可以從 0 A 轉換到 10 A,電壓偏移小于 15 mV,而之前的 PoL 模塊技術約為 50 mV。無需額外的外部電容器即可實現這一性能。

由于該設計允許負載階躍的最小電壓瞬變,并且非常小,以至于它可以安裝在非常靠近最終負載的地方,并且電壓降很小,因此可以將輸出標稱電壓設置為比以前更低,因為所需的電壓開銷更少。這可能會節省負載的能量。

超快速動態電壓縮放

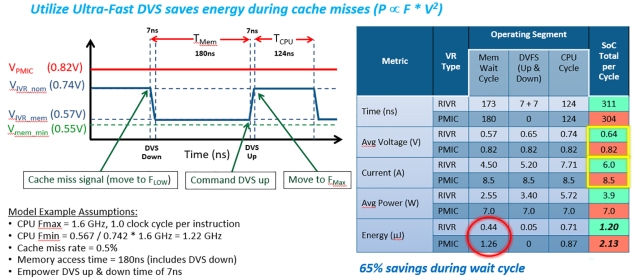

快速控制環路還允許非常快速的動態電壓縮放 (DVS),其中負載(通常是處理器)可以通過數字接口請求動態改變軌道電壓,以最大限度地降低整體功耗。

例如,在等待緩存數據時,可以放下鐵軌以減少耗散。圖 3 顯示了 Empower 部件在標稱電壓 (V IVR nom ) 和節能電壓 (V IVR mem ) 之間的轉換時間為 7 ns,從而在時鐘繼續進行的同時將每個等待周期的能耗降低了 65%。具有 DVS 功能的前幾代 PoL 轉換器比 Empower 部件慢約 1,000 倍,并且反應不夠快,無法利用這一點。V PMIC是老一代 PoL 轉換器所需的電壓,設置得更高以允許可能的電壓偏移與負載瞬變,并且在 180 ns 等待周期內無法通過 DVS 做出反應。

圖 3:Empower 的 IVR 可以在 7 ns 內從 V IVR nom轉換到 V IVR mem。

實際實施顯示顯著減少了占用空間

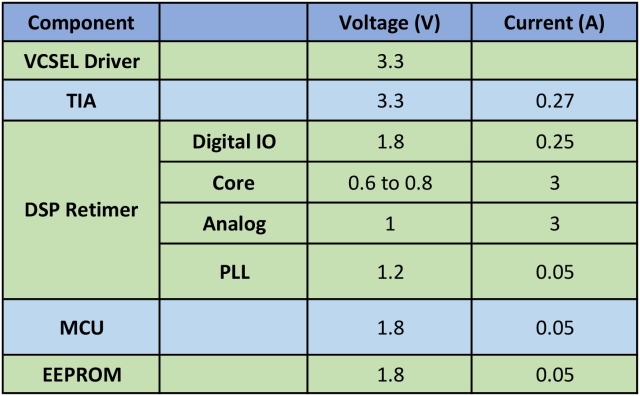

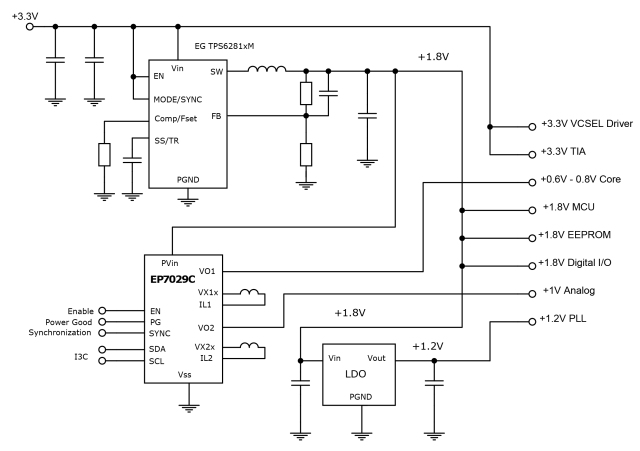

Empower IVR 部件在 1.8V 標稱輸入下運行,因此需要在系統級別與競爭 PoL 進行比較才有意義。例如,考慮圖 4 中描述的 DSP 芯片電源樹。

圖 4:典型的 DSP 電源樹

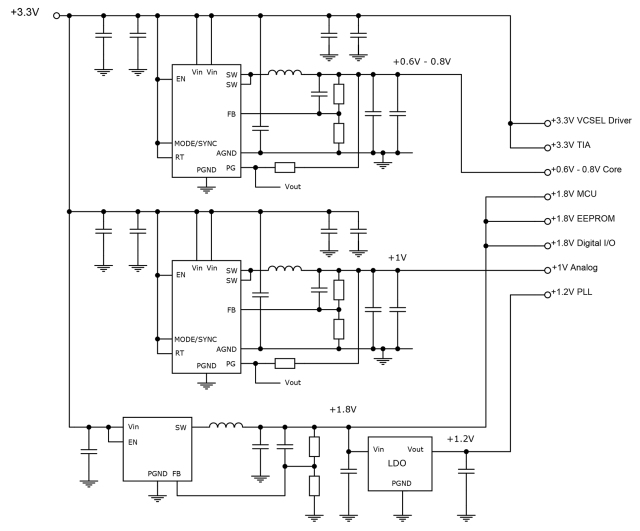

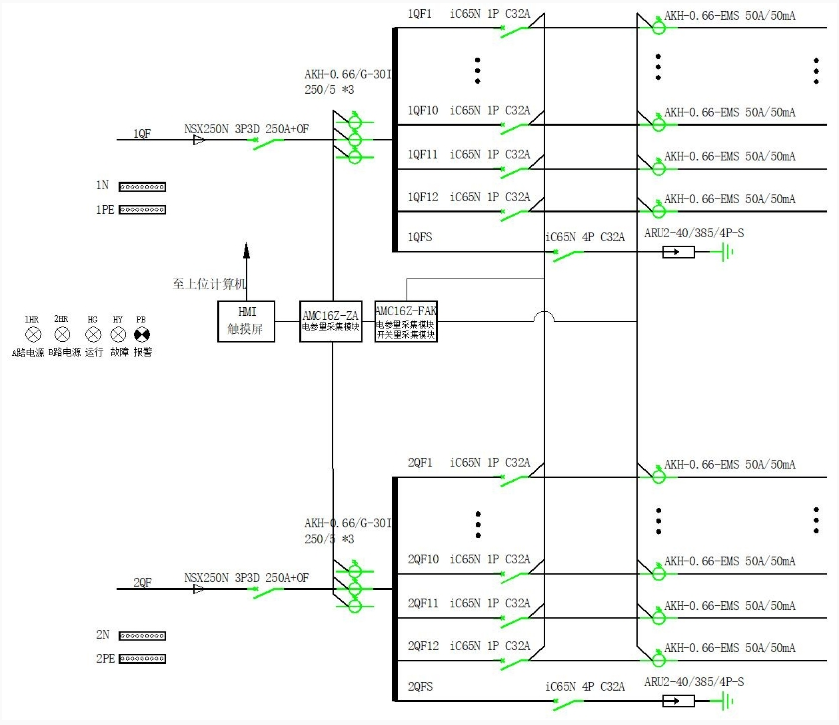

圖 5 顯示了滿足此要求的典型電源實現方案。它使用 36 個分立元件并占用約 360 mm 2的電路板空間。但是,當使用 Empower 部件實現時,圖 6 中的原理圖結果是,在 155-mm 2的電路板區域中只有 14 個分立元件。

圖 5:圖 4 的電源樹,使用現有 PoL 技術實現

圖 6:圖 4 的電源樹,使用 Empower 的 EP7029C IVR 實現

盡管尺寸很小,但 Empower IVR 包括全面的功能——提供使能輸入和電源良好輸出以及提供功能遙測的 I 3 C 數字接口,以及根據需要動態編程輸出電壓的能力。演示板帶有用于設置和監控的 GUI。這些部件還具有針對外部故障和過熱的全面保護。Empower IVR 提供單路、雙路和三路獨立穩壓輸出,并采用 FcCSP 和 LGA 封裝樣式。

概括

我們已經看到 DC/DC 轉換器如何需要在緊湊的電子設備中具有更高的功率密度,例如現代數據中心使用的機架。過去,通過提高開關頻率和減小分立元件的尺寸來實現這一點通常意味著半導體效率必須受到影響。因此,操作通常僅限于使用常用部件的幾兆赫茲。

然而,現在,集成穩壓器的可用性正在幫助解決這個問題,方法是在非常高的開關頻率下保持高效率,并逐步提高功率密度。這些 IVR 將高度集成與快速瞬態響應和行業領先的 DVS 性能相結合,可滿足現代高端處理要求的需求,同時提高整體系統效率。

審核編輯:郭婷

-

半導體

+關注

關注

334文章

27380瀏覽量

218944 -

穩壓器

+關注

關注

24文章

4241瀏覽量

93828 -

數據中心

+關注

關注

16文章

4782瀏覽量

72141

發布評論請先 登錄

相關推薦

哪些是數據中心的重要系統?

數據中心液冷需求、技術及實際應用

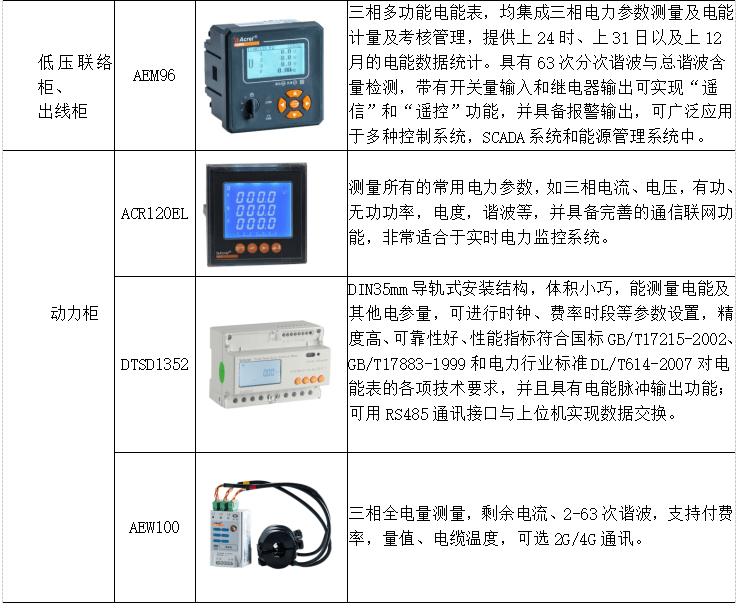

【解決方案】機房能源末端 數據中心 精密配電管理系統

淺談數據中心節能措施探析與研究

數據中心變“綠“要點有哪些?

解鎖數據中心的系統級節能

解鎖數據中心的系統級節能

評論