在SpinalHDL里,其lib庫(kù)處處可見(jiàn)Stream的身影,而在常用的邏輯設(shè)計(jì)里,尤其接口的處理中,握手信號(hào)的處理也是老生常談的話題。而在接受設(shè)計(jì)里,SpinalHDL中的“一別兩寬”式設(shè)計(jì)方式,著實(shí)讓我贊同。

》》Stream

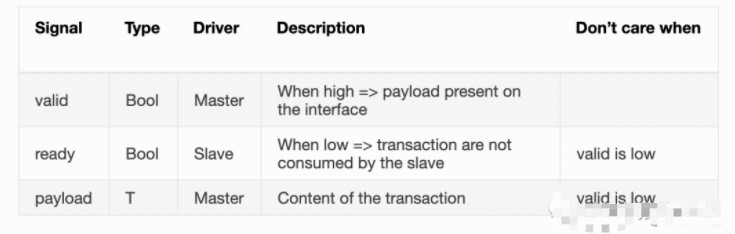

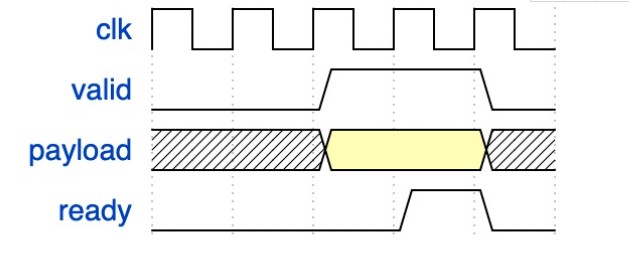

Stream本質(zhì)上是一個(gè)帶數(shù)據(jù)的握手協(xié)議:

在數(shù)字邏輯電路里,無(wú)論是普通的模塊接口之間,還是標(biāo)準(zhǔn)的AMBA、Avalon等總線,都處處可見(jiàn)Stream的身影:

》》握手之殤,糾纏不清

無(wú)論是新手還是老手,對(duì)于Stream這種握手形式的邏輯處理還是挺煩的。Stream這種握手形式的邏輯僅僅是添加一級(jí)寄存器還是頗顯得繁瑣的,需要小心翼翼的處理。更遑論當(dāng)設(shè)計(jì)里還牽涉到數(shù)據(jù)的處理。這種在處理功能邏輯的同時(shí)又要考慮握手信號(hào)的處理時(shí)在設(shè)計(jì)邏輯電路時(shí)還是顯得頗頭大的,畢竟“一心二用”還是頗有不便……

仔細(xì)想想,在接口信號(hào)處理時(shí),功能性的設(shè)計(jì)往往是組合邏輯頗多,而為了更好的滿足時(shí)序約束,往往需要添加寄存器來(lái)優(yōu)化時(shí)序,單獨(dú)處理或許并不顯得復(fù)雜,但當(dāng)把兩者混在一塊兒便極易“按起葫蘆浮起瓢”,導(dǎo)致設(shè)計(jì)功能性錯(cuò)誤了。倘若糾纏不清令人頭大,那一別兩寬呢?把功能邏輯和為了優(yōu)化時(shí)序的pipeline分開(kāi)豈不是設(shè)計(jì)極其簡(jiǎn)單。

》》Stream pipeline

Stream的pipeline處理在SpinalHDL里提供了很好的封裝:

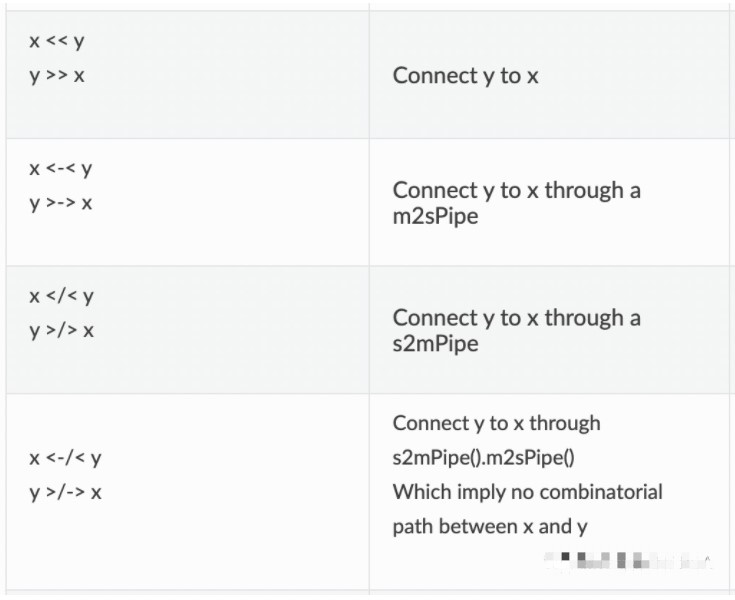

Stream接口的pipeline里有三種類(lèi)型:

m2sPipe: 為兩個(gè)Stream接口之間的valid,payload之間添加一級(jí)寄存器。

s2mPipe:為兩個(gè)Stream接口之間的ready路徑添加一級(jí)寄存器。

s2mPipe().m2sPipe():在兩個(gè)Stream接口之間的valid,payload、ready之間均添加一級(jí)寄存器。

上面的三種接口pipeline方式能夠很好的滿足接口中的時(shí)序優(yōu)化。SpinalHDL里也提供了相應(yīng)簡(jiǎn)單的連接符(箭頭指向誰(shuí)誰(shuí)就是目的端)。關(guān)于這里面的源代碼分析可參見(jiàn)文章《打個(gè)拍,握個(gè)手可以么》。

》》功能處理

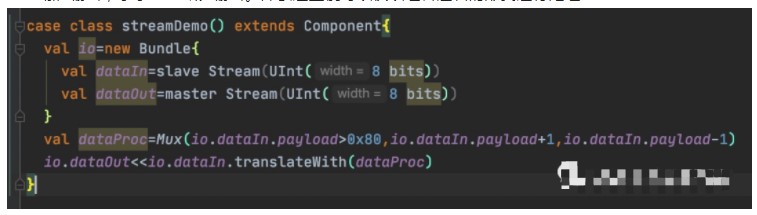

有了前面Stream接口的pipeline方式,在Stream接口信號(hào)中的處理功能性邏輯時(shí),我們便可以采用組合邏輯的方式進(jìn)行處理。舉個(gè)簡(jiǎn)單的例子,在邏輯設(shè)計(jì)里對(duì)輸入的Stream信號(hào)中的payload如果大于0x80加1輸出,小于0x80減1輸出。那么這里便可以?xún)H以組合邏輯的形式進(jìn)行處理:

在上面的邏輯處理里,整個(gè)設(shè)計(jì)均采用組合邏輯的形式進(jìn)行處理。

》》合二為一

有了上面的那些,那么合二為一便很容易了。功能處理采用組合邏輯,時(shí)序處理采用pipeline。“一別兩寬”之后,合二為一便好了:

》》寫(xiě)在最后

就個(gè)人使用來(lái)講,在SpinalHDL的設(shè)計(jì)里,這種方式極大的簡(jiǎn)化了電路設(shè)計(jì)的復(fù)雜度。理解了Stream的使用,那么對(duì)于SpinalHDL中l(wèi)ib的大多數(shù)功能也能夠有一個(gè)很好的了解與使用。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5397瀏覽量

122630 -

AMBA

+關(guān)注

關(guān)注

0文章

70瀏覽量

15256 -

數(shù)字邏輯電路

+關(guān)注

關(guān)注

0文章

106瀏覽量

15991

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

幾種常見(jiàn)的開(kāi)關(guān)電源工作原理

用TAS5630分別做兩路橋接、四路單端和四路橋接,只要有兩種模式一起工作,輸出端有很尖銳的高頻噪聲,為什么?

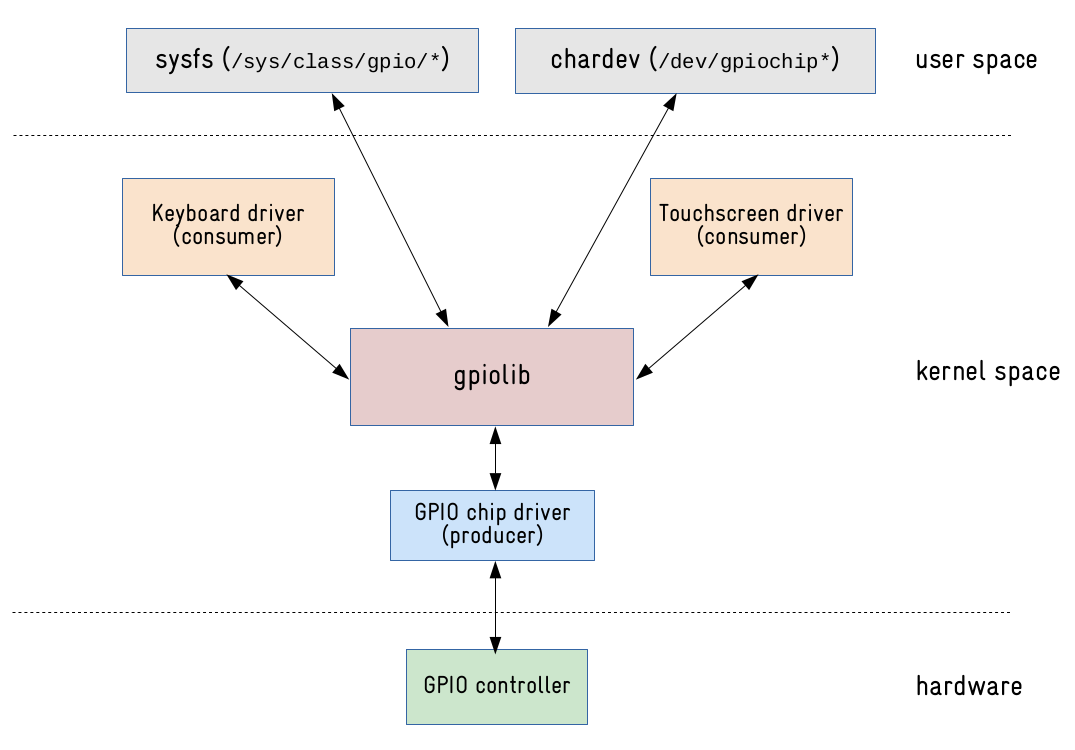

Linux應(yīng)用層控制外設(shè)的兩種不同的方式

評(píng)論