對于本文,我們將繼續討論全局時鐘恢復、分布式時鐘同步和事件同步的主題。

全局時鐘恢復

假設在一個復雜系統中有多個代理。每一個都有自己的參考時鐘,給它一種時間感。代理的時間概念由自啟動以來經過的參考時鐘滴答數給出。

為了同步動作和共享時鐘,代理需要有一個共同的、全局的時間感。使用 USB 或 Firewire 之類的總線系統很容易做到這一點,因為總線往往帶有自己的時鐘。然而,對于分布式、基于數據包的互連,事情變得更加困難。IEEE 標準 1588、1588v2 和 802.1as 以及 IETF NTP 標準旨在專門解決分布式全局時鐘恢復問題。

系統的第一個任務是選擇一個代理作為主代理。正是這個代理的時鐘將成為通用的全局時鐘。IEEE 1588 及其變體使用點對點領導選舉協議,試圖在代理中選擇最高質量的時鐘。保證會選出一位,而且只有一位,master。

Once the master is elected, each agent needs to know the following information:

我的時鐘是否比全球主時鐘慢/快?如果是這樣,多少?

根據主時鐘,現在是幾點鐘?

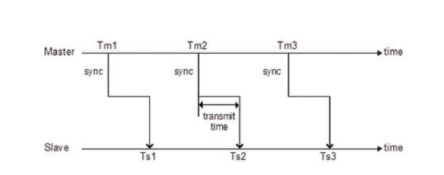

使用的基本方法是定期將同步消息從主代理傳輸到其他代理。消息包含發送消息的全球時間。下圖顯示了這種情況:

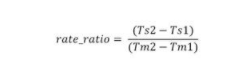

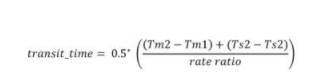

從站知道主站執行的傳出時間戳(Tm1、Tm2 和 Tm3),以及從站執行的入站時間戳(Ts1、Ts2 和 Ts3)。給定這些時間戳,它可以計算出主時鐘與其自己的本地時鐘之間的比率。例如,以下計算會測量兩個時鐘之間的比率:

可以過濾該值的多個測量值以平均傳輸時間的變化。隨著時間的推移跟蹤該值還將跟蹤所涉及的兩個時鐘中的任何漂移。

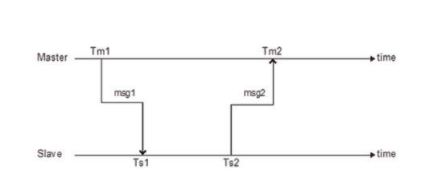

為了在全球時間和本地時間之間進行完全轉換,slave 還需要知道它與 master 的時間偏移量,這意味著它需要知道同步消息的傳輸時間。為此,主機和從機執行兩種方式的消息交換:

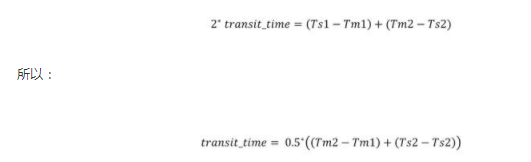

假設傳輸時間是對稱的:

這里需要小心,因為時間戳 Tm2 和 Tm1 參考與 Ts2 和 Ts1 不同的時鐘。所以從機需要進行計算:

知道這個傳輸時間允許從機計算出它與主時鐘的偏移量。它現在擁有在全球和本地時間之間轉換所需的所有信息,反之亦然。

實際上,像 802.1as 這樣的時間同步協議比這里描述的要復雜一些,但基本思想是一樣的。

事件同步

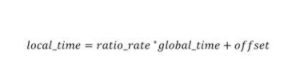

一旦全局時鐘同步到位。本地代理可以將全球時間轉換為本地時間:

這意味著兩個代理可以同步他們的動作。每個人都有一個全局時間來執行一個事件。代理將此全球時間轉換為本地時間,然后安排事件在該時間發生。當然,這些事件不會同時發生。會有一些同步錯誤。此錯誤包括:

由于全局時鐘恢復導致的錯誤

由于代理在特定本地時間觸發事件的能力的可變性而導致的錯誤。

自上次同步以來代理的本地時鐘變化導致的錯誤

這些錯誤的大小將取決于通信技術、同步協議、代理之間的消息時間戳的準確性以及代理內的本地事件同步。

在以太網通信的情況下,使用 IEEE 802.1as 作為時間同步協議,XMOS XCore 設備作為代理,同步誤差可以小于 150 ns。

基于全局時鐘恢復其他時鐘

有時需要使用全局時間作為參考來恢復輔助時鐘。IEEE AVB 1722 標準就是這種情況,需要恢復媒體時鐘以將音頻或視頻從一個端點傳輸到另一個端點。

在這種情況下,使用我之前關于軟件時鐘的文章中描述的控制環路來恢復時鐘。這種情況下的區別在于如何檢測錯誤。

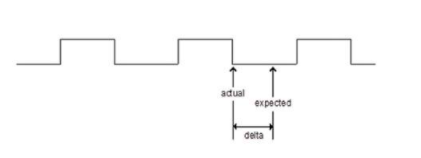

發送時鐘的代理也可以發送某些時鐘邊沿應該出現的預期時間。當從機恢復并輸出時鐘時,它可以跟蹤該邊沿實際發生的時間,并獲得預期時間和實際時間之間的差值。全局時鐘的存在允許代理有一個共同的時基來計算增量。

該增量給出了饋入 PID 控制回路的誤差項。然而,還有一個“陷阱”需要注意。目的是恢復時鐘周期;這使得預期邊緣時間和實際邊緣時間之間的增量成為積分誤差而不是比例誤差。這意味著比例誤差是增量的變化率。一旦理解了這一點,就可以以標準方式調整控制回路。

-

以太網

+關注

關注

40文章

5452瀏覽量

172195 -

usb

+關注

關注

60文章

7966瀏覽量

265299 -

時鐘

+關注

關注

11文章

1742瀏覽量

131640

發布評論請先 登錄

相關推薦

賽靈思FPGA全局時鐘網絡結構詳解

全局時鐘資源和網絡的路徑和組件組成

FPGA設計:GPIO怎么走全局時鐘網絡

FPGA的全局時鐘是什么?

FPGA全局時鐘資源相關原語及使用

FPGA全局時鐘和第二全局時鐘資源的使用方法

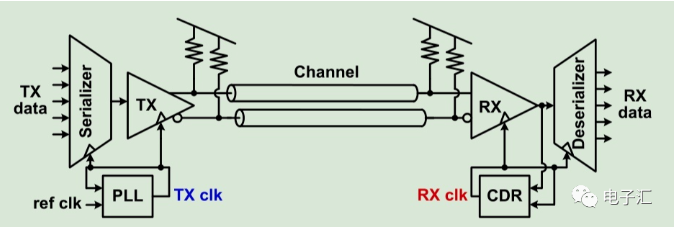

時鐘是怎么恢復的?

Xilinx全局時鐘的使用和DCM模塊的使用

全局時鐘資源相關xilinx器件原語的詳細解釋

一文看懂時鐘是怎么恢復的?

一文看懂時鐘是怎么恢復的?

探討全局時鐘恢復其他時鐘的問題

探討全局時鐘恢復其他時鐘的問題

評論