在通過Verilog語言完成芯片設計,且通過測試平臺設計(編寫testbench)對所設計的芯片施加激勵和觀測輸出后,需要在計算機上模擬芯片設計,以判斷所編寫的代碼是否符合預期。

在計算機上模擬芯片設計需運用仿真工具,常用的EDA仿真工具主要由三家集成電路公司提供,分別是Mentor Graphics、Cadence、SYNOPSYS。

MentorGraphics的產品是Modelsim,該產品主要在WINDOWS系統上運行,也可以在LINUX系統上運行,適合初學者使用。

Cadence的產品是NC-Sim,該產品主要在LINUX系統上運行,也可以在WINDOWS系統上運行。

SYNOPSYS的產品是VCS,該產品主要在LINUX系統上運行,不能在WINDOWS系統上運行。

上文提及的LINUX系統和WINDOWS系統是EDA仿真工具的兩種主要操作系統。

WINDOWS系統主要運用于可編程邏輯器件,如CPLD、FPGA的仿真,這是因為進行驗證的工程師(芯片生產前需要進行驗證,目的是防止實際生產的芯片出現漏洞導致百萬元到千萬元人民幣的損失)主要使用WINDOWS系統。可編程邏輯器件的仿真工具主要是Modelsim。

LINUX系統主要運用于ASIC設計,即專用集成電路設計的仿真,因為芯片設計到生產過程中使用的仿真以外的其他工具均支持LINUX系統,所以ASIC設計的仿真也主要使用LINUX系統。

根據課程推薦,ASIC設計人員或有學習更專業仿真工具想法的人員最優選擇是NC-Sim和VCS這兩種專業軟件。課程由于證書(license)限制,只能使用Modelsim的教學版進行芯片仿真講解。

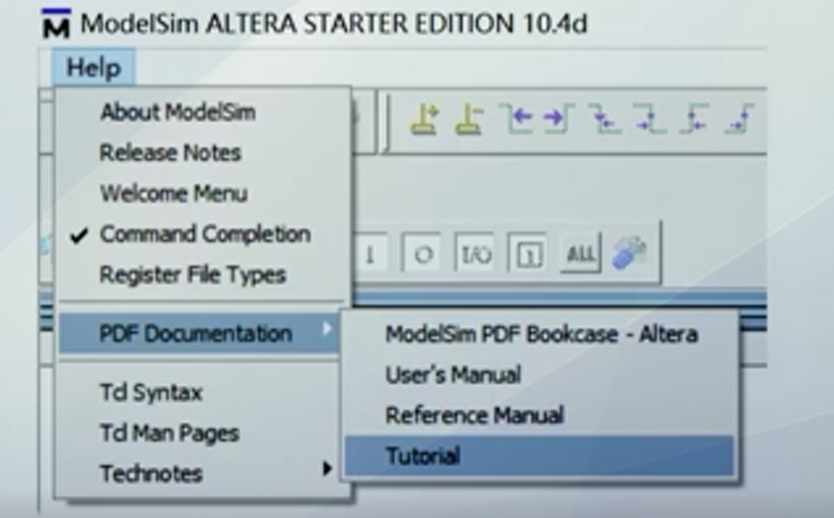

Modelsim中內嵌有教程和用戶手冊,如果需要學習Modelsim更高級的功能可以查找用戶學習手冊,網絡上也有高級教程可供學習和參考。

圖片來源:學堂在線《IC設計與方法》

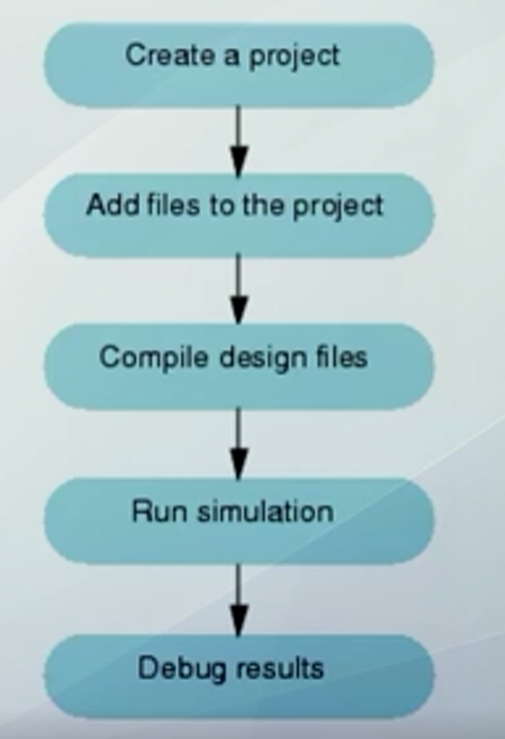

仿真的步驟如下:

(1)設置環境。包括在軟件里設置相應的工程環境,設置相應的庫文件,庫文件是其他人員已完成的設計文件,當設計芯片需要某些已設計完成的文件時,可以調用庫文件。

(2)編寫Verilog代碼。編寫Verilog代碼既可以使用文本編輯工具,也可以使用Modelsim中提供的代碼編輯工具。

(3)編譯。編譯的目標是將Verilog代碼轉化成計算機上可以執行的程序。

(4)仿真。在仿真工具中模擬電路執行過程。

(5)分析仿真結果。分析仿真結果是比較重要的步驟。分析仿真結果的目的是檢查電路模擬的結果是否正確,是否符合預期的設計目標。分析仿真結果的方法有多種:最直接的方法是用波形的方式檢查,更高層次的方法包括數據流圖(以圖形方式來表達系統的邏輯功能、數據在系統內部的邏輯流向和邏輯變換過程)、有限機(全稱有限狀態機,是一種用于進行對象行為建模的工具,作用是描述對象在其生命周期內所經歷的狀態序列,以及如何響應來自外界的各種事件),或用比較高效的方法定位故障發生的位置。

圖片來源:學堂在線《IC設計與方法》

審核編輯 :李倩

-

芯片設計

+關注

關注

15文章

1023瀏覽量

54937 -

仿真

+關注

關注

50文章

4102瀏覽量

133738 -

Verilog

+關注

關注

28文章

1351瀏覽量

110163

原文標題:芯片設計相關介紹(21)——仿真工具

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

模擬IC設計中Spectre和HSPICE仿真工具的起源、差別和優劣勢

車載總線監控分析及仿真工具 - VBA

NVIDIA發布全新AI和仿真工具以及工作流

芯片開發必備工具|好用的文件比對工具有哪些?

C2000 MCU的ADC輸入電路評估(使用TINA-TI仿真工具)

C2000 ADC的電荷共享驅動電路(使用TINA-TI仿真工具)

免費好用的在線仿真工具Wokwi

演進中的電力電子設計:安森美先進仿真工具

安森美推出一款基于PLECS的具有獨特功能的領先在線仿真工具

康謀產品 | 為ADAS/AD開創的次世代AutoGI仿真工具

熱仿真工具Ansys Discovery的使用案例

芯片設計之仿真工具

芯片設計之仿真工具

評論