靜態時序分析在電路設計中的作用重要。

如果電路出現建立時間(根據網絡資料理解:為將信號穩定建立,數據輸入端信號保持穩定的最短時間)錯誤,電路工作速度變慢。

如果電路出現保持時間(根據網絡資料理解:為使傳遞信號正確,輸入信號保持穩定的最短時間,若保持時間錯誤,正確的輸入信號會被其他輸入信號覆蓋或不能按時傳輸到對應位置,導致輸入信號錯誤)錯誤,電路可能不能正常工作。

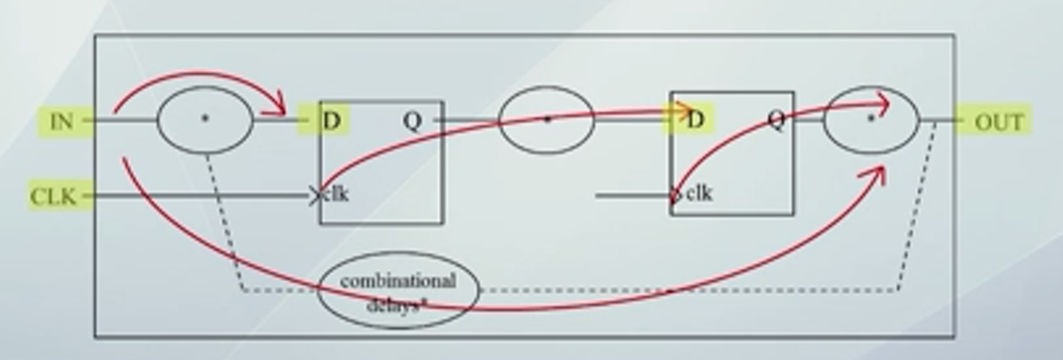

一個芯片電路通常包含四種類型的時序路徑:

(1)從芯片內部的源D觸發器(發送數據的觸發器)開始,經過一系列數據云圖(一系列組合邏輯電路),送達到芯片內部的目標D觸發器的數據端。

(2)輸入路徑,從芯片的輸入端,經過一系列數據云圖,送達到芯片內部的D觸發器。

(3)輸出路徑,芯片內部的D觸發器,經過一系列數據云圖,送達到芯片的輸出端。

(4)信號從芯片輸入端經過一系列組合邏輯電路達到芯片輸出端,時鐘信號對其不產生影響。

所有的時序分析均基于以上四種時序路徑分析。歸納以上四種路徑,所有的輸入信號均來源于芯片輸入端和時鐘輸入,所有的輸出信號都輸出到芯片輸出端或下一個時序器件的輸入端。

圖片來源:學堂在線《IC設計與方法》

Quarus Ⅱ工具(PLD設計工具,PLD是可編程器件,一種芯片的設計方式)有兩種方式進行靜態時序分析。

一種是自動化的方式,點擊編譯按鈕,Quarus Ⅱ工具會自動完成包括靜態時序分析、布局布線等工作。

另一種是手動的方式,在大型設計中,設計人員一般會采用手動方式進行靜態時序分析。手動分析方式既可以通過菜單操作(個人理解:通過鼠標點擊和鍵盤輸入)進行分析,也可以采用Tcl腳本(工具控制語言,個人理解運用代碼控制)進行約束和分析。

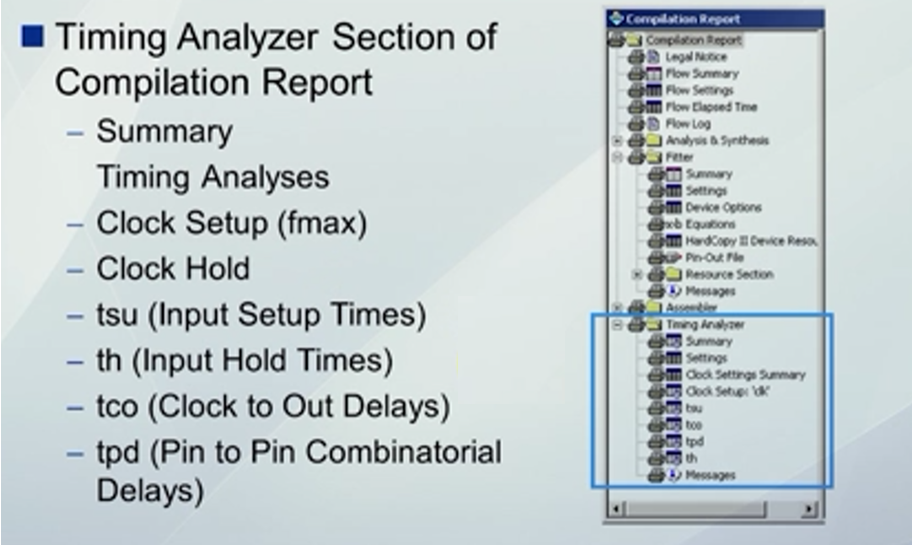

下圖藍框內為時序分析結果,需要關注的分析結果包括:時序分析約束的設置、芯片報告的總結、內部時鐘率分析(芯片建立時間和保持時間的報告)、輸入路徑的建立時間和保持時間的報告、輸出的TCO(時鐘輸出延遲)報告、組合邏輯路徑延時報告。

圖片來源:學堂在線《IC設計與方法》

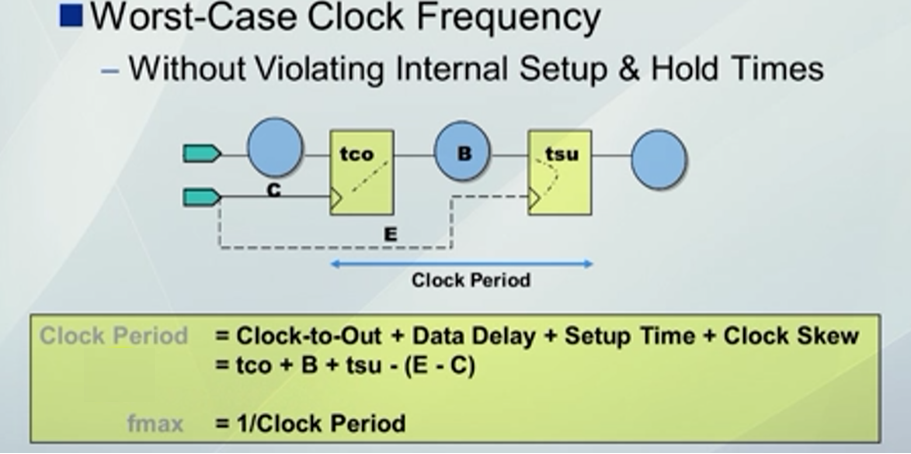

下圖是時鐘周期(Clock Period)的描述。

信號從源觸發器(圖中標有tco的黃色小矩形)輸出到目標觸發器(圖中標有tsu的黃色小矩形)需經過內部組合電路B(圖中標有B的圓形),經過內部組合電路B會產生延時。

時鐘信號傳遞到源觸發器會產生延時C,傳遞到目標觸發器會產生延時E。因為傳遞到源觸發器和目標觸發器的路徑不同,所以C和E不一定相同。

時鐘信號到達觸發器時,數據會經過tco(Clock to Out)的延時,再經過路徑B(Data Delay)的延時,同時目標觸發器需要tsu(Setup Time)的延時達到穩定。

除上述三個延時外,還需考慮時鐘信號傳遞到觸發器的延時。若E的延時大于C的延時,數據傳輸時間余量增多,其他條件不變,時鐘周期(Clock Period)可以縮短。若C的延時大于E的延時,數據傳輸時間余量減少,其他條件不變,時鐘周期(Clock Period)需要增加。

綜上,時鐘周期的描述公式如下圖黃色矩形內的公式所示。芯片工作的最高頻率為時鐘周期的倒數。

圖片來源:學堂在線《IC設計與方法》

-

電路設計

+關注

關注

6675文章

2453瀏覽量

204373 -

觸發器

+關注

關注

14文章

2000瀏覽量

61158 -

時序

+關注

關注

5文章

387瀏覽量

37333

原文標題:芯片設計相關介紹(31)——PLD靜態時序分析

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

英諾達發布全新靜態驗證產品,提升芯片設計效率

高通量生物分析技術之微流控芯片

鎖存器的基本輸出時序

時序邏輯電路故障分析

FPGA 高級設計:時序分析和收斂

Xilinx FPGA編程技巧之常用時序約束詳解

芯片設計之PLD靜態時序分析

芯片設計之PLD靜態時序分析

評論