最近新做了一塊板子,用到Spartan 7芯片對(duì)前級(jí)視頻源疊加OSD菜單,前級(jí)會(huì)將HMDI轉(zhuǎn)成LVDS送給FPGA處理,在原理圖設(shè)計(jì)階段沒有仔細(xì)閱讀fpga手冊(cè),導(dǎo)致LVDS BANK供電錯(cuò)誤,應(yīng)該接2.5V,實(shí)際接3.3V,且BANK供電沒有用磁珠隔開,整板3.3V鋪在一個(gè)平面,導(dǎo)致fpga lvds無法工作。搜集了相關(guān)資料,這里做下小結(jié),避免后續(xù)再犯類似錯(cuò)誤。

1、HR和HP banks基本介紹

Xilinx的7系列FPGA有兩種IO Bank:HP(High Performace)和HR(High Range)。HP(high-performance)I/O banks的設(shè)計(jì)目的是為了獲取更高的Memory及chip-to-chip間的傳輸速率;而HR(high-range)I/O banks的設(shè)計(jì)目的是為了更寬的I/O電平標(biāo)準(zhǔn)。兩種BANK的IO口電壓不同,其中HR I/O Banks的VCCO電壓最大為3.3V,HP I/O banks的VCCO電壓最大為1.8V。特別是初次使用7系列時(shí),在硬件設(shè)計(jì)中特別要注意它們I/O口的最大工作電壓,一不注意就會(huì)把電壓搞錯(cuò),導(dǎo)致FPGA不能正常工作。

2、HR和HP banks的LVDS電平

當(dāng)兩個(gè)banks的I/O口作為LVDS電平時(shí),HR banks的I/O電壓VCCO只能為2.5V,HP banks的I/O口電壓為1.8V。兩個(gè)banks支持LVDS的標(biāo)準(zhǔn)不同,HR I/O banks的I/O只能分配LVDS_25標(biāo)準(zhǔn),HP分配為LVDS標(biāo)準(zhǔn)。

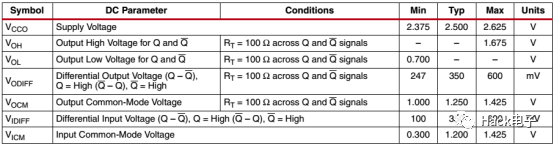

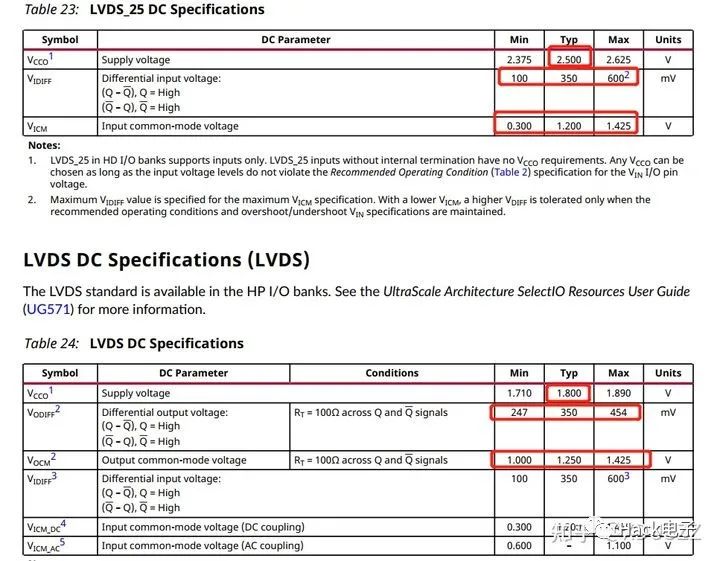

LVDS_25的直流特性如下表所示。

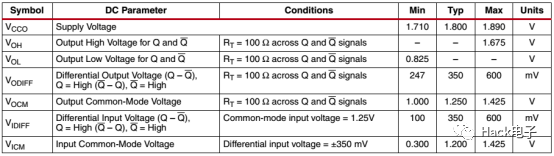

LVDS的直流特性如下表所示。

對(duì)比上述兩表可知,雖然LVDS_25和LVDS的bank的工作電壓不同,但是LVDS電平的直流特性一樣。高速AD/DA的LVDS工作電壓一般為1.8V,在初次使用7系列時(shí),一些硬件工程師可能擔(dān)心:HR bank的工作電壓為2.5V,那么HR bank的LVDS是否可以直接連接工作電壓為1.8V的AD/DA的LVDS接口,通過查看它們LVDS的直流特性,可知可以放心的直接連接。

3、HR banks電壓接錯(cuò)LVDS還能使用嗎

正如上述所描述,初次使用7系列的硬件工程師,需要把1.8V工作電壓AD/DA的LVDS接口連接到FPGA時(shí),設(shè)計(jì)人員把FPGA HR banks的I/O口電壓VCCO直接設(shè)計(jì)跟AD/DA I/O一樣的電壓為1.8V,由于沒有仔細(xì)查看FPGA的數(shù)據(jù)手冊(cè),導(dǎo)致設(shè)計(jì)存在缺陷。當(dāng)電路板加工、貼片回來才知道設(shè)計(jì)有問題時(shí),心里肯定忐忑不安,這樣低級(jí)錯(cuò)誤領(lǐng)導(dǎo)肯定得盤我了。此時(shí),千萬別慌張,不要想著立馬重來一版,想著如何可以彌補(bǔ),即使不能保證完全可用,也至少得驗(yàn)證一些功能,讓此版電路板有所價(jià)值,不能做出一版廢的電路板,這是大部分硬件工程師的愿望。筆者遇到過此問題,驗(yàn)證過即使HR I/O電壓設(shè)計(jì)為1.8V,同樣可以作為LVDS使用。也通過咨詢過Xilinx官方技術(shù)人員,I/O電壓主要影響LVDS的阻抗匹配。那么電壓不對(duì)就無法保證LVDS速率達(dá)到理論速率,具體能到多少速率那就看自己的“人品”了。

xilinx 7系列芯片不再支持LVDS33電平,在VCCO電壓為3.3V的情況下無法使用LVDS25接口。

有些設(shè)計(jì)者想通過在軟件中配置為LVDS25,實(shí)際供電3.3V來實(shí)現(xiàn)LVDS33也是無效的,原因是xilinx 7系列芯片在IO配置方面增加了過壓保護(hù),因而無法通過欺騙綜合軟件的方式強(qiáng)行配置IO,具體參見

7-Series SelectIO Resources Guide(https://www.xilinx.com/support/documentation/user_guides/ug471_7Series_SelectIO.pdf), page 100, Note 2 states:

"if the voltage exceeds 2.85V, the outputs will be in a high-Z state. The device should always be operated within the recommended operating range as specified in the 7 series FPGA data sheets."

雖然在VCCO為3.3V情況下無法輸出LVDS25,但可以作為輸入進(jìn)行使用,具體參見AR#43989 https://www.xilinx.com/support/answers/43989.html

即使VCCO電平不是1.8V,在HP I / O bank中也可以使用LVDS輸入。LVDS輸出(因此雙向LVDS)只能用于1.8V供電的組。

同樣,即使VCCO電平不是2.5V,也可以在HR I / O bank中使用LVDS_25輸入。LVDS_25輸出(因此雙向LVDS_25)只能用于2.5V供電的bank。

查了上述說法之后,我們自己試驗(yàn)下:

實(shí)驗(yàn)驗(yàn)證:

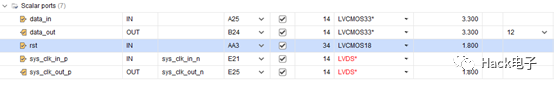

Bank14為HR Bank,差分輸入以及差分輸出使用LVDS電平:

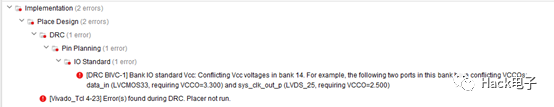

提示說明,LVDS電平不支持HRbank。

差分輸入以及差分輸出使用LVDS25電平:

提示VCCOs矛盾,輸出差分時(shí)鐘sys_clk_out_p,要求VCCO=2.5V,但對(duì)輸入并沒有這種要求。

驗(yàn)證了:

即使VCCO電平不是1.8V,在HP I / O bank中也可以使用LVDS輸入。LVDS輸出(因此雙向LVDS)只能用于1.8V供電的組。

同樣,即使VCCO電平不是2.5V,也可以在HR I / O bank中使用LVDS_25輸入。LVDS_25輸出(因此雙向LVDS_25)只能用于2.5V供電的bank。

官方更詳細(xì)說明:

1、Xilinx Customer Community

https://www.xilinx.com/support/answers/43989.html

2、Xilinx Customer Community

https://forums.xilinx.com/t5/Design-Entry/spartan7-power-wiring-LVDS-25/m-p/984802

//補(bǔ)充說明:FPGA中的 LVDS LVDS33 LVDS25

這僅僅是一種命名,對(duì)于XILINX FPGA來說,LVDS25意味著bank的供電電壓VCCO采用的是2.5V,LVDS33意味著bank的供電電壓VCCO采用的是3.3V,只是在代碼中使用LVDS信號(hào)時(shí),需要將管腳分別約束為LVDS25和LVDS33。但是!!FPGA引腳輸出的LVDS電平都是標(biāo)準(zhǔn)LVDS電平,一般共模電壓在1.25V,擺幅是350mV。下圖是FPGA官方給出的ds926手冊(cè),可以看到LVDS25和LVDS真的只是VCCO不同而導(dǎo)致的命名不同,但FPGA引腳輸出的電平都是標(biāo)準(zhǔn)LVDS。

這就會(huì)導(dǎo)致一些問題,經(jīng)常會(huì)有人問LVDS25、和LVDS33以及LVDS的芯片(或者FPGA約束)到底能不能兼容?答案是可以的,因?yàn)楝F(xiàn)在市面上正常情況下大部分公司的產(chǎn)品就只會(huì)用一種標(biāo)準(zhǔn)的LVDS電平,也就是上述所說的。因此,在這次和對(duì)外對(duì)接的時(shí)候,對(duì)方的LVDS芯片使用的是3.3V供電電壓,對(duì)方就說是自己的標(biāo)準(zhǔn)是LVDS33,而我這邊FPGA是在HP BANK產(chǎn)生的LVDS信號(hào),剛開始我也以為不兼容,但查看了網(wǎng)上的資料和對(duì)方使用的芯片的手冊(cè),也就發(fā)現(xiàn)了這個(gè)問題。一個(gè)小小的LVDS電平問題,直到今天遇到了問題才了解明白。

區(qū)別僅在于零件的內(nèi)部。

LVDS33需要3.3V Vcco,LVDS25需要2.5 Vcco(或者對(duì)于較新的部件,它可能使用Vccaux)。

引腳上的信號(hào)接口是相同的。

即兩種情況下的電壓擺幅和共模電壓相同,因此您可以將其視為LVDS。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1629文章

21754瀏覽量

604227 -

電壓

+關(guān)注

關(guān)注

45文章

5616瀏覽量

115947 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65848

原文標(biāo)題:Xilinx 7系FPGA LVDS使用要注意了,供電不能搞錯(cuò)

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

HP8590系列頻譜分析儀的維修技術(shù)

安捷倫 Agilent HP8595E 頻譜分析儀

HP3324A合成函數(shù)/掃描發(fā)生器操作和編程手冊(cè)

HR8825 STEP/DIR 微步進(jìn)電機(jī)驅(qū)動(dòng)芯片

安波福蘇州榮獲“2024大蘇州最佳雇主”及“2024最佳HR團(tuán)隊(duì)獎(jiǎng)”

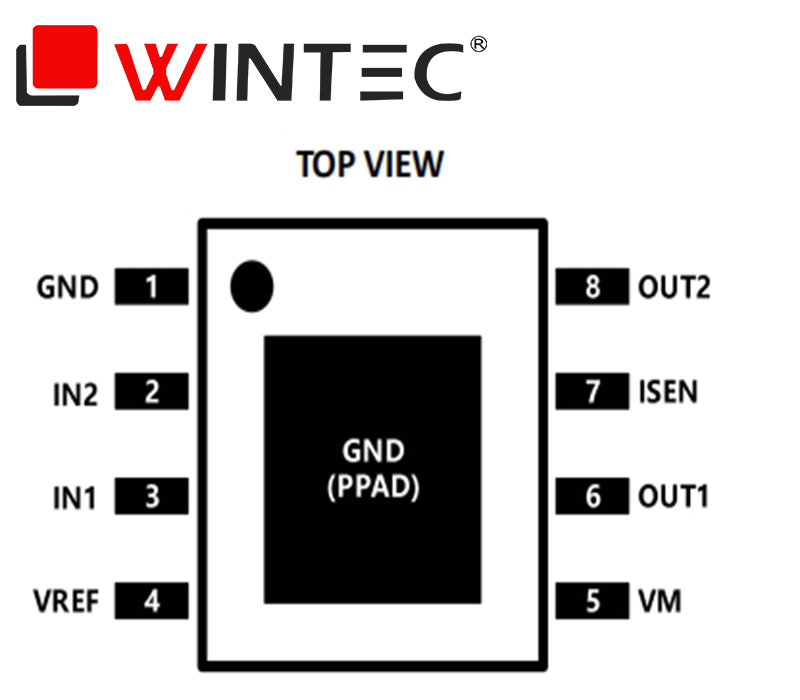

機(jī)器人里的直流有刷電機(jī)驅(qū)動(dòng)器資料:HR8870

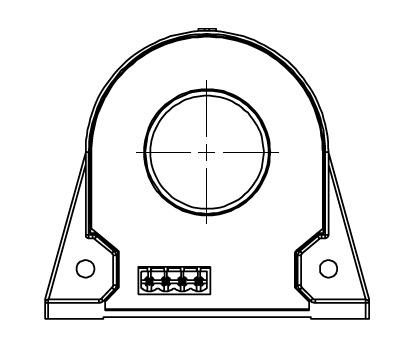

芯森HR1M H00系列充電樁用電流傳感器介紹

環(huán)保與高效并重:HP90三維激光切管機(jī)在綠色制造中的角色

機(jī)器人應(yīng)用選型推薦::HR8870直流有刷電機(jī)驅(qū)動(dòng)芯片

慧能泰推出HP1500+HP3500+HUSB338E 20W快充方案

毫末智行聯(lián)手高通推出HP370智能駕駛解決方案

HP1010–全球首款專用圖騰柱PFC數(shù)字控制器

?芯森電子HR1V H01開環(huán)電流傳感器介紹

慧能泰推出HP3000雙通道低側(cè)驅(qū)動(dòng)器

HR和HP banks基本介紹

HR和HP banks基本介紹

評(píng)論