1.時序分析工具

時序分析工具用來檢查同步電路設計是否滿足給定的時序約束(包括建立時間Setup約束、保持時間Hold約束等),分為靜態時序分析(Static Timing Analysis, DTA)兩種方法。

靜態時序分析是一種針對大規模門級電路進行時序驗證的有效方法。它不需要測試向量,根據單元庫中的時序模型和電路網表的拓撲結構,利用統計線網負載模型或SDF(Standard Delay Format,標準延時格式)文件中的電阻電容反標值計算時序路徑延遲,檢查每一個觸發器的建立和保持時間是否滿足設計要求。它的優點是覆蓋率高,速度快;缺點是不能分析異步邏輯電路和模擬電路。

靜態時序分析用工藝角(Corner)來反映不同的工藝/電壓/溫度等環境下電路的工作條件。工藝角下的單元庫中定義了單元的時序模型(包括時序延遲值和時序約束值)。理論上時序收斂要保證芯片在各個工作場景(Scenario)下都沒有時序違例,而實際操作中會選取某一個或幾個特殊的工藝角去檢查。

(1)單一模式:采用同一個工藝角條件,分析整個電路中時序路徑的建立時間和保持時間。

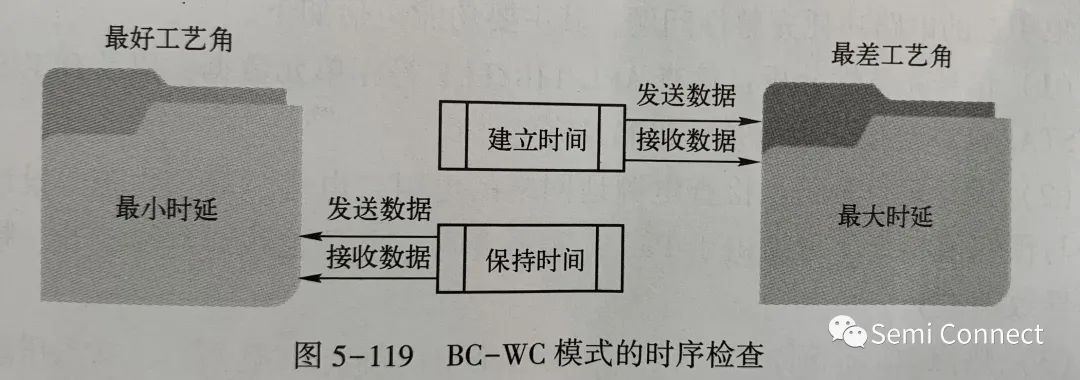

(2)BC- WC(Best-Case/Worst-Case)模式:用最好條件分析時序路徑的保持時間,用最差條件分析時序路徑的建立時間。BC- WC模式的時序檢查如圖5-119所示。

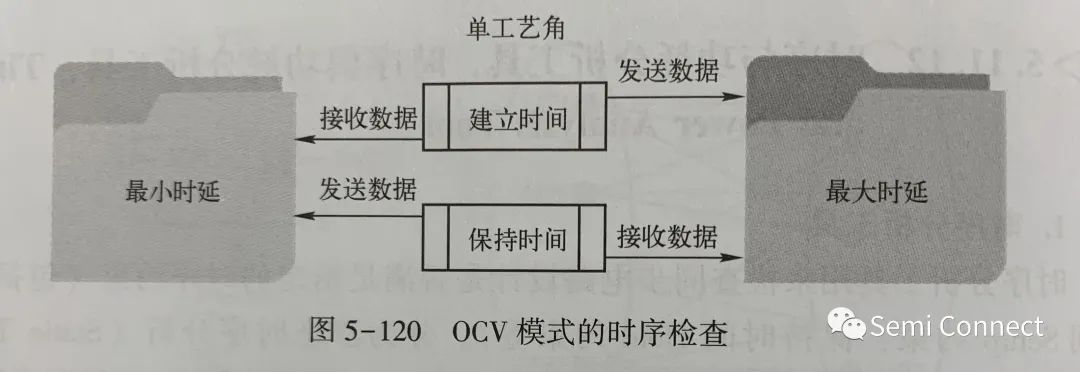

(3)OCV(On-Chip Variation)模式:利用放大及縮小倍數,分析建立時間時,令數據路徑傳輸慢一些,時鐘路徑傳輸快一些;分析保持時間時,令數據路徑傳輸快一些,時鐘路徑傳輸慢一些。OCV模式的時序檢查如圖5-120所示。

在28nm及更先進工藝條件下,新出現的AOCV(Advanced OCV)方法對OCV進行了擴展和延伸。它消除了OCV的不利因素,根據時序路徑的不同邏輯層次深度和物理距離,查表得到每個單元具體的時延值。

為了應對芯片內部及芯片之間出現的系統性和隨機性變化,時序分析工具又引入了統計靜態時序分析(Statistical Static Timing Analysis,SSTA)方法。該方法利用概率分布函數,計算每個節點上每個信號的到達時間以減少不必要的時序過度修正。SSTA方法的難點在于概率函數難以計算,而且龐大的統計數據也造成了內存需求量增大,運行時間增長。

在16nm工藝條件以下的SoC設計以及物聯網(IoT)超低電壓設計中,以工藝角時延為基礎的STA計算已經不再準確,而需要采用基于晶體管級仿真的動態時序分析方法。該方法采用并行化處理和特殊加速技術,針對關鍵時序路徑進行高精度快速仿真,以獲得時序路徑準確的時序信息,幫助時序收斂。

2.功耗分析工具

功耗分析工具用于對電路中的溫度、翻轉頻率、負載、電流、電壓、功耗等進行統計報告,分析IR壓降(IR-Drop)和電遷移(Electro Migration,EM)等現象引起的電路功耗完整性問題,其主要功能包括如下。

(1)信號完整性分析:檢查APL/LIB/LEF等庫單元數據,以及DEF/SPEF/IPF/STA/VCD等設計數據是否正確且完整。

(2)設計弱點分析:檢查電源地網絡的電阻、電容、峰值電流等設計指標是否與預期值相符(可能由于Pad分布不合理、電源地線布線不優化、頻率過高等導致偏差)。

(3)熱點(Hot Spot)分析:檢查電路中的靜態電阻電流、動態壓降、功耗、電遷移等相關項是否滿足簽核標準,如有違反則定位問題所在區域并追溯其原因。

審核編輯 :李倩

-

觸發器

+關注

關注

14文章

2000瀏覽量

61158 -

時序

+關注

關注

5文章

387瀏覽量

37333

原文標題:可編程邏輯電路設計—時序與功耗分析工具

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字電路基礎教程之時序邏輯電路的詳細資料概述

數字電路教程之時序邏輯電路課件的詳細資料免費下載

模擬電路教程之時序邏輯電路的課件資料免費下載

可編程邏輯電路設計之時序與功耗分析工具

可編程邏輯電路設計之時序與功耗分析工具

評論