1、什么是I2C協議

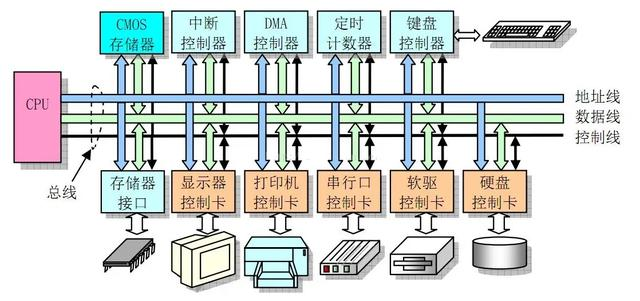

I2C協議是一個允許多個 “從機” 芯片和一個或更多的 “主機” 芯片進行通訊的協議。它就像串行外設接口(SPI)一樣,只能用于短距離通信。又像異步串行接口(如RS232或UART), 只需要兩根信號線來交換信息。

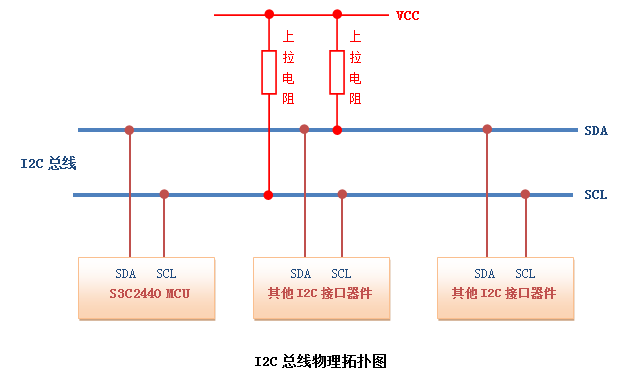

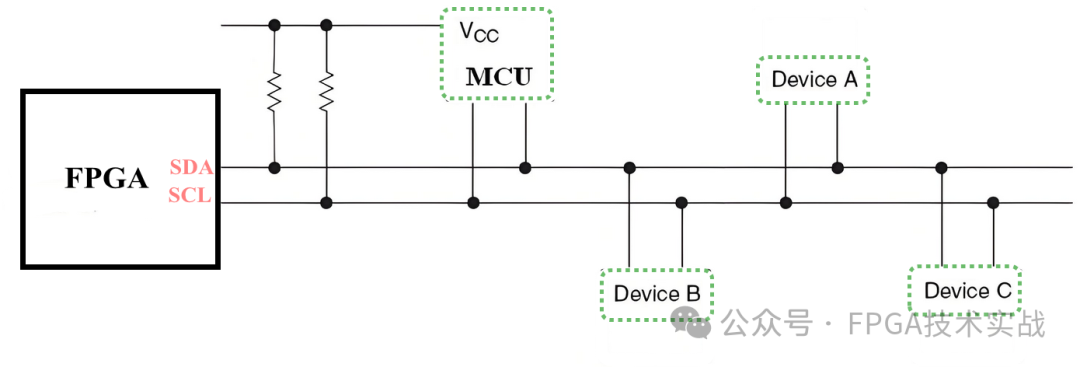

實現I2C需要兩根信號線完成信息交換,SCL時鐘信號線,SDA數據輸入/輸出線。它屬于同步通信,由于輸入輸出數據均使用一根線,因此通信方向為半雙工。

總結:短距離、一主多從、半雙工、兩根線、同步通訊

2、名詞解釋

什么是半雙工呢?什么是同步通訊?什么是異步通訊?

2.1 什么是半雙工?

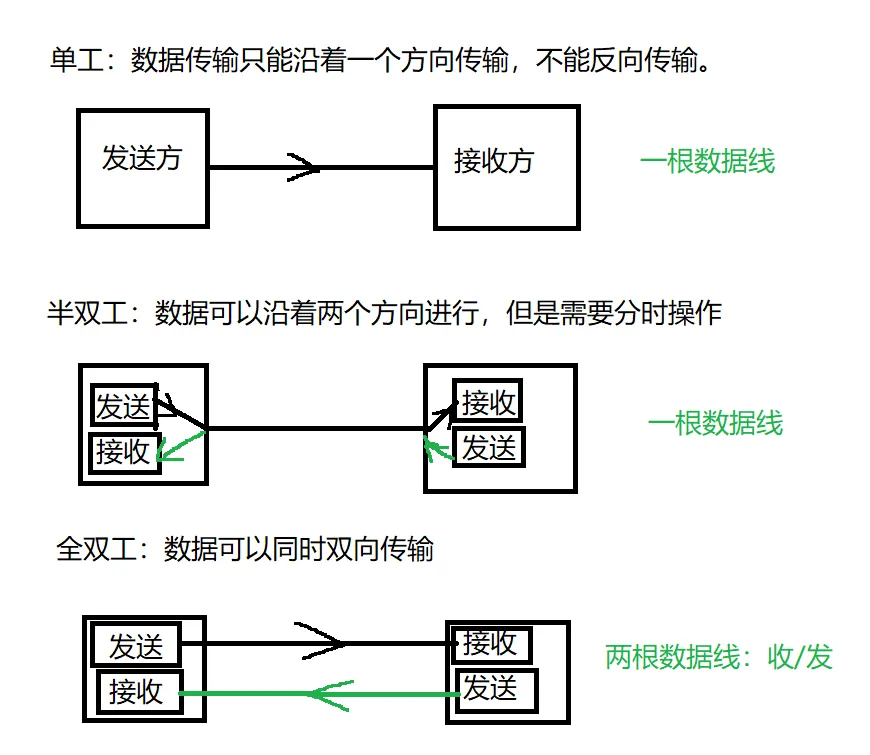

數據通信中,數據在線路上的傳送方式可以分為單工通信、半雙工通信和全雙工通信三種。

單工通信: 是指消息只能單方向傳輸的工作方式。例如遙控、遙測(一部分),就是單工通信方式。單工通信信道是單向信道,發送端和接收端的身份是固定的,發送端只能發送信息,不能接收信息;接收端只能接收信息,不能發送信息,數據信號僅從一端傳送到另一端,即信息流是單方向的。

半雙工: 是指數據可以沿兩個方向傳送,但同一時刻一個信道只允許單方向傳送,因此又被稱為雙向交替通信。(信息在兩點之間能夠在兩個方向上進行發送,但不能同時發送的工作方式。)半雙工方式要求收發兩端都有發送裝置和接收裝置。由于這種方式要頻繁變換信道方向,故效率低,但可以節約傳輸線路。

全雙工: 是指在通信的任意時刻,線路上可以同時存在A到B和B到A的雙向信號傳輸。在全雙工方式下,通信系統的每一端都設置了發送器和接收器,因此,能控制數據同時在兩個方向上傳送。全雙工方式無需進行方向的切換,因此,沒有切換操作所產生的時間延遲,這對那些不能有時間延誤的交互式應用(例如遠程監測和控制系統)十分有利。比如,電話機則是一種全雙工設備,其通話雙方可以同時進行對話。

2.2 什么是同步通訊

同步通信: 發送端在發送串行數據的同時,提供一個時鐘信號,并按照一定的約定(例如:在時鐘信號的上升沿的時候,將數據發送出去)發送數據,接收端根據發送端提供的時鐘信號,以及大家的約定,接收數據。如:I2C、SPI等有時鐘信號的協議,都屬于這種通信方式。

異步通信: 接收方并不知道數據什么時候會到達,收發雙方可以有各自自己的時鐘。發送方發送的時間間隔可以不均,接收方是在數據的起始位和停止位的幫助下實現信息同步的。這種傳輸通常是很小的分組,比如:一個字符為一組,數據組配備起始位和結束位。所以這種傳輸方式的效率是比較低的,因為額外加入了很多的輔助位作為負載,常用在低速的傳輸中。

同步通信與異步通信區別:

(1)同步通信要求接收端時鐘頻率和發送端時鐘頻率一致,發送端發送連續的比特流;異步通信時不要求接收端時鐘和發送端時鐘同步,發送端發送完一個字節后,可經過任意長的時間間隔再發送下一個字節。

(2)同步通信效率高,異步通信效率較低。

(3)同步通信較復雜,雙方時鐘的允許誤差較小;異步通信簡單,雙方時鐘可允許一定誤差。

(4)同步通信可用于點對多點;異步通信只適用于點對點。

3、I2C的功能特點

I2C最重要的功能包括:

只需要兩條總線;

沒有嚴格的波特率要求,例如使用RS232,主設備生成總線時鐘;

所有組件之間都存在簡單的主/從關系,連接到總線的每個設備均可通過唯一地址進行軟件尋址;

I2C是真正的多主設備總線,可提供仲裁和沖突檢測;

傳輸速度:

標準模式:Standard Mode = 100 Kbps

快速模式:Fast Mode = 400 Kbps

高速模式:High speed mode = 3.4 Mbps

超快速模式:Ultra fast mode = 5 Mbps

最大主設備數:無限制;

最大從機數:理論上是127;

4、I2C的高阻態

漏極開路(Open Drain)即高阻狀態,適用于輸入/輸出,其可獨立輸入/輸出低電平和高阻狀態,若需要產生高電平,則需使用外部上拉電阻

高阻狀態:高阻狀態是三態門電路的一種狀態。邏輯門的輸出除有高、低電平兩種狀態外,還有第三種狀態——高阻狀態的門電路。電路分析時高阻態可做開路理解。

我們知道IIC的所有設備是接在一根總線上的,那么我們進行通信的時候往往只是幾個設備進行通信,那么這時候其余的空閑設備可能會受到總線干擾,或者干擾到總線,怎么辦呢?

為了避免總線信號的混亂,IIC的空閑狀態只能有外部上拉, 而此時空閑設備被拉到了高阻態,也就是相當于斷路, 整個IIC總線只有開啟了的設備才會正常進行通信,而不會干擾到其他設備。

5、數據傳輸協議

主設備和從設備進行數據傳輸時遵循以下協議格式。數據通過一條SDA數據線在主設備和從設備之間傳輸0和1的串行數據。串行數據序列的結構可以分為:

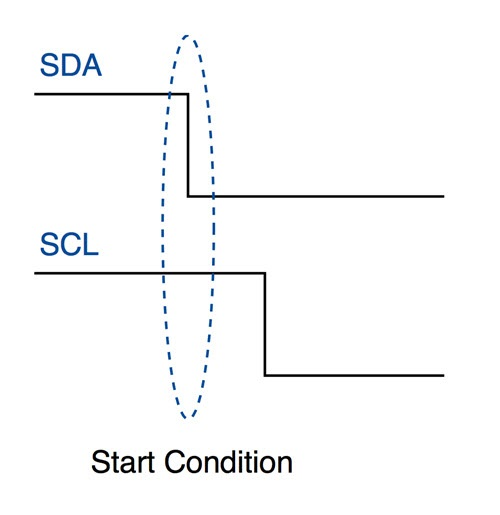

5.1 開始位

當主設備決定開始通訊時,需要發送開始信號,并且執行以下過程:

將SDA線由高電平切換成低電平;

將SCL線由高電平切換成低電平;

在主設備發送開始條件信號之后,所有從機即使處于睡眠模式也將變為活動狀態,并等待接收地址位。

5.2 地址位

地址位支持7bit、10bit,主設備如果需要向從機發送/接收數據,首先要發送對應從機的地址,然后會匹配總線上掛載的從機的地址,故地址為主要用來辨識不同設備。

地址位由主機發送,從設備負責接受并識別該地址是否位自己地址。

5.3 讀寫位

由于I2C是半雙工通訊,所以設備需要確定數據傳輸的方向,故引入了讀寫位。

如果主設備需要將數據發送到從設備,則該位設置為 0;

如果主設備需要往從設備接收數據,則將其設置為 1 ;

讀寫位由主機發送;1表示讀操作,0表示寫操作。

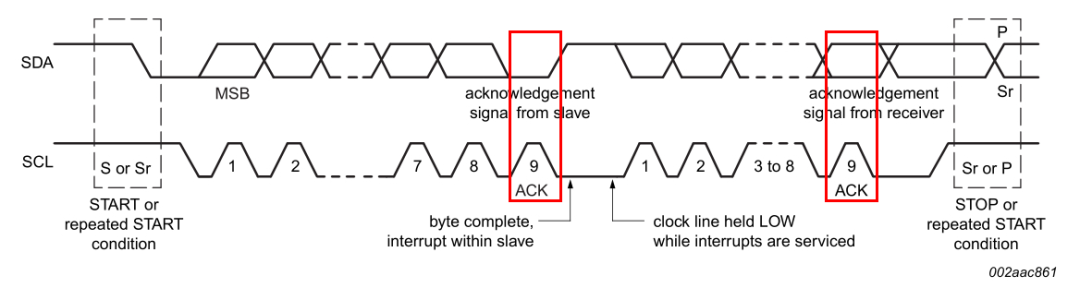

5.4 應答位

I2C最大的一個特點就是有完善的應答機制,從機接收到主機的數據時,會回復一個應答信號來通知主機表示“我收到了”。

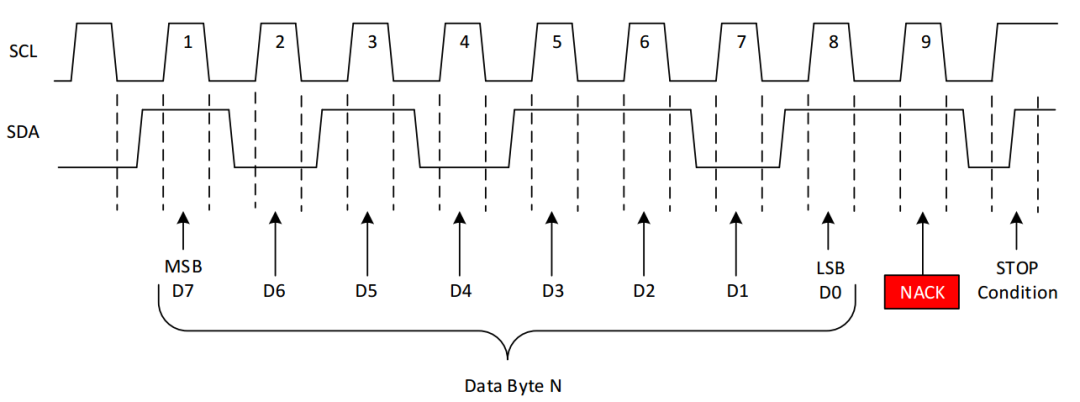

應答信號: 出現在1個字節傳輸完成之后,即第9個SCL時鐘周期內,此時主機需要釋放SDA總線,把總線控制權交給從機,由于上拉電阻的作用,此時總線為高電平,如果從機正確的收到了主機發來的數據,會把SDA拉低,表示應答響應。

非應答信號:當第9個SCL時鐘周期時,SDA保持高電平,表示非應答信號。

非應答信號可能是主機產生也可能是從機產生,產生非應答信號的情況主要有以下幾種:

I2C總線上沒有主機所指定地址的從機設備;

從機正在執行一些操作,處于忙狀態,還沒有準備好與主機通訊;

主機發送的一些控制命令,從機不支持;

主機接收從機數據時,主機產生非應答信號,通知從機數據傳輸結束,不要再發數據了;

5.5 數據位

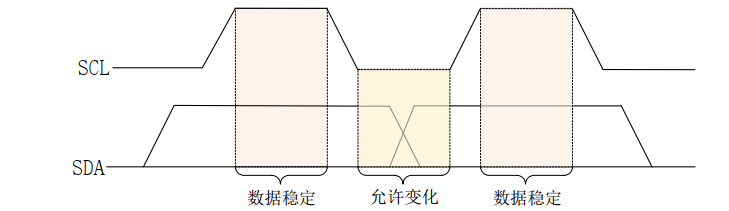

I2C數據總線傳輸要保證在SCL為高電平時,SDA數據穩定,所以SDA上數據變化只能在SCL為低電平時

一次傳輸的數據總共有8位,由發送方設置,它需要將數據位傳輸到接收方。發送之后會緊跟一個ACK / NACK位,如果接收器成功接收到數據,則從機發送ACK。否則,從機發送NACK。

數據可以重復發送多個,直到接收到停止位為止。

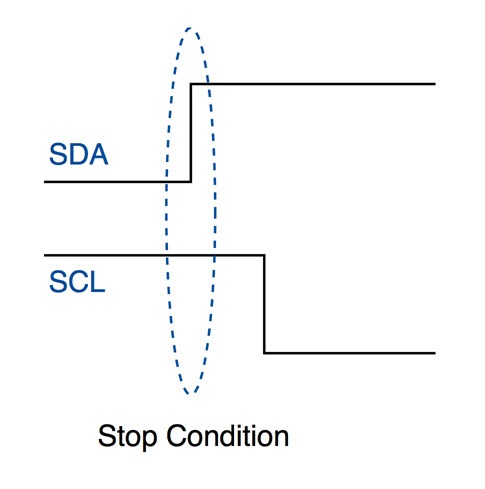

5.6 停止位

當主設備決定結束通訊時,需要發送結束信號,需要執行以下動作:

先將SDA線從低電壓電平切換到高電壓電平;

再將SCL線從高電平拉到低電平;

5.7 總結

寫寄存器的標準流程為:

Master發起START

Master發送I2C addr(7bit)和w操作0(1bit),等待ACK

Slave發送ACK

Master發送reg addr(8bit),等待ACK

Slave發送ACK

Master發送data(8bit),即要寫入寄存器中的數據,等待ACK

Slave發送ACK

第6步和第7步可以重復多次,即順序寫多個寄存器

Master發起STOP

讀寄存器的標準流程為:

Master發送I2C addr(7bit)和w操作1(1bit),等待ACK

Slave發送ACK

Master發送reg addr(8bit),等待ACK

Slave發送ACK

Master發起START

Master發送I2C addr(7bit)和r操作1(1bit),等待ACK

Slave發送ACK

Slave發送data(8bit),即寄存器里的值

Master發送ACK

第8步和第9步可以重復多次,即順序讀多個寄存器

6、仲裁機制

在多主的通信系統中。總線上有多個節點,它們都有自己的尋址地址,可以作為從節點被別的節點訪問,同時它們都可以作為主節點向其他的節點發送控制字節和傳送數據。

但是如果有兩個或兩個以上的節點都向總線上發送啟動信號并開始傳送數據,這樣就形成了沖突。要解決這種沖突,就要進行仲裁的判決,這就是I2C總線上的仲裁。

I2C總線上的仲裁分兩部分:SCL線的同步和SDA線的仲裁。

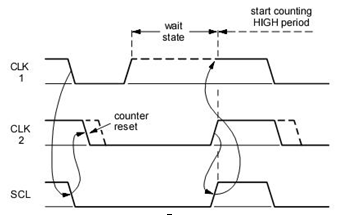

6.1 SCL線的同步

SCL同步是由于總線具有線 “與” 的邏輯功能(開漏輸出),即只要有一個節點發送低電平時,總線上就表現為低電平。當所有的節點都發送高電平時,總線才能表現為高電平。正是由于線“與”邏輯功能的原理,當多個節點同時發送時鐘信號時,在總線上表現的是統一的時鐘信號,這就是SCL的同步原理。

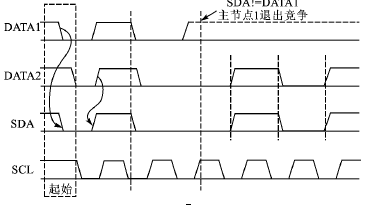

6.2 SDA線的仲裁

總線仲裁是為了解決多設備同時競爭中線控制權的問題,通過一定的裸機來決定哪個設備能夠獲得最終的總線控制權。

SDA線的仲裁也是建立在總線具有線“與”邏輯功能的原理上的。節點在發送1位數據后,比較總線上所呈現的數據與自己發送的是否一致(類似于CAN總線的回讀機制)。

是,繼續發送;

否則,退出競爭;

I2C總線的控制邏輯:低電平優先

SDA線的仲裁可以保證I2C總線系統在多個主節點同時企圖控制總線時通信正常進行并且數據不丟失,總線系統通過仲裁只允許一個主節點可以繼續占據總線。

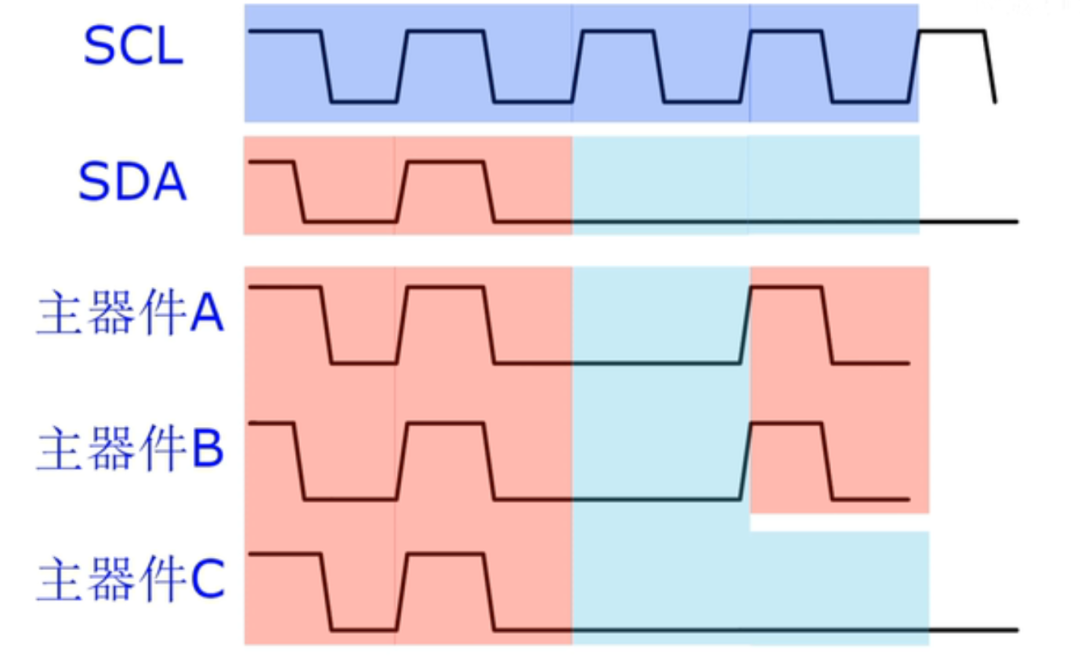

上圖過程分析:

第一個周期:所有設備發送1,做與運算后的結果為1,與自己發送的數據相同,繼續發送; 第二個周期:所有設備發送1,做與運算后的結果為1,與自己發送的數據相同,繼續發送; 第三個周期:所有設備發送0,做與運算后的結果為0,與自己發送的數據相同,繼續發送; 第四個周期:AB設備發送1,C設備發送0,做與運算后結果為0,與AB發送的數據不同,則AB退出競爭,節點C獲勝; 注:若AB兩個設備發送0,C設備發送1,這最后與運算結果為0,與AB數據格式相同,與C數據格式不同,則C退出,AB繼續發送,直至AB中有一個退出。

SDA仲裁和SCL時鐘同步處理過程沒有先后關系,而是同時進行的。

7、I2C死鎖

在實際使用過程中,I2C比較容易出現的一個問題就是死鎖 ,死鎖在I2C中主要表現為:I2C死鎖時表現為SCL為高,SDA一直為低。

在I2C主設備進行讀寫操作的過程中,主設備在開始信號后控制SCL產生8個時鐘脈沖,然后拉低SCL信號為低電平,在這個時候,從設備輸出應答信號,將SDA信號拉為低電平。

如果這個時候主設備異常復位,SCL就會被釋放為高電平。此時,如果從設備沒有復位,就會繼續I2C的應答,將SDA一直拉為低電平,直到SCL變為低電平,才會結束應答信號。

而對于I2C主設備來說,復位后檢測SCL和SDA信號,如果發現SDA信號為低電平,則會認為I2C總線被占用,會一直等待SCL和SDA信號變為高電平。

這樣,I2C主設備等待從設備釋放SDA信號,而同時I2C從設備又在等待主設備將SCL信號拉低以釋放應答信號,兩者相互等待,I2C總線進人一種死鎖狀態。

同樣,當I2C進行讀操作,I2C從設備應答后輸出數據,如果在這個時刻I2C主設備異常復位而此時I2C從設備輸出的數據位正好為0,也會導致I2C總線進入死鎖狀態。

8、I2C的代碼實現

參考了STM32的HAL庫中I2C驅動,主設備發送函數HAL_I2C_Master_Transmit()具體如下:

/** *@briefTransmitsinmastermodeanamountofdatainblockingmode. *@paramhi2cPointertoaI2C_HandleTypeDefstructurethatcontains *theconfigurationinformationforthespecifiedI2C. *@paramDevAddressTargetdeviceaddress:Thedevice7bitsaddressvalue *indatasheetmustbeshiftedtotheleftbeforecallingtheinterface *@parampDataPointertodatabuffer *@paramSizeAmountofdatatobesent *@paramTimeoutTimeoutduration *@retvalHALstatus */ HAL_StatusTypeDefHAL_I2C_Master_Transmit(I2C_HandleTypeDef*hi2c, uint16_tDevAddress, uint8_t*pData, uint16_tSize, uint32_tTimeout){ uint32_ttickstart=0x00U; /*Inittickstartfortimeoutmanagement*/ tickstart=HAL_GetTick(); if(hi2c->State==HAL_I2C_STATE_READY){ /*WaituntilBUSYflagisreset*/ if(I2C_WaitOnFlagUntilTimeout(hi2c,I2C_FLAG_BUSY,SET,I2C_TIMEOUT_BUSY_FLAG,tickstart)!=HAL_OK){ returnHAL_BUSY; } /*ProcessLocked*/ __HAL_LOCK(hi2c); /*CheckiftheI2Cisalreadyenabled*/ if((hi2c->Instance->CR1&I2C_CR1_PE)!=I2C_CR1_PE){ /*EnableI2Cperipheral*/ __HAL_I2C_ENABLE(hi2c); } /*DisablePos*/ hi2c->Instance->CR1&=~I2C_CR1_POS; hi2c->State=HAL_I2C_STATE_BUSY_TX; hi2c->Mode=HAL_I2C_MODE_MASTER; hi2c->ErrorCode=HAL_I2C_ERROR_NONE; /*Preparetransferparameters*/ hi2c->pBuffPtr=pData; hi2c->XferCount=Size; hi2c->XferOptions=I2C_NO_OPTION_FRAME; hi2c->XferSize=hi2c->XferCount; /*SendSlaveAddress*/ if(I2C_MasterRequestWrite(hi2c,DevAddress,Timeout,tickstart)!=HAL_OK){ if(hi2c->ErrorCode==HAL_I2C_ERROR_AF){ /*ProcessUnlocked*/ __HAL_UNLOCK(hi2c); returnHAL_ERROR; }else{ /*ProcessUnlocked*/ __HAL_UNLOCK(hi2c); returnHAL_TIMEOUT; } } /*ClearADDRflag*/ __HAL_I2C_CLEAR_ADDRFLAG(hi2c); while(hi2c->XferSize>0U){ /*WaituntilTXEflagisset*/ if(I2C_WaitOnTXEFlagUntilTimeout(hi2c,Timeout,tickstart)!=HAL_OK){ if(hi2c->ErrorCode==HAL_I2C_ERROR_AF){ /*GenerateStop*/ hi2c->Instance->CR1|=I2C_CR1_STOP; returnHAL_ERROR; }else{ returnHAL_TIMEOUT; } } /*WritedatatoDR*/ hi2c->Instance->DR=(*hi2c->pBuffPtr++); hi2c->XferCount--; hi2c->XferSize--; if((__HAL_I2C_GET_FLAG(hi2c,I2C_FLAG_BTF)==SET) &&(hi2c->XferSize!=0U)){ /*WritedatatoDR*/ hi2c->Instance->DR=(*hi2c->pBuffPtr++); hi2c->XferCount--; hi2c->XferSize--; } /*WaituntilBTFflagisset*/ if(I2C_WaitOnBTFFlagUntilTimeout(hi2c,Timeout,tickstart)!=HAL_OK){ if(hi2c->ErrorCode==HAL_I2C_ERROR_AF){ /*GenerateStop*/ hi2c->Instance->CR1|=I2C_CR1_STOP; returnHAL_ERROR; }else{ returnHAL_TIMEOUT; } } } /*GenerateStop*/ hi2c->Instance->CR1|=I2C_CR1_STOP; hi2c->State=HAL_I2C_STATE_READY; hi2c->Mode=HAL_I2C_MODE_NONE; /*ProcessUnlocked*/ __HAL_UNLOCK(hi2c); returnHAL_OK; }else{ returnHAL_BUSY; } }

審核編輯:劉清

-

串行接口

+關注

關注

3文章

328瀏覽量

42613 -

SPI接口

+關注

關注

0文章

258瀏覽量

34382 -

高電平

+關注

關注

6文章

149瀏覽量

21385 -

I2C協議

+關注

關注

0文章

26瀏覽量

8475

原文標題:一文帶你讀懂I2C協議

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RISC V的I2C操作

具有熱插拔功能和IEC ESD功能的隔離式I2C緩沖器如何改進隔離式I2C

簡單認識I2C通信協議

I2C總線協議的工作原理和尋址格式

SPI和I2C通信協議:應用與區別

什么是I2C協議 I2C總線的控制邏輯

什么是I2C協議?I2C的功能特點有哪些

什么是I2C協議?I2C的功能特點有哪些

評論