前陣子寫過一篇文章《如何才能半導體雪崩中活下來》,然后昨天任老爺子就發布了講話,即接下來是全球經濟衰退期,為了保證度過未來三年的“經濟”危機,縮減業務,核心聚焦,不再關注銷售額,而是現金流/利潤為王。

為了活下來,我們可以躺平;我們需要臥薪嘗膽,既然不適合去轟轟烈烈趕一把,我們反而可以利用這段時間,臥薪嘗膽,好好學習。前陣子出差+工作耽擱了下,內心無比愧疚,今天重新開始學習分享FPGA知識,歡迎各位斧正。

拿來主義的好處就是,相對效率會更高一點,并且試錯成本還低很多。那么在此感謝原廠FAE王奇搶先一步在我的開發板商移植HDMI,讓我們在易靈思Ti60 FPGA上一睹為快。

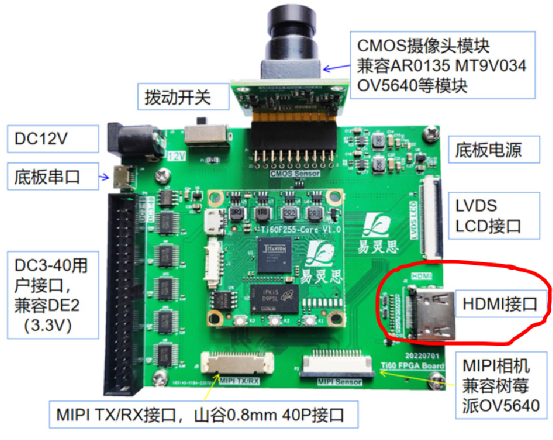

易靈思鈦金系列FPGA Ti60F255的開發板,出爐已經有一些日子了,板載HDMI電路理論上是成熟的(別家FPGA上我驗證過),但卻一直沒能擠出時間來移植一下HDMI 1.4的顯示方案,今天我們就來挑戰一下IO模擬1080P60,把易靈思Ti60 FPGA干到750MHz主頻!

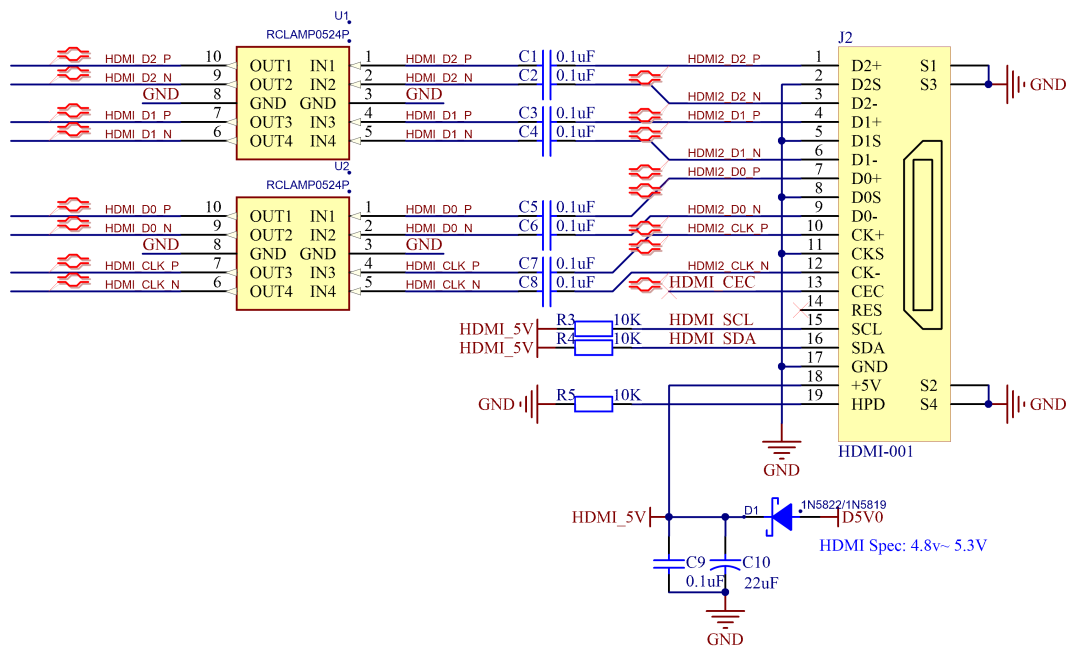

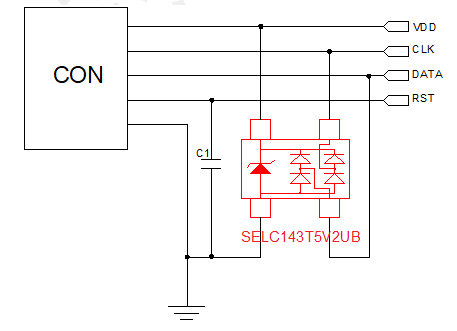

這部分采用FPGA模擬的話,電路其實非常簡單,加了EMC芯片后的原理圖如下所示。

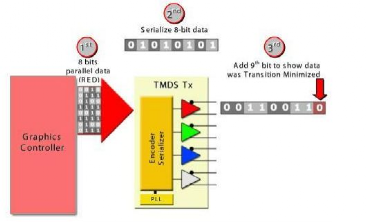

HDMI 采用和 DVI 相同的傳輸原理——TMDS最小化傳輸差分信號。TMDS 傳輸系統分為兩個部分:發送端和接收端。TMDS 發送端收到HDMI 接口傳來的24bit RGB信號,然后對這些數據進行編碼和并/串轉換,再將RGB 信號的數據分別分配到獨立的傳輸通道發送出去。接收端接收來自發送端的串行信號,對其進行解碼和串/并轉換,然后發送到顯示器的控制端;與此同時也接收時鐘信號,以實現同步。

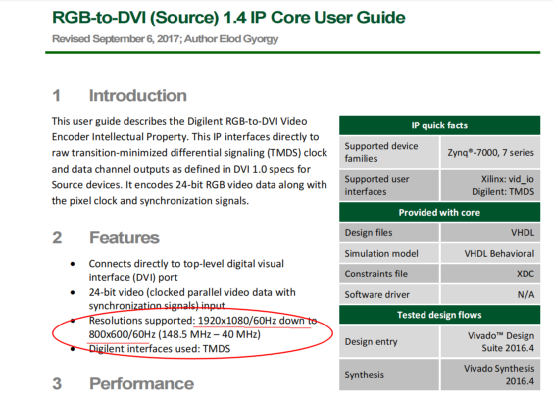

網上很多FPGA模擬HDMI PHY的設計,可參見https://zhuanlan.zhihu.com/p/435937460。其中以Digilent的HDMI IP最為常見,其采用VHDL模擬TMDS,用FPGA實現HDMI的收發,節省了外部PHY芯片的成本(https://github.com/Digilent/vivado-library)。

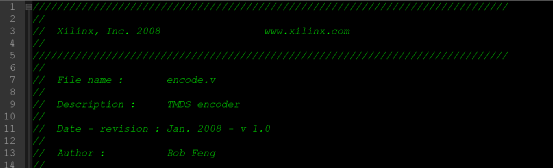

Digilent HDMI IP方案,后來很多朋友其他平臺上都有移植,我也在Xilinx和安路上都有移植測到過,其采用VHDL實現,稍微有點復雜。不過今天我將在FAE王奇的基礎上,消化吸收另一個HDMI tx ip(采用Verilog編寫,結構很簡單),在易靈思Ti60 FPGA挑戰下1080P60(其實主頻主要還是看收發器的速率)。這里也感謝這個HDMI IP創作者的勞動果實,Verilog Header如下:

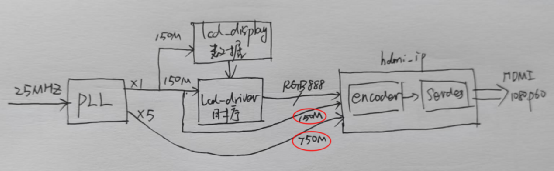

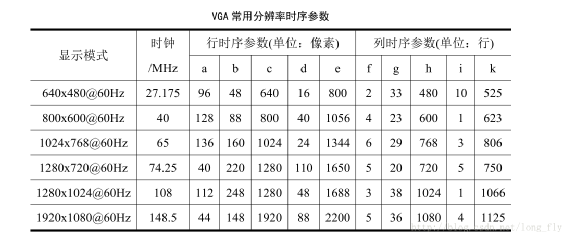

給出目前的框圖,如下所示,外部輸入25M,由Interface的PLL生成150/750MHz(離開148.5MHz有點偏差也沒關系),hdmi_ip接收前面測試的RGB數據后,模擬HDMI協議發送給外部,在顯示器上顯示。由于TMDS用10bit編碼,FPGA采用DDR模式進行數據發送,因此當串行時鐘是像素時鐘的10/2=5倍。

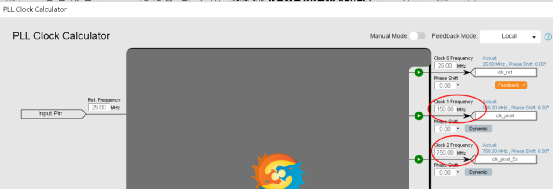

我們在Interface中配置PLL,這里輸入25M,輸出150+750MHz,如下圖所示:

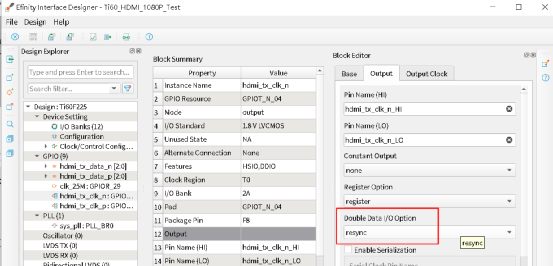

另外,這里的關鍵是我們采用易靈思的Double Data IO,配置如下,這里將hdmi_tx_data和hdmi_tx_clk都打開了resync模式:

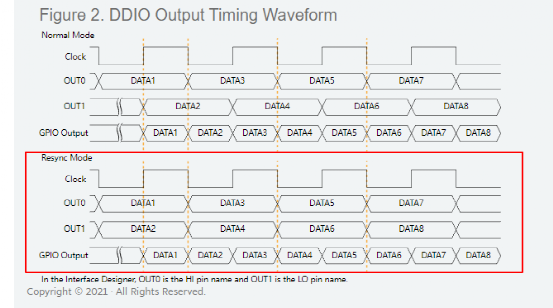

查詢Efinity help文檔,可以看到DDIO的Resync Mode,用戶在Clock下降沿輸入OUT0+OUT1,GPIO在上升沿輸出OUT0,在Clock下降沿輸出OUT1,從而達到了倍頻的目的(這里的HI就是OUT0,LO就是OUT1)。

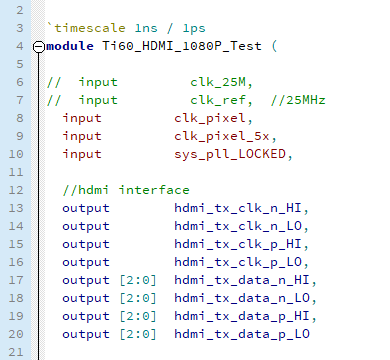

那么在代碼中,我們需要驅動GPIO DDIO前的HI與LO,我們的頂層代碼如下:

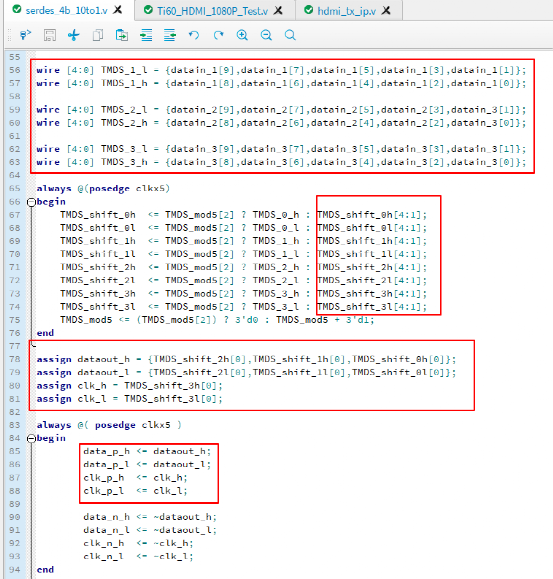

這部分通過serdes_4b_10to1.v文件編碼輸出,相關代碼如下所示:

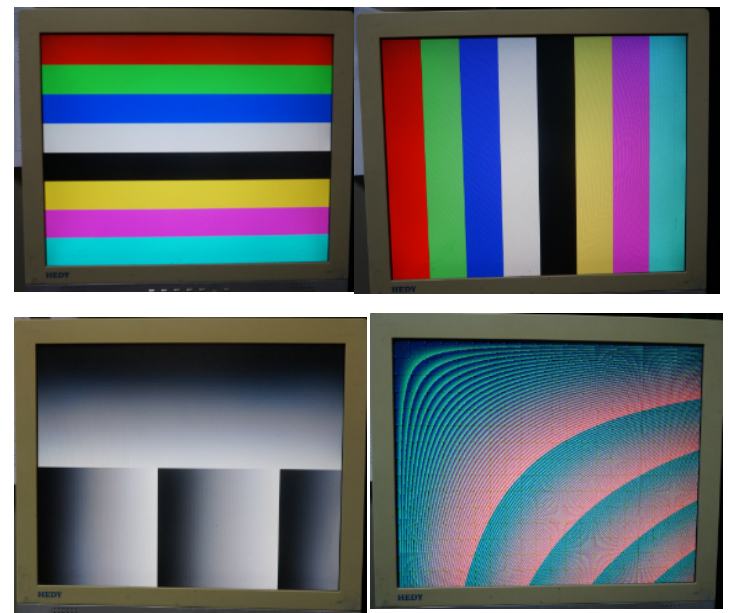

最后,采用Efinity進行綜合,上圖中的邏輯跑到了750MHz,DDIO實現了1.5Gbps的帶寬。DDIO 1.5Gbps已經是易靈思的瓶頸了,雖然時序有一點小違例(150M到750M跨時鐘域部分電路),但是HDMI 1080P60已經成功顯示,如下所示(盜用8年前的圖,懶得拍)。

本來打算移植LVDS模式,但是頻率上不去,目前懷疑HDMI電路還得加上拉電阻,當前版本省略了,以后有機會再試試。下一步,上T35移植HDMI測試一下能跑到多少頻率,至少應該能跑720P吧?

審核編輯 :李倩

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604316 -

HDMI

+關注

關注

32文章

1719瀏覽量

152077 -

易靈思

+關注

關注

5文章

47瀏覽量

4889

原文標題:如何將易靈思FPGA干到750MHz(1080P顯示)

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用TVP7002采集VGA輸出的1080P信號源,顯示分辨率顯示的是1920*1080@60Hz,為什么會有黑框顯示?

DS90UB913A-Q1是否支持像素時鐘74.25MHz的1080p 30的分辨率?

給DM8168兩路視頻數據1080P和640x480逐行,在正常運行一段時間后640x480就沒數據了,是什么原因導致的?

易靈思FPGA產品的主要特點

DLP?顯示≥0.47英寸陣列WUXGA/1080p/WXGA/XGA/SVGA評估模塊

帶HDCP的DS90UH947-Q1 1080p OpenLDI到FPD-link III串行器數據表

DS90UB940-Q1 1080p FPD-link III至CSI-2解串器數據表

DS90UB947-Q1 1080p OpenLDI到FPD-link III串行器數據表

TIDA-080009-采用 DLP? 技術的便攜式超小型 1080p顯示屏 PCB layout 設計

國產FPGA應用專題--易靈思Efinity軟件使用心得

如何將易靈思FPGA干到750MHz(1080P顯示)

如何將易靈思FPGA干到750MHz(1080P顯示)

評論