問題描述

在抓信號過程中,想看的信號忘記抓了,如果重新抓取的話將會重新走一遍綜合、實現過程,浪費極大時間,漏抓的信號就1bit,實在不值得重新再跑一遍程序。

解決方法

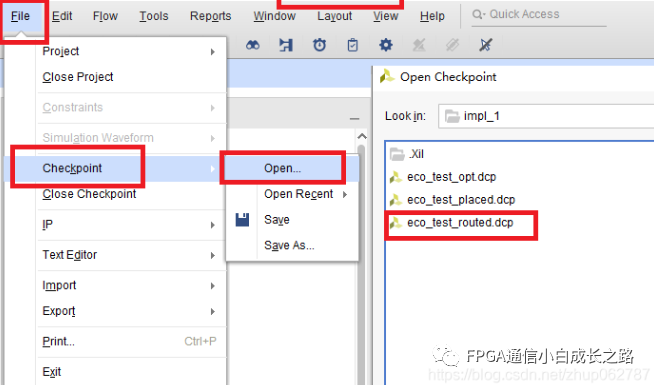

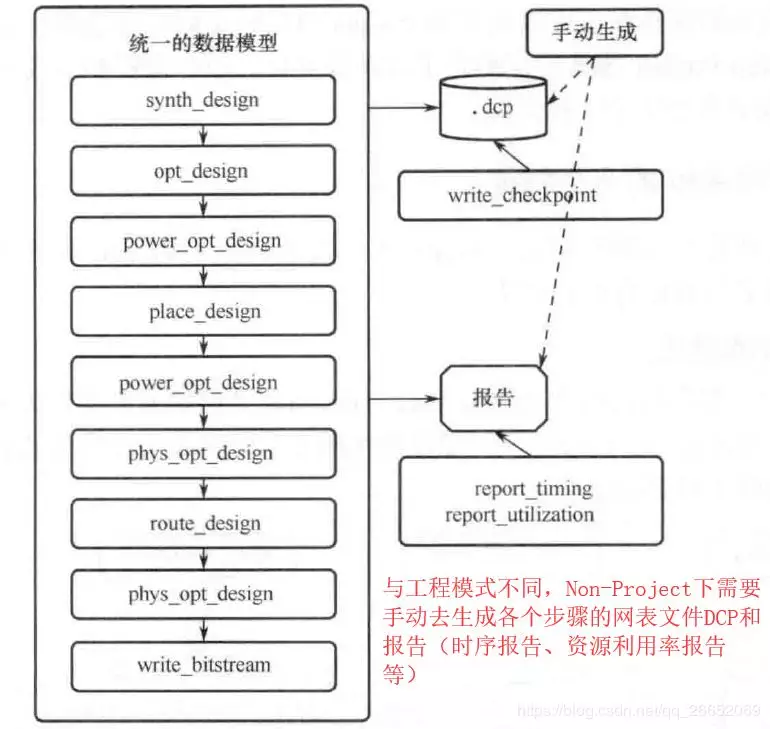

vivado工程編譯完成后,在工程目錄下vivado在實現(implement)過程中會將中間的過程封裝成dcp文件,在/runs/impl_1下,有_opt.dcp、_placed.dcp、_routed.dcp幾個dcp文件。

其中_opt.dcp是在opt_design完成之后生成,opt_design主要是完成邏輯優化等。_placed.dcp在placed_design完成之后生成,placed_design主要是完成布局工作。_routed.dcp在routed_design完成之后生成,routed_desig主要是完成布線工作。

可以根據修改的邏輯大小、類型選擇DCP節點進行修改。生成bit流時,是從該節點到generate_bitstream,從而節省編譯時間。

這里我參考了一篇csdn上的文章(文末附上鏈接),我引用一個文中提到的也是我用過的方法,剩下的場景大家可參考這篇文章。

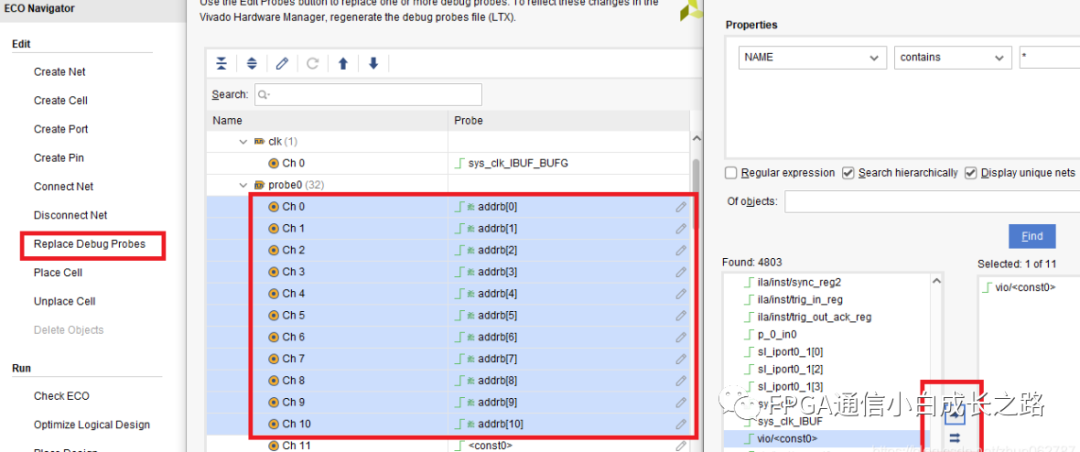

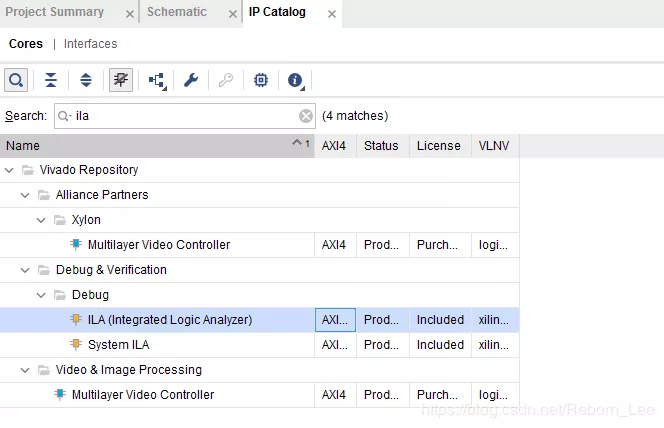

使用eco模式下的Replace Debug Probes(已經有ILA核,只是漏抓了信號)

a,打開_routed.dcp

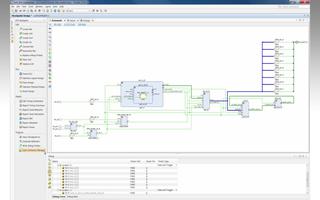

b,選擇Replace Debug probes

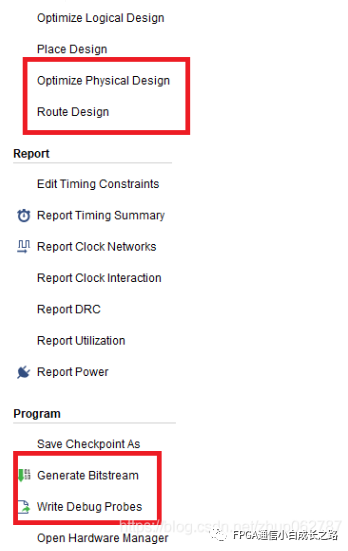

c,因為只是修改了布線,布局沒有改動,所以需要Route Design。Optimize Physical Design是優化布局、時序等。大工程不優化有可能布不成功。布局完成,直接Generate Bitstream、write Debug probes

d,對于編譯1.5個小時的工程。替換ILA引腳生成bit文件需要10分鐘左右。

-

程序

+關注

關注

117文章

3793瀏覽量

81220 -

編譯

+關注

關注

0文章

660瀏覽量

32929 -

Vivado

+關注

關注

19文章

815瀏覽量

66709

原文標題:vivado中使用eco方式進行快速debug

文章出處:【微信號:FPGA通信小白成長之路,微信公眾號:FPGA通信小白成長之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Vivado工程模式和非工程模式的比較

Vivado+FPGA:如何使用Debug Cores(ILA)在線調試

Vivado中使用debug工具步驟與調試技巧

Vivado使用誤區與進階——在Vivado中實現ECO功能

汽車eco模式使用技巧_eco模式真能省油嗎

eco模式的好處以及壞處_eco模式會引起積碳是真的嗎

關于Vivado中三種操作Debug的方式

一起體驗Vivado 的ECO流程

帶大家一起體驗一下Vivado的ECO流程

vivado使用eco模式下的Replace Debug Probes

vivado使用eco模式下的Replace Debug Probes

評論