絕緣體上硅(SOI)硅片由頂層硅膜、埋氧層和硅襯底三部分組成。隨著集成電路技術(shù)的發(fā)展,體硅襯底CMOS集成電路面臨著諸多挑戰(zhàn),如寄生閂鎖效應(yīng)(Latch-Up Effect)、短溝道效應(yīng)、泄漏電流增大、閾值電壓漂移、寄生電容增大等,SOI集成電路則可減少上述困擾。SOI集成電路可以實(shí)現(xiàn)集成電路中器件之間更有效的介質(zhì)隔離,并徹底消除體硅襯底CMOS電路中的寄生閂鎖效應(yīng),同時降低寄生電容和RC延遲,提高電路操作速度,減少光掩模版數(shù)量,減緩短溝道效應(yīng),降低功耗。

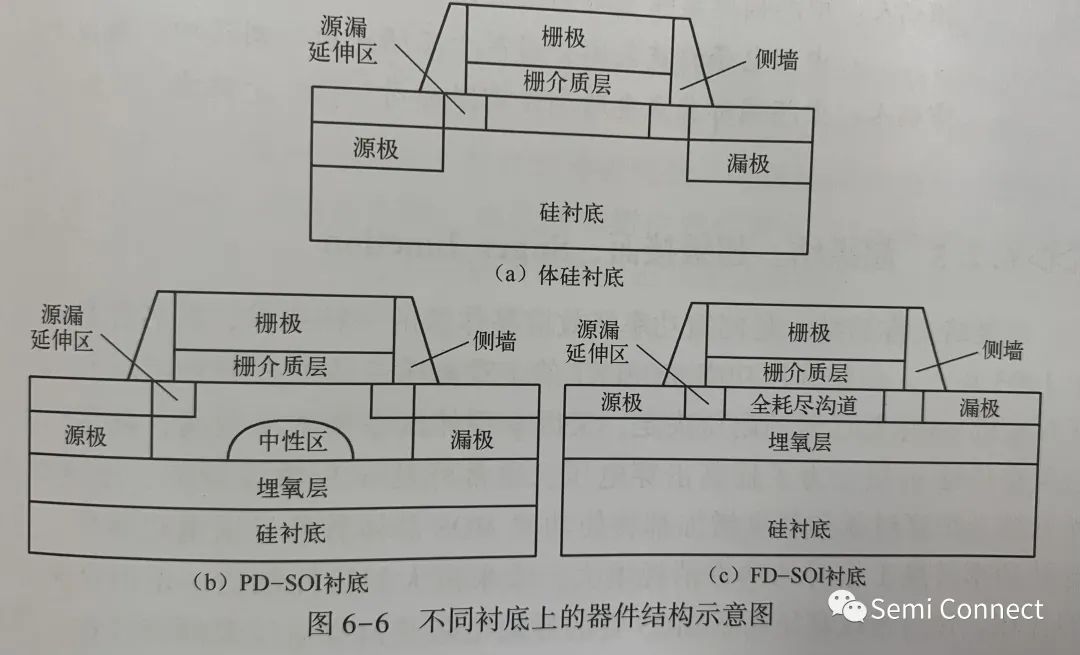

根據(jù)器件工作時溝道區(qū)域是否存在中性區(qū),將SOI器件分為部分耗盡型SOI(Partially Depleted SOI,PD- SOI)器件及全耗盡型SOI(Fully Depleted SOI, FD-SOI)器件兩種類型,如圖6-6所示。FD- SDI器件的頂層硅膜較薄,導(dǎo)通狀態(tài)下硅膜處于完全耗盡狀態(tài),消除了中性體區(qū)引起的翹曲效應(yīng)(Kink Effect)和寄生n-p-n管效應(yīng)。同時,超薄的頂層硅膜使柵極對溝道控制能力得到提高,亞閾值擺幅得到改善,因此FD-SOI器件具有良好的短溝道特性。

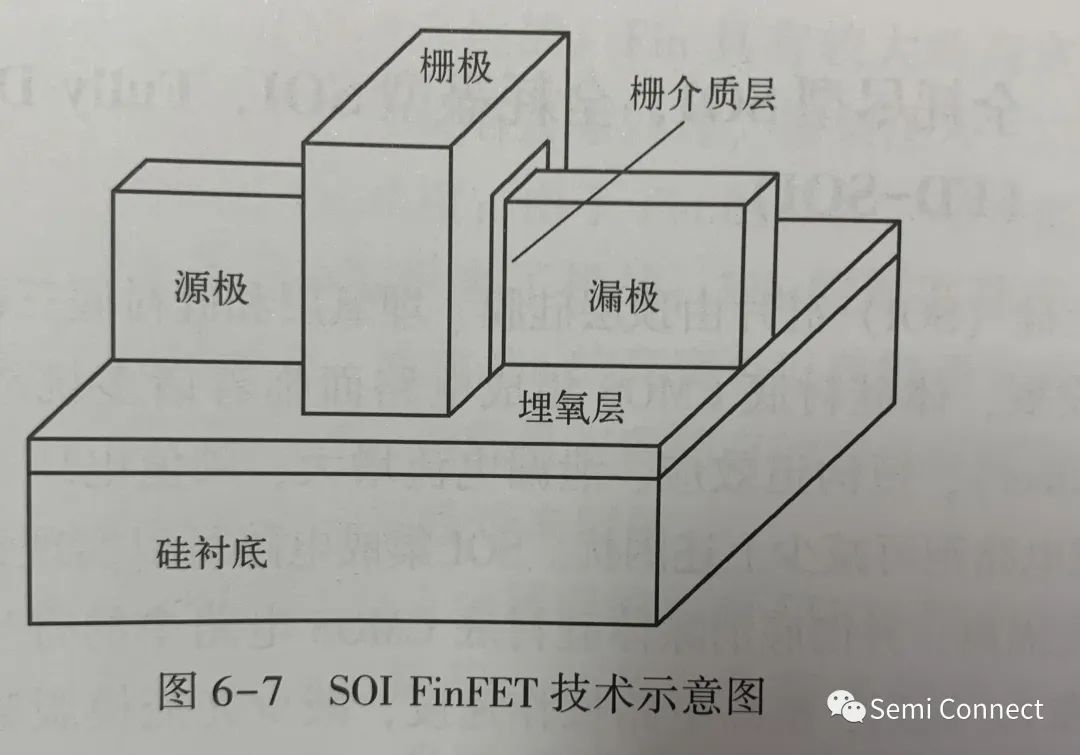

有分析認(rèn)為,從28nm/20nm節(jié)點(diǎn)開始,基于體硅CMOS和FinFET工藝的集成電路主流技術(shù)的單個晶體管的成本出現(xiàn)不降反升的局面。而作為FD-SOI技術(shù)的主要支持者(如IBM、意法半導(dǎo)體、格芯等)認(rèn)為,在先進(jìn)節(jié)點(diǎn)上,F(xiàn)D- SOI技術(shù)將更具備競爭優(yōu)勢。FD- SOI技術(shù)可延續(xù)平面CMOS器件的微縮進(jìn)程。此外,也有一些公司和科研機(jī)構(gòu)正在研究FD- SOI FinFET工藝,如圖6-7所示。

相對于體硅FinFET,F(xiàn)D-SOI因目前仍然采用平面架構(gòu),其工藝實(shí)現(xiàn)難度及制造成本相對較低。雖然在SOI襯底上制備集成電路的工藝相對簡單,但其原材料成本較高,限制了SOI工藝的廣泛應(yīng)用。除了介個因素,F(xiàn)D- SOI的產(chǎn)業(yè)生態(tài)環(huán)境也是制約其發(fā)展的重要因素,模擬仿真軟件、設(shè)計IP、設(shè)計工具尚不及普通體硅技術(shù)健全,因此FD- SOI目前主要應(yīng)用于低功耗、低漏電等領(lǐng)域。

-

集成電路

+關(guān)注

關(guān)注

5388文章

11547瀏覽量

361836 -

晶體管

+關(guān)注

關(guān)注

77文章

9693瀏覽量

138196 -

SOI

+關(guān)注

關(guān)注

4文章

70瀏覽量

17643

原文標(biāo)題:集成電路中的硅基器件—全耗盡型SOI(FD- SOI)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

SOI工藝的廣泛應(yīng)用

SOI工藝的廣泛應(yīng)用

評論