初學(xué)STM32H7一定要優(yōu)先整體把控芯片的框架,不要急于了解單個(gè)外設(shè)的功能。

1 初學(xué)者重要提示

學(xué)習(xí)一款新的芯片,優(yōu)先掌握系統(tǒng)框架是比較重要的,建議逐漸養(yǎng)成這種學(xué)習(xí)習(xí)慣,然后各個(gè)擊破即可。

本章節(jié)提供了多張STM32H7的框圖,這些框圖都非常具有代表性。很多時(shí)候記憶知識點(diǎn)比較費(fèi)腦子,記錄這些框圖是一種非常好的方式。

對于本章節(jié)提供的部分知識點(diǎn),無法理解透徹,暫時(shí)沒有關(guān)系。隨著后面的深入學(xué)習(xí),基本都可以掌握。

重要的MPU和Cache知識分別放在了第23章和第24章。

2 STM32H7硬件框圖

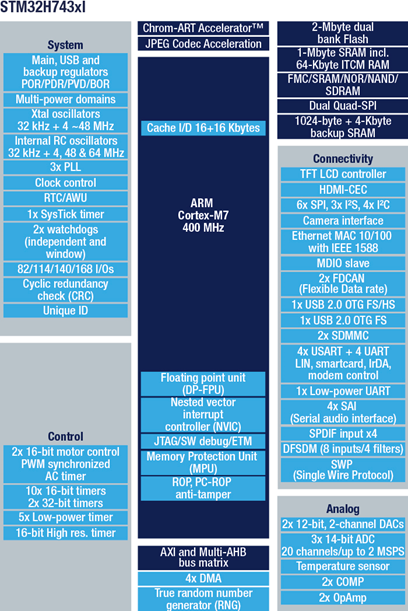

學(xué)習(xí)一款新的芯片,需要優(yōu)先了解一下它的整體功能設(shè)計(jì)。需要的資料主要是來自官網(wǎng)和數(shù)據(jù)手冊,比如我們V7開發(fā)板使用的STM32H743XIH6,直接在官方地址:鏈接(這是超鏈接)就可以看到對此芯片所做的介紹,頁面中有一個(gè)如下的框圖,對于了解STM32H7整體設(shè)計(jì)非常方便。

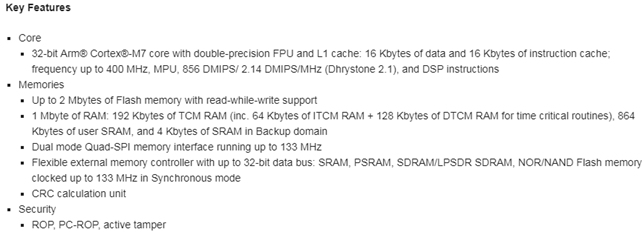

再稍微詳細(xì)點(diǎn),就需要大家讀頁面上的”Key Features”,就是下圖所示的內(nèi)容:

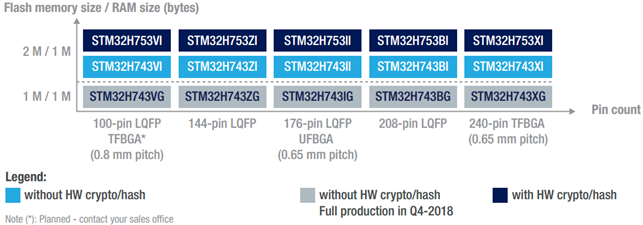

或者直接看數(shù)據(jù)手冊開頭的章節(jié)即可,也進(jìn)行了介紹,內(nèi)容基本都是差不多的,如下圖所示(部分截圖):

通過框圖和Key Features,大家可以方便地了解STM32H7的FLASH、RAM大小以及各種自帶外設(shè)的信息。

3 STM32H7各個(gè)型號的區(qū)別

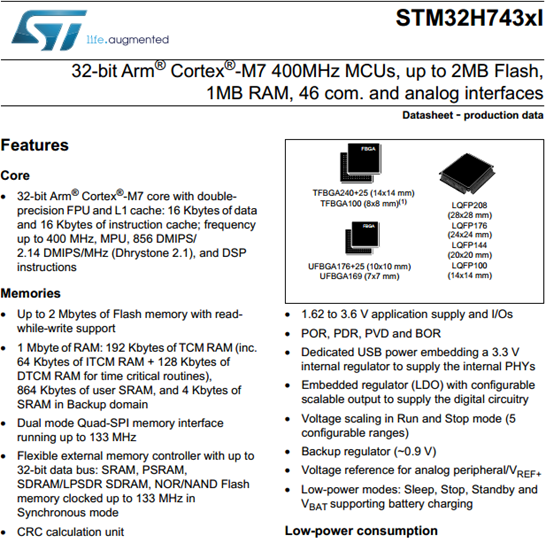

涉及到芯片選型的時(shí)候,需要大家了解各個(gè)型號的區(qū)別。對此ST有一個(gè)專門的文件STM32H7x3 MCUs High-performance line,在鏈接(這是一個(gè)超鏈接)里面可以找到。此文件里面有簡單的對比,只是內(nèi)容比較簡單,僅兩頁,不過也言簡意賅。最主要的是下面的這個(gè)截圖:

通過這個(gè)截圖可以方便地了解不同型號的引腳數(shù)、封裝、FLASH大小、RAM大小以及是否帶HW CRYPTO硬件加密的區(qū)別。

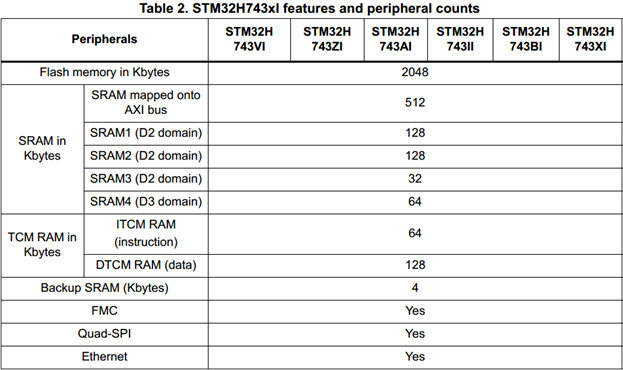

需要了解更詳細(xì)的對比信息,可以看數(shù)據(jù)手冊。任意下載一個(gè)型號的數(shù)據(jù)手冊,在數(shù)據(jù)手冊的的Table 2里面有詳細(xì)的對比,如下圖所示(部分截圖):

使用ST提供的軟件STMCUFinder或者STM32CubeMX也可以做對比,只是沒有上面的表格這么方便,可以一目了然。

4 STM32H7總線框圖和時(shí)鐘

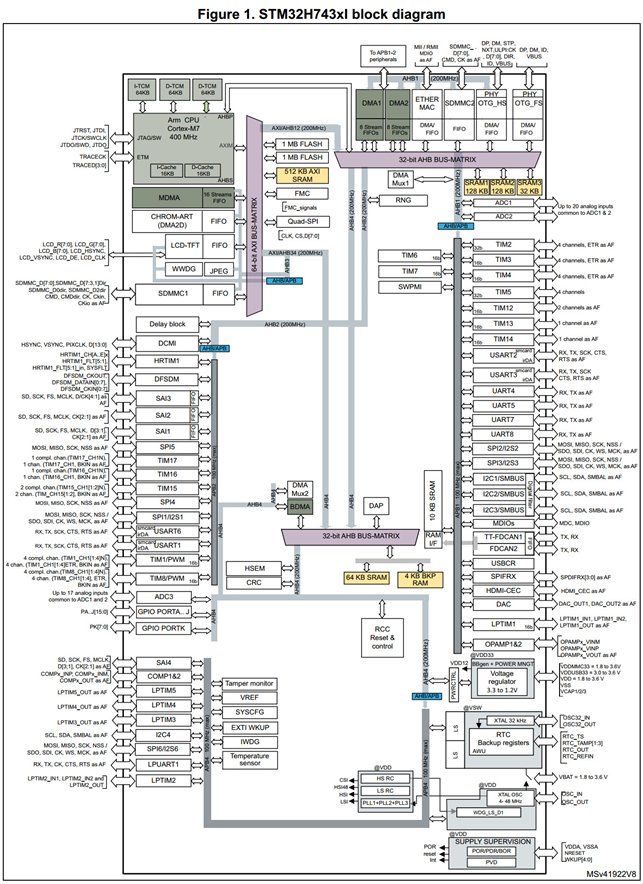

STM32H7的數(shù)據(jù)手冊里面提供了一張非常棒的框圖,大家可以方便地查看每個(gè)總線的時(shí)鐘速度和這個(gè)總線所掛的外設(shè)。這個(gè)在大家配置外設(shè)時(shí)鐘分頻的時(shí)候還是非常有用的,因?yàn)橥庠O(shè)的時(shí)鐘分頻就是建立在所掛的總線速度

比如我們想得到不同定時(shí)器的主頻,通過上面的框圖,可以方便地獲得如下信息:

SYSCLK(Hz) = 400000000 (CPU Clock)

HCLK(Hz) = 200000000 (AXI and AHBs Clock)

AHB Prescaler = 2

D1 APB3 Prescaler = 2 (APB3 Clock 100MHz)

D2 APB1 Prescaler = 2 (APB1 Clock 100MHz)

D2 APB2 Prescaler = 2 (APB2 Clock 100MHz)

D3 APB4 Prescaler = 2 (APB4 Clock 100MHz)

因?yàn)锳PB1 prescaler != 1, 所以 APB1上的TIMxCLK = APB1 x 2 = 200MHz;

因?yàn)锳PB2 prescaler != 1, 所以 APB2上的TIMxCLK = APB2 x 2 = 200MHz;

APB4上面的TIMxCLK沒有分頻,所以就是100MHz;

APB1 定時(shí)器有 TIM2, TIM3 ,TIM4, TIM5, TIM6, TIM7, TIM12, TIM13, TIM14,LPTIM1

APB2 定時(shí)器有 TIM1, TIM8 , TIM15, TIM16,TIM17

APB4 定時(shí)器有 LPTIM2,LPTIM3,LPTIM4,LPTIM5

5 STM32H7的AXI總線

AXI總線在STM32H7中有著舉足輕重的作用。高并發(fā)性全靠這個(gè)總線了,先來看下AXI總線的框架:

5.1 總線系統(tǒng)框架

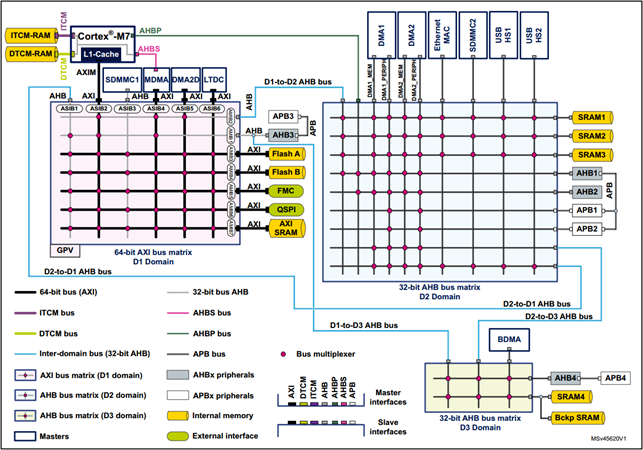

下面這個(gè)截圖比較有代表性,可以幫助大家理解STM32H7總線系統(tǒng)。

這個(gè)圖可以方便識別總線所外掛的外設(shè),共分為三個(gè)域:D1 Domain,D2 Domain和D3 Domain。

D1 Domain

D1域中的各個(gè)外設(shè)是掛在64位AXI總線組成6*7的矩陣上。

6個(gè)從接口端ASIB1到ASIB6

外接的主控是LTDC,DMA2D,MDMA,SDMMC1,AXIM和D2-to-D1 AHB 總線。

7個(gè)主接口端AMIB1到AMIB7

外接的從設(shè)備是AHB3總線,F(xiàn)lash A,F(xiàn)lash B,F(xiàn)MC總線,QSPI和AXI SRAM。另外AHB3也是由AXI總線分支出來的,然后再由AHB3分支出APB3總線。

D2 Domain

D2域的各個(gè)外設(shè)是掛在32位AHB總線組成10*9的矩陣上。

10個(gè)從接口

外接的主控是D1-to-D2 AHB 總線,AHBP總線,DMA1,DMA2,Ethernet MAC,SDMMC2,USB HS1和USB HS2。

9個(gè)主接口

外接的從設(shè)備是SRAM1,SRMA2,SRAM3,AHB1,AHB2,APB2,APB3,D2-to-D1 AHB總線和D2-to-D3 AHB總線。

D3 Domain

D3域的各個(gè)外設(shè)是掛在32位AHB總線組成3*2的矩陣上。

3個(gè)從接口

外接的主控D1-to-D3 AHB總線,D2-to-D3 AHB總線和BDMA。

2個(gè)主接口

外接的從設(shè)備是AHB4,SRAM4和Bckp SRAM。另外AHB4也是這個(gè)總線矩陣分支出來的,然后再由AHB4分支出APB4總線。

這三個(gè)域之間也是有互聯(lián)的,可以是:

D1域到D2域的D1-to-D2 AHB bus

允許D1域中的主接口外設(shè)訪問D2域里面的從接口外設(shè)。比如D1域里面的DMA2D訪問D2域里面的SRAM1。

D2域到D1域的D2-to-D1 AHB bus

允許D2域中的主接口外設(shè)訪問D1域里面的從接口外設(shè)。比如D2域里面的DMA2訪問D1域里面的AXI SRAM。

D1域到D3域的D1-to-D3 AHB bus

允許D1域中的主接口外設(shè)訪問D3域里面的從接口外設(shè)。比如D1域里面的DMA2D訪問D3域里面的SRAM4。

D2域到D3域的D2-to-D3 AHB bus。

允許D1域中的主接口外設(shè)訪問D2域里面的從接口外設(shè)。比如D2域里面的DMA2訪問D3域里面的SRAM4。

有了這些知識后,下面我們重點(diǎn)了解AXI總線矩陣。

5.2 AXI總線特色

AXI支持高頻率、高性能的系統(tǒng)設(shè)計(jì):

支持高帶寬,低延遲設(shè)計(jì)。

提供高頻操作,無需復(fù)雜的總線橋。

滿足各種組件的接口需求。

適用于具有高初始訪問延遲的內(nèi)存控制器。

為互連架構(gòu)的實(shí)現(xiàn)提供了靈活性。

與現(xiàn)有的AHB和APB接口向后兼容。

AXI總線的關(guān)鍵特性:

獨(dú)立的地址、控制和數(shù)據(jù)線。

支持非字節(jié)對齊方式傳輸。

基于起始地址的突發(fā)傳輸。

分開的讀和寫數(shù)據(jù)通道,且提供DMA傳輸。

支持發(fā)起多個(gè)地址。

支持無序傳輸。

允許添加寄存器,以提供時(shí)序收斂。

5.3 AXI總線簡介

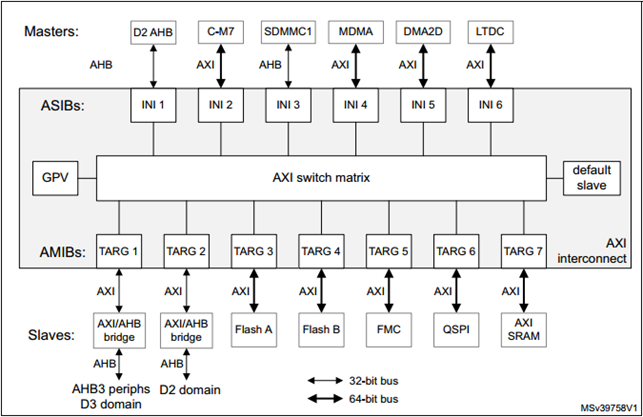

通過下面的框圖,我們再進(jìn)一步的認(rèn)識一下AXI總線。

通過上面的截圖,我們可以看到,AXI總線有6個(gè)從接口ASIBs(AMBA slave interface blocks)和7個(gè)主控接口AMIBs(AMBA master interface blocks)。

針對從接口ASIBs,描述如下:

重點(diǎn)注意最后一列,STM32H7參考手冊里面原始的描述是R/W issuing,這里將其翻譯為讀/寫發(fā)起能力。比如輸入通道IN5連接的主控DMA2D,支持的讀發(fā)起能力是2,寫發(fā)起能力是1。讀發(fā)起能力是2該如何理解呢?這里的含義是存在兩路讀信號同時(shí)進(jìn)行(因?yàn)锳XI接口有一個(gè)FIFO的功能,可供同時(shí)進(jìn)行,更深入的認(rèn)識有待研究),反映到DMA2D的實(shí)際應(yīng)用中,就是DMA2D同時(shí)讀取前景色和背景色的緩存區(qū)做Alpha融合之類的操作。寫操作同理,DMA2D的寫發(fā)起能力僅支持一路。

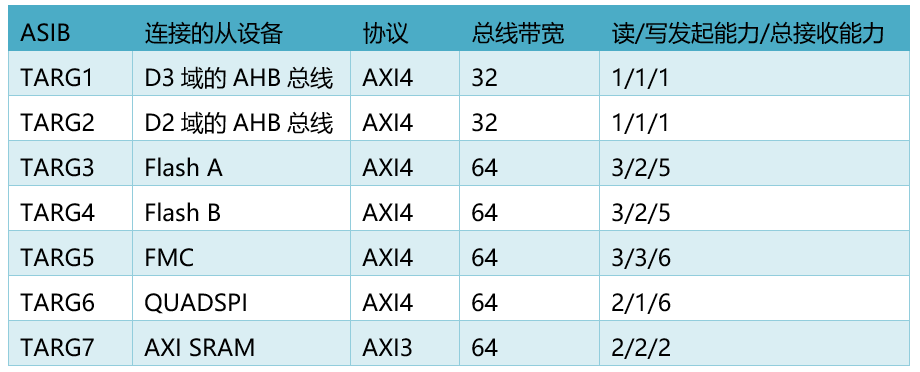

針對主控接口AMIBs,描述如下:

跟上面表格的含義是一樣的,同樣重點(diǎn)注意最后一列,這里多了一個(gè)總接收能力(Total acceptance),也就是讀發(fā)起能力和寫發(fā)起能力同時(shí)執(zhí)行的情況。

5.4 AXI總線優(yōu)先級編程

由于存在多個(gè)ASIB從接口訪問AMIB主控的問題,這就涉及到誰先誰后等問題。所以AXI總線矩陣就做了一個(gè)基于優(yōu)先級的仲裁方案。每個(gè)ASIB接口支持讀通道和寫通道分別設(shè)置,優(yōu)先級從0到15。數(shù)值越大,優(yōu)先級越高,默認(rèn)情況都是優(yōu)先級0。如果有兩個(gè)傳輸同時(shí)到達(dá)AMIB主控接口,那么優(yōu)先級高的ASIB接口傳輸優(yōu)先處理;如果優(yōu)先級相同的話,根據(jù)LUR方案選擇(least recently-used最近最少使用情況)。

大家在實(shí)際應(yīng)用中,可以根據(jù)實(shí)際情況進(jìn)行設(shè)置,一般情況下使用默認(rèn)值即可。

6 STM32H7的總線互聯(lián)

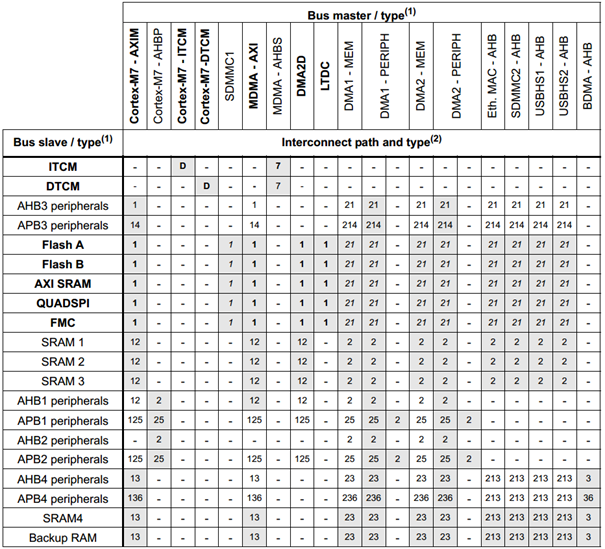

STM32H7的總線矩陣四通八達(dá),但不是任意Bus Master總線主控端和Bus Slave設(shè)備端都可以相互通信的:

黑色加粗字體是64位總線(ITCM,DTCM,F(xiàn)lash A,F(xiàn)lash,AXI SRAM,F(xiàn)MC等),普通字體是32位總線。

訪問通路(每個(gè)小方塊里面的字符)

任何有數(shù)字的表示有訪問通路。

短橫杠“-”表示不可訪問。

有灰色陰影的表示有實(shí)用價(jià)值的訪問通路。

表格中具體數(shù)值所代表的含義

D=direct

1=via AXI bus matrix

2=via AHB bus matrix in D2

3=via AHB bus matrix in D3

4=via AHB/APB bridge in D1

5=via AHB/APB bridge in D2

6=via AHB/APB bridge in D3

7=via AHBS bus of Cortex-M7

多個(gè)數(shù)值組合 = 互連路徑以數(shù)字的順序經(jīng)過多個(gè)矩陣或/和橋。

總線訪問類型

普通字體表示32位總線。

斜體表示32位總線主機(jī)端/ 64位總線從機(jī)端。

粗體表示64位總線。

當(dāng)前要對這個(gè)圖有個(gè)了解,后面章節(jié)講解各個(gè)外設(shè)的時(shí)候要用到,比如DTCM和ITCM不支持DMA1,DMA2和BDMA,僅支持MDMA。

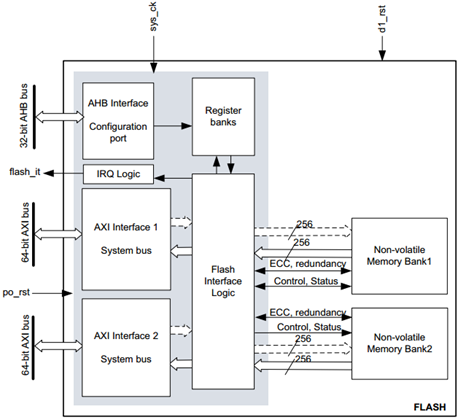

7 STM32H7的FLASH

首次學(xué)習(xí)STM32H7,要掌握以下幾點(diǎn)認(rèn)識即可:

1、雙BANK,每個(gè)BANK的帶寬都是64bits,如下圖所示:

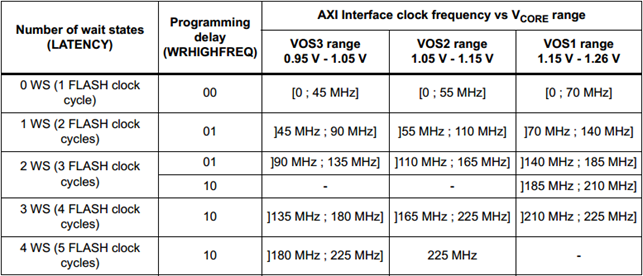

2、H7中Flash的延遲和主頻關(guān)系。

H7中已經(jīng)沒有F1和F4系列中的ART Chrome加速,通過H7中的Cache加速即可。具體延遲數(shù)值和主頻關(guān)系如下:

對于上面的表格,大家可以看到,當(dāng)延遲等待設(shè)置為0的時(shí)候,即無等待,單周期訪問,速度可以做到70MHz。增加1個(gè)Flash周期后,訪問速度可以做到140MHz。當(dāng)增加到3個(gè)或4個(gè)Flash周期后,最高速度可以做到225MHz。

3、Flash編程操作(寫)最好以256bits為單位進(jìn)行,應(yīng)用中也可以小于256bits,但是容易造成ECC校驗(yàn)出問題,所以不推薦。Flash讀操作支持64bits,32bits,16bits和8bits。

4、Flash支持ECC校驗(yàn),每256bits配10bit的ECC位,可以檢測到1個(gè)bit并糾正或者檢測2個(gè)bit。隨著芯片的制造工藝水平越高,帶電粒子能產(chǎn)生的位翻轉(zhuǎn)就越多,此時(shí)的ECC是必須要有的,一般可以糾正1-2個(gè)bit。安全等級高的Flash類存儲(chǔ)器和RAM類都是必須要帶ECC的。

8 STM32H7的RAM

STM32H7的RAM區(qū)分為好幾個(gè)部分,下面分別進(jìn)行說明:

TCM區(qū)

TCM : Tightly-Coupled Memory 緊密耦合內(nèi)存 。ITCM用于運(yùn)行指令,也就是程序代碼,DTCM用于數(shù)據(jù)存取,特點(diǎn)是跟內(nèi)核速度一樣,而片上RAM的速度基本都達(dá)不到這個(gè)速度,所以有降頻處理。

速度:400MHz。

DTCM地址:0x2000 0000,大小128KB。

ITCM地址:0x0000 0000,大小64KB。

AXI SRAM區(qū)

位于D1域,數(shù)據(jù)帶寬是64bit,掛在AXI總線上。除了D3域中的BDMB主控不能訪問,其它都可以訪問此RAM區(qū)。

速度:200MHz。

地址:0x2400 0000,大小512KB。

用途:用途不限,可以用于用戶應(yīng)用數(shù)據(jù)存儲(chǔ)或者LCD顯存。

SRAM1,SRAM2和SRAM3區(qū)

位于D2域,數(shù)據(jù)帶寬是32bit,掛在AHB總線上。除了D3域中的BDMB主控不能訪問這三塊SRAM,其它都可以訪問這幾個(gè)RAM區(qū)。

速度:200MHz。

SRAM1:地址0x3000 0000,大小128KB,用途不限,可用于D2域中的DMA緩沖,也可以當(dāng)D1域斷電后用于運(yùn)行程序代碼。

SRAM2:地址0x3002 0000,大小128KB,用途不限,可用于D2域中的DMA緩沖,也可以用于用戶數(shù)據(jù)存取。

SRAM3:地址0x3004 0000,大小32KB,用途不限,主要用于以太網(wǎng)和USB的緩沖。

SRAM4區(qū)

位于D3域,數(shù)據(jù)帶寬是32bit,掛在AHB總線上,大部分主控都能訪這塊SRAM區(qū)。

速度:200MHz。

地址:0x3800 0000,大小64KB。

用途:用途不限,可以用于D3域中的DMA緩沖,也可以當(dāng)D1和D2域進(jìn)入DStandby待機(jī)方式后,繼續(xù)保存用戶數(shù)據(jù)。

Backup SRAM區(qū)

備份RAM區(qū),位于D3域,數(shù)據(jù)帶寬是32bit,掛在AHB總線上,大部分主控都能訪問這塊SRAM區(qū)。

速度:200MHz。

地址:0x3880 0000,大小4KB。

用途:用途不限,主要用于系統(tǒng)進(jìn)入低功耗模式后,繼續(xù)保存數(shù)據(jù)(Vbat引腳外接電池)。

9 總結(jié)

本章節(jié)就為大家講解這么多,讓大家對STM32H7有個(gè)整體的認(rèn)識,后面章節(jié)將逐個(gè)進(jìn)行學(xué)習(xí)。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

455文章

50812瀏覽量

423583 -

FlaSh

+關(guān)注

關(guān)注

10文章

1635瀏覽量

148017 -

stm32h7

+關(guān)注

關(guān)注

0文章

37瀏覽量

1753

原文標(biāo)題:如何高效入手STM32H7?整體把控一下框架

文章出處:【微信號:技術(shù)讓夢想更偉大,微信公眾號:技術(shù)讓夢想更偉大】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

【STM32H7教程】第19章 STM32H7的GPIO應(yīng)用之按鍵FIFO

STM32H7學(xué)習(xí)之路繼續(xù)(stm32H7系列3) GPIO

【STM32H7教程】第21章 STM32H7的NVIC中斷分組和配置(重要)

"STM32H7學(xué)習(xí)繼續(xù)(STM32H7系列5)第十七章比較實(shí)用,以后寫程序的時(shí)候會(huì)用到"

【STM32H7教程】第8章 STM32H7的終極調(diào)試組件Event Recorder

【STM32H7教程】第14章 STM32H7的電源,復(fù)位和時(shí)鐘系統(tǒng)

一文深入了解STM32H7芯片

一文深入了解STM32H7芯片

評論