電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))數(shù)據(jù)中心作為CPU、GPU和加速器廠商最為關(guān)注的市場(chǎng),自然也少不了RISC-V這個(gè)新架構(gòu)來(lái)?yè)胶鸵荒_。我們?cè)谥暗奈恼轮幸矊?duì)RISC-V在數(shù)據(jù)中心的進(jìn)展做了一些介紹,RISC-V雖然在服務(wù)器通用CPU上發(fā)力跡象不明顯,但要說(shuō)AI加速器這類產(chǎn)品,很有可能會(huì)是RISC-V打入數(shù)據(jù)中心市場(chǎng)的最佳方向。

谷歌的RISC-V戰(zhàn)略

自己設(shè)計(jì)芯片的服務(wù)器廠商之一,谷歌,似乎也開始打算用上RISC-V。在今年9月美國(guó)的AI硬件峰會(huì)上,SiFive首席架構(gòu)師和谷歌的TPU芯片架構(gòu)師展示了他們的合作方案。谷歌的TPU是谷歌設(shè)計(jì)專用于機(jī)器學(xué)習(xí)的加速器,用于在數(shù)據(jù)中心上運(yùn)行TensorFlow、Pytorch和JAX等機(jī)器學(xué)習(xí)框架。

而TPU的主要計(jì)算單元就是矩陣乘法打算(MXU),由脈動(dòng)陣列中的128x128乘法/累積器組成,在最小配置v4版TPU中包含4個(gè)TPU芯片,每個(gè)TPU芯片都有8個(gè)MXU,是TPU v3版的兩倍,而且每個(gè)MXU都能使用BF16執(zhí)行每周期16K的乘積累加運(yùn)算。

然而,谷歌發(fā)現(xiàn)雖然TPU的機(jī)器學(xué)習(xí)算力雖然夠用,但客戶在利用這類大型AI加速器時(shí),往往無(wú)法用它來(lái)完成其他的復(fù)雜計(jì)算負(fù)載,所以谷歌的做法是將SiFive的X280處理器核心,作為TPU的協(xié)處理器,用來(lái)提供維護(hù)和運(yùn)行代碼,跑加速器沒法運(yùn)行的內(nèi)核。

雖然SiFive的X280主打的是加速AI/ML計(jì)算,但主要是針對(duì)邊緣端,比如AR/VR、數(shù)碼相機(jī)等等,并非用于數(shù)據(jù)中心的大型AI加速器。但在與谷歌等廠商的合作下,SiFive推出了一個(gè)名為矢量定制協(xié)處理器接口(VCIX)的技術(shù),可以讓大型AI加速器直接與X280的32x512位矢量寄存器文件高速通信。

這相比其他方案來(lái)說(shuō),矢量寄存器層級(jí)上的訪問不僅可以提供更大的帶寬、比PCIe更低延遲,還能簡(jiǎn)化軟件棧、省下更多的硬件資源。X280和TPU核心分工合作,前者負(fù)責(zé)運(yùn)行完整的Linux系統(tǒng)和虛擬機(jī)管理程序,后者負(fù)責(zé)密集的機(jī)器學(xué)習(xí)運(yùn)算。

英特爾HorseCreek初見端倪

早在去年,英特爾就宣布將會(huì)用到SiFive的P550高性能RISC-V核心,以及自己的7nm工藝(即現(xiàn)在的Intel4工藝)來(lái)打造一款RISC-V SoC,代號(hào)名為HorseCreek。雖然到了2022年,SiFive最高性能的核心已經(jīng)成了P650。但作為一個(gè)十三級(jí)流水線、三發(fā)射、亂序的64位RISC-V核心,P550的性能仍然是相當(dāng)能打的,SiFive給到的定位也是對(duì)標(biāo)ARM的Cortex-A75,同時(shí)只需不到一半的面積。

不過消息公布后,英特爾雖然又開展了一系列與RISC-V相關(guān)的行動(dòng),比如加入RISC-V國(guó)際基金會(huì)、IFS支持RISC-V芯片代工和推出RISC-V的FPGA開發(fā)平臺(tái)等等,但HorseCreek卻始終不見蹤影。

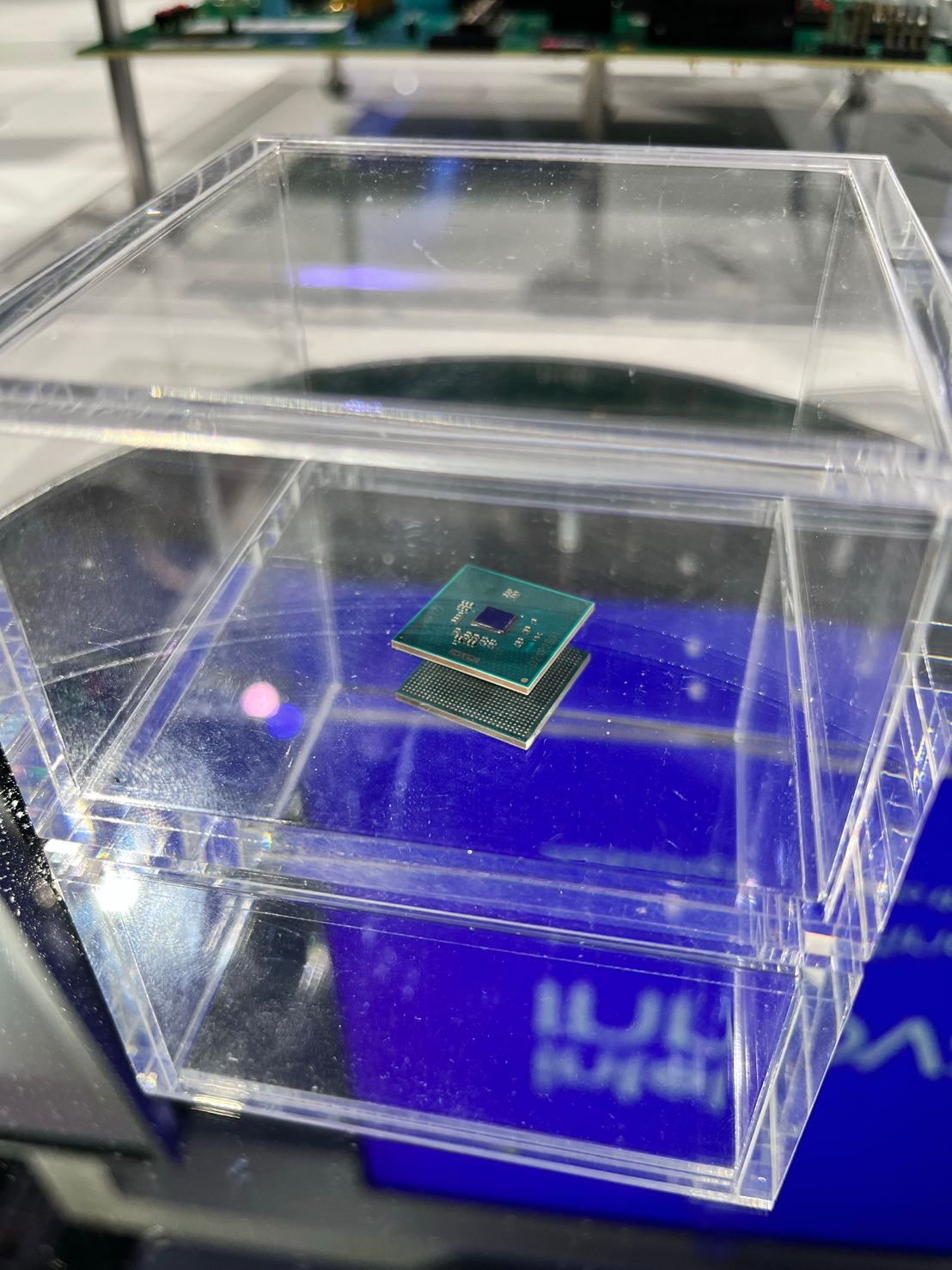

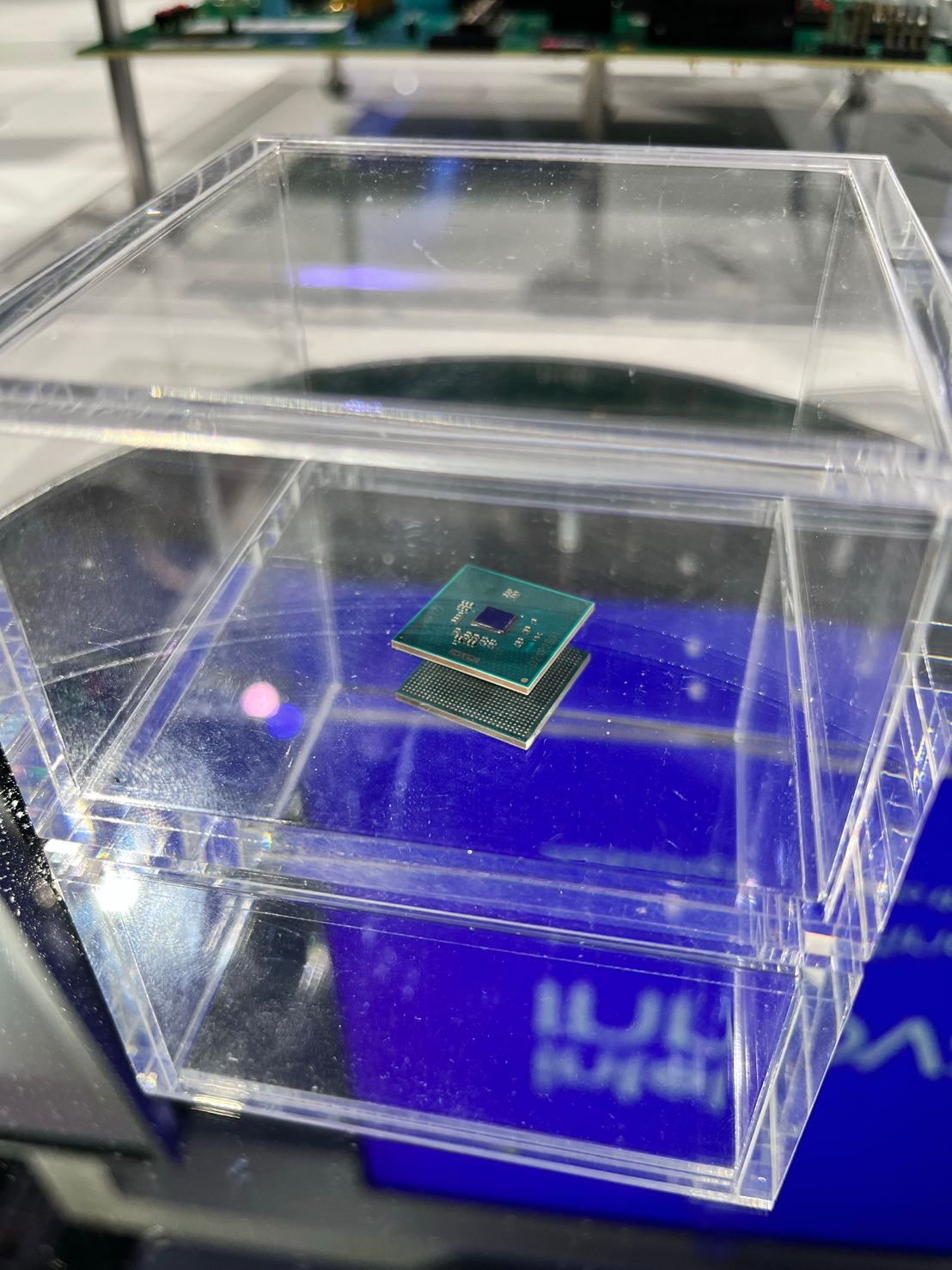

而在今年的IntelInnovation大會(huì)上,英特爾的不少合作伙伴都在現(xiàn)場(chǎng)搭建了展臺(tái),也有參會(huì)者終于在現(xiàn)場(chǎng)看到了HorseCreek的真面目。在Intel4工藝的加持下,HorseCreek將4個(gè)2.2GHz的SiFiveP550核心、DDR5和PCIe5集成到了4mmx4mm的單個(gè)裸片上,連英特爾CEO PatGelsinger本人也親自來(lái)展臺(tái)查看HorseCreek的開發(fā)平臺(tái)。

而在今年的IntelInnovation大會(huì)上,英特爾的不少合作伙伴都在現(xiàn)場(chǎng)搭建了展臺(tái),也有參會(huì)者終于在現(xiàn)場(chǎng)看到了HorseCreek的真面目。在Intel4工藝的加持下,HorseCreek將4個(gè)2.2GHz的SiFiveP550核心、DDR5和PCIe5集成到了4mmx4mm的單個(gè)裸片上,連英特爾CEO PatGelsinger本人也親自來(lái)展臺(tái)查看HorseCreek的開發(fā)平臺(tái)。

根據(jù)展臺(tái)上公開的數(shù)據(jù),HorseCreek配備了三級(jí)緩存,包括私有二級(jí)緩存和通用三級(jí)緩存。DDR5這塊集成了英特爾的DDR PHY、DFI接口與Cadence的DDR內(nèi)存控制器,支持到5600頻率的DDR5內(nèi)存,PCIe5.0部分集成了英特爾的PCIePhy和新思的PCIeRootHub控制器。除了英特爾提供的PLL、內(nèi)存編譯器、標(biāo)準(zhǔn)單元等數(shù)模IP以外,HorseCreek還用到了其他的IP,比如西門子的DFT和新思的NOC Fabric。

從以上數(shù)據(jù)可以看出,HorseCreek是一個(gè)集SiFive、英特爾和EDA廠商IP大成的SoC。如此強(qiáng)大的SoC加上豐富的接口支持,完全可以用于數(shù)據(jù)中心里。不過,HorseCreek的首個(gè)終端產(chǎn)品形態(tài)應(yīng)該是SiFive的下一代HiFive開發(fā)板。上一代的HiFive Unmatched開發(fā)板已經(jīng)售罄了,在疫情相關(guān)的供應(yīng)鏈問題下,SiFive已經(jīng)放棄了補(bǔ)貨的打算,轉(zhuǎn)而全力去打造下一代基于HorseCreek的HiFive開發(fā)板。

從以上數(shù)據(jù)可以看出,HorseCreek是一個(gè)集SiFive、英特爾和EDA廠商IP大成的SoC。如此強(qiáng)大的SoC加上豐富的接口支持,完全可以用于數(shù)據(jù)中心里。不過,HorseCreek的首個(gè)終端產(chǎn)品形態(tài)應(yīng)該是SiFive的下一代HiFive開發(fā)板。上一代的HiFive Unmatched開發(fā)板已經(jīng)售罄了,在疫情相關(guān)的供應(yīng)鏈問題下,SiFive已經(jīng)放棄了補(bǔ)貨的打算,轉(zhuǎn)而全力去打造下一代基于HorseCreek的HiFive開發(fā)板。

又一個(gè)千核RISC-V芯片

在戴爾的HPC社區(qū)大會(huì)上,來(lái)自美國(guó)的初創(chuàng)半導(dǎo)體公司InspireSemiconductor公布了他們?yōu)閿?shù)據(jù)中心提供的RISC-V加速器方案,同時(shí)還給出了另一個(gè)有趣的說(shuō)法,那就是現(xiàn)有的高性能計(jì)算方案已經(jīng)“不夠好”了。

在他們看來(lái),目前的主流數(shù)據(jù)中心CPU都太慢了,無(wú)論有無(wú)加速器的輔助都是如此,而在有了加速器以后,90%的高性能計(jì)算都是由加速器負(fù)責(zé)了。再者就是GPU和FPGA的方案,InspireSemiconductor指出這兩者的編程太復(fù)雜了,不僅鎖定了軟件棧,而且需要特定的技能才能獲得足夠好的計(jì)算結(jié)果。而ASIC和AI加速器的風(fēng)險(xiǎn)又太高了,從成本、時(shí)間上看都是如此。

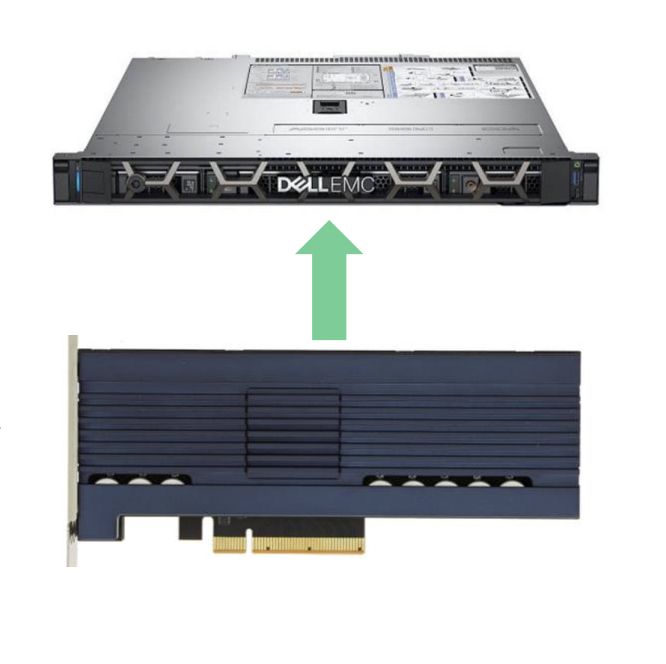

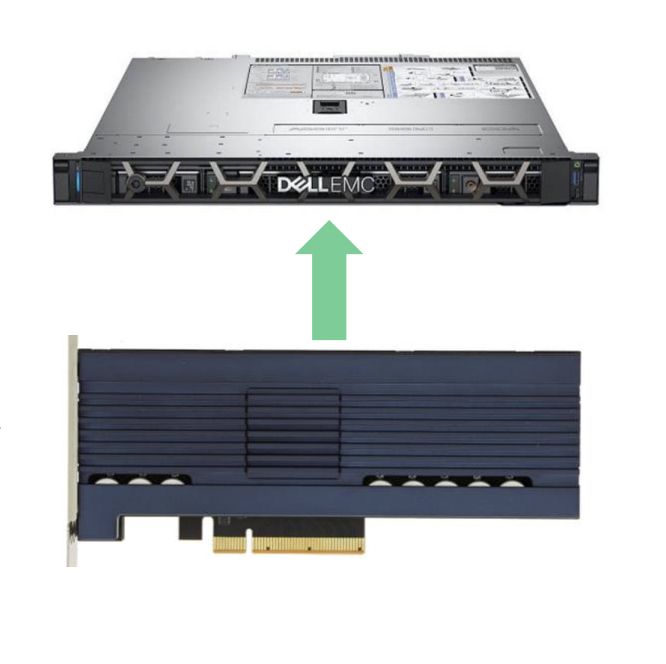

為此,InspireSemiconductor推出了他們的RISC-V加速器方案,Thunderbird。Thunderbird在單芯片上集成了2560個(gè)64位的CPU核心,單個(gè)PCIe加速卡上的核心數(shù)量更是超過5000個(gè)。InspireSemiconductor稱他們用到了創(chuàng)新的高速互聯(lián)方案,在高效利用這么多核心的同時(shí),最高可以組成256個(gè)芯片的陣列。

相較其他加速器和GPU方案,Thunderbird加速器也有著功耗上的優(yōu)勢(shì),單芯片的功耗在175W左右,同時(shí)他們給出了20W/Tflops的能效比,看來(lái)Thunderbird的峰值算力大概就在8.75Tflops左右了。雖然會(huì)上InspireSemiconductor也展示了谷歌、聯(lián)想和IBM等客戶或合作伙伴的一些反饋,但這些不少是客套話,是否已經(jīng)用于這些公司的數(shù)據(jù)中心方案中還不好說(shuō)。

相較其他加速器和GPU方案,Thunderbird加速器也有著功耗上的優(yōu)勢(shì),單芯片的功耗在175W左右,同時(shí)他們給出了20W/Tflops的能效比,看來(lái)Thunderbird的峰值算力大概就在8.75Tflops左右了。雖然會(huì)上InspireSemiconductor也展示了谷歌、聯(lián)想和IBM等客戶或合作伙伴的一些反饋,但這些不少是客套話,是否已經(jīng)用于這些公司的數(shù)據(jù)中心方案中還不好說(shuō)。

InspireSemiconductor同時(shí)承諾了一個(gè)對(duì)開發(fā)者友好的軟件生態(tài)系統(tǒng),但他們并沒有給出自己的軟件方案,而是指出Thunderbird將充分利用RISC-V已有的豐富軟件生態(tài)系統(tǒng),比如OneAPI等,所以不必像競(jìng)品芯片那樣去開發(fā)一次性的軟件棧。如此一來(lái)更適合那些喜歡標(biāo)準(zhǔn)CPU編程模型的開發(fā)者,無(wú)需像GPU那樣去學(xué)習(xí)CUDA、OpenCL,而是可以用Pragma和MPI這樣的標(biāo)準(zhǔn)編譯器方案。

AI編程上也是如此,InspireSemiconductor指出流行的AI框架,諸如TensorFlow、Pytorch和Glow等都已有了對(duì)RISC-V的支持,Linux也在操作系統(tǒng)支持的行列中。如此看來(lái),InspireSemiconductor目前應(yīng)該只提供了純硬件方案,而這樣的產(chǎn)品是否能在市面上取得成功,目前看來(lái)完全取決于英特爾Codeplay那邊的OneAPI軟件生態(tài)了。

谷歌的RISC-V戰(zhàn)略

自己設(shè)計(jì)芯片的服務(wù)器廠商之一,谷歌,似乎也開始打算用上RISC-V。在今年9月美國(guó)的AI硬件峰會(huì)上,SiFive首席架構(gòu)師和谷歌的TPU芯片架構(gòu)師展示了他們的合作方案。谷歌的TPU是谷歌設(shè)計(jì)專用于機(jī)器學(xué)習(xí)的加速器,用于在數(shù)據(jù)中心上運(yùn)行TensorFlow、Pytorch和JAX等機(jī)器學(xué)習(xí)框架。

而TPU的主要計(jì)算單元就是矩陣乘法打算(MXU),由脈動(dòng)陣列中的128x128乘法/累積器組成,在最小配置v4版TPU中包含4個(gè)TPU芯片,每個(gè)TPU芯片都有8個(gè)MXU,是TPU v3版的兩倍,而且每個(gè)MXU都能使用BF16執(zhí)行每周期16K的乘積累加運(yùn)算。

然而,谷歌發(fā)現(xiàn)雖然TPU的機(jī)器學(xué)習(xí)算力雖然夠用,但客戶在利用這類大型AI加速器時(shí),往往無(wú)法用它來(lái)完成其他的復(fù)雜計(jì)算負(fù)載,所以谷歌的做法是將SiFive的X280處理器核心,作為TPU的協(xié)處理器,用來(lái)提供維護(hù)和運(yùn)行代碼,跑加速器沒法運(yùn)行的內(nèi)核。

雖然SiFive的X280主打的是加速AI/ML計(jì)算,但主要是針對(duì)邊緣端,比如AR/VR、數(shù)碼相機(jī)等等,并非用于數(shù)據(jù)中心的大型AI加速器。但在與谷歌等廠商的合作下,SiFive推出了一個(gè)名為矢量定制協(xié)處理器接口(VCIX)的技術(shù),可以讓大型AI加速器直接與X280的32x512位矢量寄存器文件高速通信。

這相比其他方案來(lái)說(shuō),矢量寄存器層級(jí)上的訪問不僅可以提供更大的帶寬、比PCIe更低延遲,還能簡(jiǎn)化軟件棧、省下更多的硬件資源。X280和TPU核心分工合作,前者負(fù)責(zé)運(yùn)行完整的Linux系統(tǒng)和虛擬機(jī)管理程序,后者負(fù)責(zé)密集的機(jī)器學(xué)習(xí)運(yùn)算。

英特爾HorseCreek初見端倪

早在去年,英特爾就宣布將會(huì)用到SiFive的P550高性能RISC-V核心,以及自己的7nm工藝(即現(xiàn)在的Intel4工藝)來(lái)打造一款RISC-V SoC,代號(hào)名為HorseCreek。雖然到了2022年,SiFive最高性能的核心已經(jīng)成了P650。但作為一個(gè)十三級(jí)流水線、三發(fā)射、亂序的64位RISC-V核心,P550的性能仍然是相當(dāng)能打的,SiFive給到的定位也是對(duì)標(biāo)ARM的Cortex-A75,同時(shí)只需不到一半的面積。

不過消息公布后,英特爾雖然又開展了一系列與RISC-V相關(guān)的行動(dòng),比如加入RISC-V國(guó)際基金會(huì)、IFS支持RISC-V芯片代工和推出RISC-V的FPGA開發(fā)平臺(tái)等等,但HorseCreek卻始終不見蹤影。

根據(jù)展臺(tái)上公開的數(shù)據(jù),HorseCreek配備了三級(jí)緩存,包括私有二級(jí)緩存和通用三級(jí)緩存。DDR5這塊集成了英特爾的DDR PHY、DFI接口與Cadence的DDR內(nèi)存控制器,支持到5600頻率的DDR5內(nèi)存,PCIe5.0部分集成了英特爾的PCIePhy和新思的PCIeRootHub控制器。除了英特爾提供的PLL、內(nèi)存編譯器、標(biāo)準(zhǔn)單元等數(shù)模IP以外,HorseCreek還用到了其他的IP,比如西門子的DFT和新思的NOC Fabric。

又一個(gè)千核RISC-V芯片

在戴爾的HPC社區(qū)大會(huì)上,來(lái)自美國(guó)的初創(chuàng)半導(dǎo)體公司InspireSemiconductor公布了他們?yōu)閿?shù)據(jù)中心提供的RISC-V加速器方案,同時(shí)還給出了另一個(gè)有趣的說(shuō)法,那就是現(xiàn)有的高性能計(jì)算方案已經(jīng)“不夠好”了。

在他們看來(lái),目前的主流數(shù)據(jù)中心CPU都太慢了,無(wú)論有無(wú)加速器的輔助都是如此,而在有了加速器以后,90%的高性能計(jì)算都是由加速器負(fù)責(zé)了。再者就是GPU和FPGA的方案,InspireSemiconductor指出這兩者的編程太復(fù)雜了,不僅鎖定了軟件棧,而且需要特定的技能才能獲得足夠好的計(jì)算結(jié)果。而ASIC和AI加速器的風(fēng)險(xiǎn)又太高了,從成本、時(shí)間上看都是如此。

為此,InspireSemiconductor推出了他們的RISC-V加速器方案,Thunderbird。Thunderbird在單芯片上集成了2560個(gè)64位的CPU核心,單個(gè)PCIe加速卡上的核心數(shù)量更是超過5000個(gè)。InspireSemiconductor稱他們用到了創(chuàng)新的高速互聯(lián)方案,在高效利用這么多核心的同時(shí),最高可以組成256個(gè)芯片的陣列。

InspireSemiconductor同時(shí)承諾了一個(gè)對(duì)開發(fā)者友好的軟件生態(tài)系統(tǒng),但他們并沒有給出自己的軟件方案,而是指出Thunderbird將充分利用RISC-V已有的豐富軟件生態(tài)系統(tǒng),比如OneAPI等,所以不必像競(jìng)品芯片那樣去開發(fā)一次性的軟件棧。如此一來(lái)更適合那些喜歡標(biāo)準(zhǔn)CPU編程模型的開發(fā)者,無(wú)需像GPU那樣去學(xué)習(xí)CUDA、OpenCL,而是可以用Pragma和MPI這樣的標(biāo)準(zhǔn)編譯器方案。

AI編程上也是如此,InspireSemiconductor指出流行的AI框架,諸如TensorFlow、Pytorch和Glow等都已有了對(duì)RISC-V的支持,Linux也在操作系統(tǒng)支持的行列中。如此看來(lái),InspireSemiconductor目前應(yīng)該只提供了純硬件方案,而這樣的產(chǎn)品是否能在市面上取得成功,目前看來(lái)完全取決于英特爾Codeplay那邊的OneAPI軟件生態(tài)了。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

英特爾

+關(guān)注

關(guān)注

61文章

9978瀏覽量

171913 -

谷歌

+關(guān)注

關(guān)注

27文章

6171瀏覽量

105505 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

4794瀏覽量

72193 -

RISC-V

+關(guān)注

關(guān)注

45文章

2292瀏覽量

46218

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

第17屆英特爾互聯(lián)網(wǎng)數(shù)據(jù)中心大會(huì)順利舉行

第17屆英特爾互聯(lián)網(wǎng)數(shù)據(jù)中心大會(huì)在成都順利舉行。業(yè)界領(lǐng)先的云服務(wù)商、互聯(lián)網(wǎng)廠商、行業(yè)客戶、OEM/ODM等生態(tài)合作伙伴齊聚一堂,就當(dāng)下云計(jì)算與AI技術(shù)的發(fā)展趨勢(shì),以及加速產(chǎn)業(yè)智能化轉(zhuǎn)型等話題展開

RISC-V發(fā)展及FPGA廠商為什么選擇RISC-V

Microsemi 于 2017 年開始在其 FPGA 中提供 RISC-V 軟核,Lattice 于 2020 年開始提供,英特爾 (Altera) 于 2021 年

AMD數(shù)據(jù)中心營(yíng)收首超英特爾

在這一領(lǐng)域的地位開始受到挑戰(zhàn),也預(yù)示著數(shù)據(jù)中心市場(chǎng)競(jìng)爭(zhēng)格局的轉(zhuǎn)變。 具體數(shù)據(jù)顯示,AMD 在2024年第三季度的數(shù)據(jù)中心業(yè)務(wù)收入達(dá)到了35.49億美元(按照當(dāng)前匯率計(jì)算,約合人民幣25

AMD數(shù)據(jù)中心業(yè)務(wù)首超英特爾,Nvidia異軍突起

長(zhǎng)期以來(lái),英特爾在數(shù)據(jù)中心CPU市場(chǎng)占據(jù)主導(dǎo)地位,其Xeon處理器為絕大多數(shù)服務(wù)器提供動(dòng)力。大約七、八年前,AMD的處理器在市場(chǎng)份額中還只是個(gè)位數(shù)。然而,這一局面已經(jīng)發(fā)生了翻天覆地的變化。盡管

RISC-V,即將進(jìn)入應(yīng)用的爆發(fā)期

自己增加指令和自己的功能。RISC-V架構(gòu)可以用于數(shù)據(jù)中心、車用、移動(dòng)設(shè)備等任何AI需求產(chǎn)品。

展望RISC-V前景,此前硅谷芯片傳奇Jim Keller曾指出,“RISC-V的潛力是

發(fā)表于 10-31 16:06

RISC-V擁有巨大市場(chǎng)潛力的原因

敏感的市場(chǎng)尤其有吸引力。

5、行業(yè)支持:越來(lái)越多的行業(yè)巨頭和初創(chuàng)公司開始支持RISC-V,這不僅包括芯片制造商,還包括軟件開發(fā)商和系統(tǒng)設(shè)計(jì)公司。2023年,包括谷歌、英特爾、英偉達(dá)、高

發(fā)表于 09-30 14:20

英特爾發(fā)布至強(qiáng)6性能核處理器,攜手生態(tài)加速數(shù)據(jù)中心算力升級(jí)

英特爾至強(qiáng)6處理器在云計(jì)算、數(shù)據(jù)中心架構(gòu)創(chuàng)新、綠色可持續(xù)發(fā)展等諸多領(lǐng)域的應(yīng)用實(shí)踐,并攜手多家產(chǎn)業(yè)伙伴進(jìn)行了聯(lián)合發(fā)布。

英特爾數(shù)據(jù)中心XPU產(chǎn)品最新進(jìn)展:預(yù)計(jì)2027年發(fā)布

據(jù)匈牙利媒體PROHARDVER!的最新報(bào)道,英特爾正緊鑼密鼓地在其內(nèi)部開發(fā)新一代數(shù)據(jù)中心XPU產(chǎn)品,并有望于2027年正式發(fā)布。這一消息標(biāo)志著英特爾在數(shù)據(jù)中心計(jì)算領(lǐng)域的又一重要布局,

risc-v的發(fā)展歷史

Foundation),旨在促進(jìn)RISC-V架構(gòu)的發(fā)展和推廣。該基金會(huì)由大量的企業(yè)和機(jī)構(gòu)支持,包括英特爾、Nvidia、谷歌、華為、IBM、紅帽、西部數(shù)據(jù)等。

2015年:

發(fā)表于 07-29 17:20

RISC-V適合什么樣的應(yīng)用場(chǎng)景

研發(fā)成本,不受任何專利或版權(quán)制約,這對(duì)于汽車電子等成本敏感型領(lǐng)域尤為重要。

5. 數(shù)據(jù)中心和云計(jì)算

高性能和能效比:RISC-V處理器在性能和能效比方面表現(xiàn)出色,適用于數(shù)據(jù)中心和云計(jì)算領(lǐng)域?qū)Ω咝阅苡?jì)算

發(fā)表于 07-29 17:16

RISC-V在中國(guó)的發(fā)展機(jī)遇有哪些場(chǎng)景?

的理想選擇。

生態(tài)系統(tǒng)建設(shè):多家頭部芯片公司和生態(tài)廠商正在積極推進(jìn)RISC-V在車規(guī)級(jí)產(chǎn)品的布局,這將有助于RISC-V在汽車領(lǐng)域的快速發(fā)展。

4. 數(shù)據(jù)中心和高性能計(jì)算(HPC)

性能與能效比

發(fā)表于 07-29 17:14

risc-v多核芯片在AI方面的應(yīng)用

應(yīng)用中的成本。

最后,RISC-V多核芯片不僅可以應(yīng)用于AI邊緣計(jì)算領(lǐng)域,還可以擴(kuò)展到其他領(lǐng)域,如數(shù)據(jù)中心、云計(jì)算、自動(dòng)駕駛、機(jī)器人等,為這些領(lǐng)域提供高效、靈活和安全的解決方案。

總的來(lái)說(shuō),R

發(fā)表于 04-28 09:20

賽昉科技與超聚變達(dá)成戰(zhàn)略合作,RISC-V在數(shù)據(jù)中心迎來(lái)歷史性跨越

;賽昉科技聯(lián)合創(chuàng)新中心,賽昉科技為數(shù)據(jù)中心場(chǎng)景打造的首款研發(fā)代號(hào)為“獅子山”的RISC-V芯片將應(yīng)用在超聚變的智算產(chǎn)品中。貫徹發(fā)展新質(zhì)生產(chǎn)力的時(shí)代要求,賽昉科技將持續(xù)打造具

RISC-V 基礎(chǔ)學(xué)習(xí):RISC-V 基礎(chǔ)介紹

同一個(gè)存儲(chǔ)器的不同物理位置,因此程序指令和數(shù)據(jù)的寬度相同,如英特爾公司的8086中央處理器的程序指令和數(shù)據(jù)都是16位寬。

數(shù)學(xué)家馮·諾依曼提出了計(jì)算機(jī)制造的三個(gè)基本原則,即采用二進(jìn)制邏輯、程序存儲(chǔ)執(zhí)行

發(fā)表于 03-12 10:25

【RISC-V開放架構(gòu)設(shè)計(jì)之道|閱讀體驗(yàn)】 RISC-V設(shè)計(jì)必備之案頭小冊(cè)

。在書中,特別提到了匯編器對(duì)于RISC-V中的作用,包括當(dāng)講寄存器硬連線為0時(shí),可以使用偽指令來(lái)簡(jiǎn)化常規(guī)操作,如跳轉(zhuǎn)、返回和等于零時(shí)分支等。

浮點(diǎn)運(yùn)算和壓縮指令數(shù)據(jù)集的知識(shí)則是放在下一次的帖子中說(shuō)。

發(fā)表于 01-22 16:24

英特爾與谷歌開始為RISC-V進(jìn)軍數(shù)據(jù)中心鋪路

英特爾與谷歌開始為RISC-V進(jìn)軍數(shù)據(jù)中心鋪路

評(píng)論