目前商用領域的成像系統還是以嵌入式ASIC為主(成品時間快,性價比高),對于一些軍工、醫學等特殊領域還是以FPGA為主,在特殊領域里延遲是最先考慮的問題(成本不是主要問題),所以今天介紹一下使用FPGA實現低延遲的成像系統,這里說明一下,整個系統調試比較麻煩(和sensor有關),很大可能調試不出圖像,所以大家只需要知道有這個架構即可,有需求可以自己調試。

低延遲架構

我們這次使用的是AMD-Xilinx FPGA,大部分的圖像處理都有IP可以使用,在官方文檔中有相關的架構,具體如下:

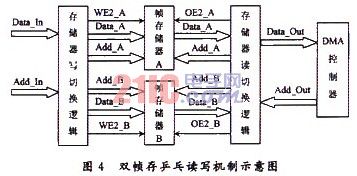

上面的架構是比較通用的架構,官方也有例程可以參考,但是上面架構多了一個VDMA,這就導致視頻傳輸的時候有1到幾幀的延遲,這對于低延遲、高分辨率的情形肯定是不能容忍的。所以官方對于特殊情況建議使用下面的架構:

去掉了VDMA,但是對于時鐘系統要去更高,對于視頻輸入輸出在不同時鐘域情況下是使用不了的,所以整體要求比較高。但是砍掉了VDMA和DDR,所以整體成本會低很多。關于沒有VDMA情況下的各個IP的設置及測試可以看下面的文章《不使用VDMA情況下使用AXI4總線實現視頻輸入輸出(低延遲首選)》。

FPGA系統架構設計

我們還是參考上面的架構來設計我們的系統。

當我們與圖像sensor對接時,我們通常會以不同的格式接收圖像,例如 MIPI 、并行接口,在我們接收視頻之前,我們需要先配置sensor按照我們的需求運行。通常,sensor需要通過 I2C 或 SPI 進行配置。

這次演示的平臺:

7系列FPGA

MT9M114 sensor

sensor 的接口非常簡單,可以分為視頻接口和配置接口(IIC)。

視頻接口由 10 位數據(分為 8 位和 2 位)、幀和行有效、像素時鐘和參考時鐘 (24 MHz) 組成。

配置接口由連接到sensor的 I2C 和 復位IO組成。

該解決方案的架構如下:軟核處理器(MicroBlaze)通過 I2C 配置sensor。雖然圖像處理路徑將在 FPGA 中實現,但由于這是一種低成本應用,該解決方案不會使用 DDR 存儲器中實現外部幀緩沖區,而是圖像處理流水線將完全在 FPGA 中實現。

Sensor中由于我們配置的是RAW數據,所以還需要使用Sensor Demosaic和Gamma(基本成像IP)IP。

該設計還將使用軟核處理器來控制視頻時序和圖像處理路徑的其他相關配置任務。

Vivado 工程構建

搭建MicroBlaze 系統

這一部分比較簡單,可以看看之前的文章《【Vivado那些事兒】MicroBlaze最小系統搭建及程序固化》

添加其他IP

整個系統需要的IP主要如下:

CAM 接口 - 此接口與 sensor接口連接,簡單處理數據(選擇RAW數據的位數),此IP非必須

Video to AXIS - 這會將并行視頻轉換為 AXI 流格式

Sensor Demosaic - 將代表 R、G 或 B 的 RAW 像素值轉換為 24 位 RGB 格式

Video Timing Generator - 生成輸出格式的視頻時序信號

AXI Stream to Video Out - 將 AXI Stream 轉換為并行視頻

AXI IIC - 連接到 MicroBlaze,用于配置sensor

AXI UART - 連接到 MicroBlaze,用于軟件調試

添加完后就可以連線了,完整的框圖應如下所示。完整的工程在文章最后給出。

在 AXI Stream 中,使用 TUser 指示幀的開始,使用 TLast 指示行的結束。

IP的關鍵設置

Video to AXIS

Sensor Demosaic

AXI IIC 設置

其他IP可以查看文章最后的工程查看。

資源使用率

在Arty S7-50 的總利用率如下所示。

SDK 中編寫軟件

生成 Vivado 硬件后,下一步就是編寫應用軟件,用于配置sensor和視頻處理IP核。

因此,軟件中將執行以下操作:

初始化 AXI IIC、VTC 和中斷控制器

設置AXI 相關中斷控制器 - 這包括三個中斷服務例程。IIC 發送、接收和狀態各一個。

在 VTC 配置輸出時序

通過 I2C 復位sensor并點亮 sensor板子上 LED

通過I2C讀取sensor-MT9M114的ID,來檢測相機是否存在(外圍設置是否正確)

通過 I2C 配置和初始化相機 - 這是最浪費時間的,好在有很多資料可以參考

初始化相機后,我們將能夠在 ILA 上看到視頻流。

調試過程中測量的FPGA和sensor之間的 I2C 通信信號。

使用 AXI UART 調試軟件:

一旦相機初始化,我們可以使用 ILA 采集信號:

上圖顯示了 1280 像素的線寬。

AXI Stream 是一種單向總線,用于將數據從主機傳輸到從機,作為數據流,它不包含地址通道。為了通過 AXI 流控制流和傳遞視頻時序信息,我們使用了以下信號:

TReady - 當準備好接收數據時由下游外設斷言

TValid - 當輸出數據有效時通過發送外設斷言

TUser - 為幀的開始發出

TLast - 為行尾標志

由于我們沒有 使用VDMA,所以 AXIS 流上的視頻輸出是一個連續塊,并且 TValid 在活動像素周期內不會斷言和取消斷言。

我們可以通過使用圖像處理鏈的像素時鐘來確保 Tvalid 是連續的。

軟件部分還是參考最后的工程吧,除了sensor需要單獨編寫,其他都是由SDK自帶的例程修改而來。

總結

雖然上面的架構和最后的設計比較簡單,但是調試起來還是很難得,只不過我寫的比較簡單,一旦出不來視頻,重點按照最開始官方架構檢查PCLK。

該工程主要參考架構和架構中時鐘域的處理,注意pCLK(像素時鐘)和ACLK的走向。

-

FPGA

+關注

關注

1629文章

21742瀏覽量

603537 -

asic

+關注

關注

34文章

1200瀏覽量

120513 -

成像系統

+關注

關注

2文章

196瀏覽量

13932

發布評論請先 登錄

相關推薦

FPGA的B超成像系統圖像采集的原理和實現

如何實現視頻采集與DVI成像設計?

怎么設計基于FPGA多波束成像的聲納系統?

【MPS電源評估板試用申請】基于FPGA的紅外熱成像系統

怎么實現IGBT延遲導通時間測量系統的設計?

FPGA的多路可控脈沖延遲系統設計

基于FPGA多波束成像的聲納系統設計

基于Flash FPGA器件實現脈沖延遲控制系統的設計

基于使用FPGA實現低延遲的成像系統

基于使用FPGA實現低延遲的成像系統

評論