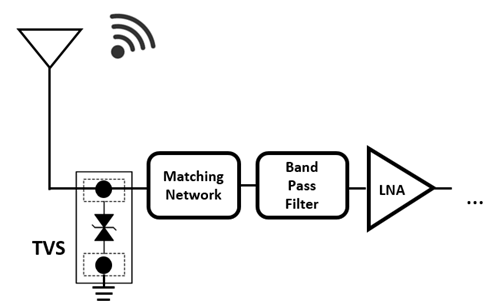

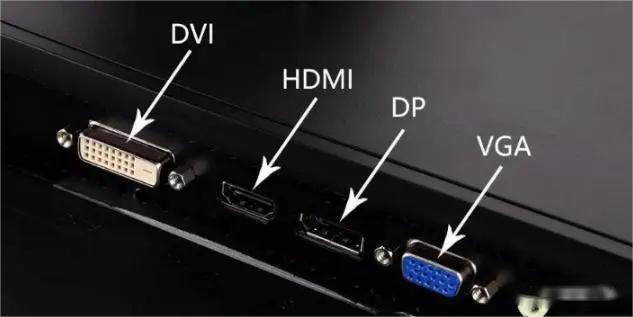

隨著晶片先進制程的演進,晶片對于抵御外在ESD/EOS干擾的能力越來越弱,進而造成對外接口(例如:USB, HDMI, LAN等)對于ESD/EOS等能量的抗擾能力下降。為了提升系統(tǒng)的ESD/EOS防護效果,在各對外接口加上TVS元件已變成系統(tǒng)產(chǎn)品設計的趨勢,因此以下將介紹挑選TVS元件時必須注意的參數(shù)。

AMAZINGIC晶焱科技TVS Layout與系統(tǒng)對于ESD的防護能力探討

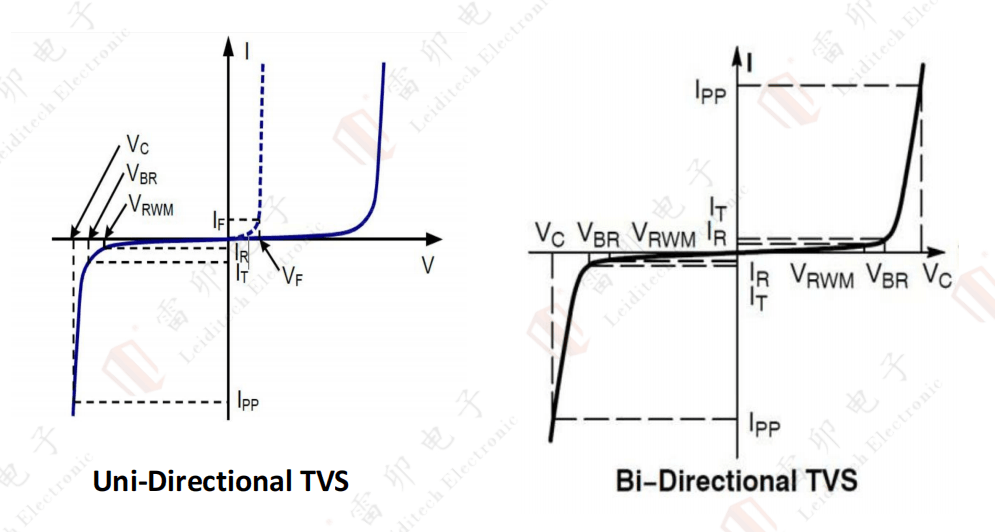

挑選適當?shù)腡VS 防護元件應注意以下參數(shù): (1)工作電壓(VRWM),確保您訊號在正常工作的情形下不被影響,因此TVS的工作電壓不小于訊號的工作電壓; (2)電容值,TVS元件的寄生電容值過大會造成高速訊號傳輸異常,因此需選擇適當大小的電容值以避免訊號受到影響; (3)鉗制電壓,對于TVS保護元件而言,此參數(shù)格外重要,越低的鉗制電壓能夠提供系統(tǒng)越好的ESD/EOS防護效果。

前面所提及TVS的鉗制電壓為影響防護ESD/EOS效果的重要參數(shù),但如果在系統(tǒng)電路中沒有合適的layout擺放TVS,即便是保護效果再好的TVS元件,當遇到ESD/EOS能量沖擊時,也無法有效的發(fā)揮TVS的保護效果,最終造成系統(tǒng)的損壞。以下將探討TVS Layout對于系統(tǒng)防護效果的影響。

針對layout方式主要提供兩部份的建議:

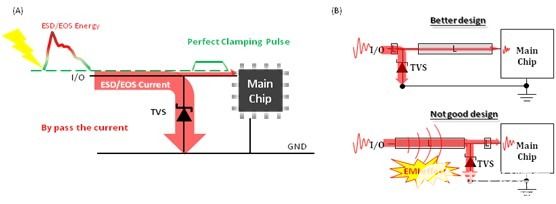

(一)TVS應盡可能靠近外部接口擺放 由圖一可見,當TVS擺放位置為靠近外部接口(I/O)時,外部能量可以快速經(jīng)由TVS將大多數(shù)的能量宣泄至地,此為較佳的擺放方式;但當TVS擺放位置距離外部接口較遠時,外部能量有可能造成訊號的擾動,因此造成在TVS做到進行保護之前就干擾到整個系統(tǒng)的運作。

圖一、

(A)TVS元件于線路中遭遇外部能量時的外部能量導通示意圖

(B)當外部能量進入時TVS距離端口遠近對于訊號干擾的差異

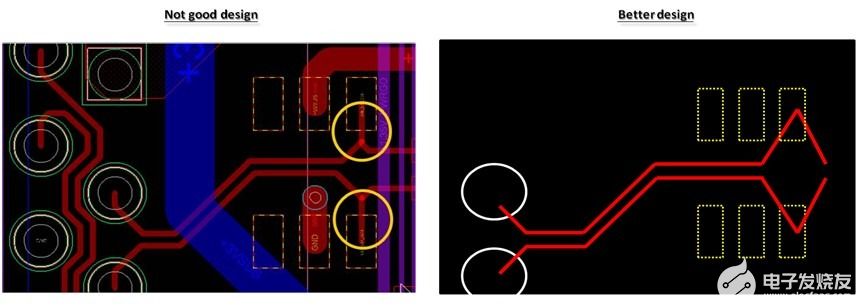

(二)TVS應避免走分支路徑 當PCB布線空間狹小時,為了方便擺放TVS,有時會將訊號線另外拉線后接到TVS進行使用,如圖二(左)。類似此種另加引線的布線方式將導致TVS無法達到最有效的防護效果。通常于TVS建議走線時,都建議將預保護的訊號線直接通過TVS,并且不建議使用而外拉線的方式進行使用。后續(xù)我們也以實測結果來模擬系統(tǒng)線路設計時,TVS的分支路徑對于TVS保護效果的影響。

圖二、TVS走線方式

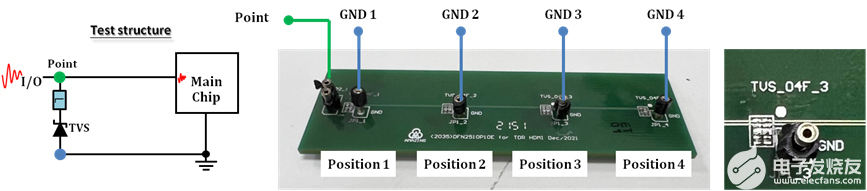

圖三為實驗測試板,此實驗以AZ1143-04F進行測試,板子最左側為訊號線位置,并且在訊號線上設計不同的TVS放置位置,用于模擬當TVS距離訊號不同距離時,TVS對于系統(tǒng)保護上所產(chǎn)生的變化;而板子位置上,由左至右分別為Position 1至Position 4,并透過TLP系統(tǒng)量測不同位置下的TVS與線路上距離所造成的鉗制電壓差異,以此作為TVS防護效果變化的依據(jù)。為了著重于訊號線與TVS之間的距離對于鉗制電壓的影響,因此在測試版設計上,將GND部分以最接近TVS元件進行設計,以降低地回路對于整體實驗的影響。

圖三、實驗測試版

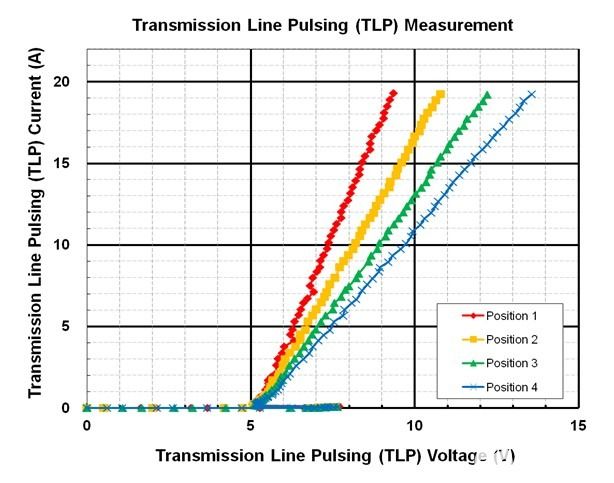

由量測TLP結果(圖四)可知,在相同TLP電流16A的情況下,Position 1所量測到的鉗制電壓最低(8.6V),而Position 4所量測到的鉗制電壓最高(12.2V);隨著TVS距離預保護線路越遠,后端晶片所看見的鉗位電壓就越高,表示保護效果越差。

圖四、Position 1-4利用TLP系統(tǒng)量測實驗線路上的TVS鉗制電壓結果

透過以上實驗可以證明,在系統(tǒng)電路設計時,TVS防護元件LAYOUT的方式會影響到TVS對于系統(tǒng)的保護效果,在進行電路保護規(guī)劃時,保護元件應盡量靠近外部接口(Connector)擺放并且TVS應直接擺放于預保護之訊號上,能使TVS元件對于系統(tǒng)ESD/EOS的防護效果較佳化,以達到提升系統(tǒng)抵抗外部ESD/EOS干擾的能力。

審核編輯:湯梓紅

-

ESD

+關注

關注

49文章

2046瀏覽量

173128 -

TVS

+關注

關注

8文章

792瀏覽量

60658 -

Layout

+關注

關注

14文章

405瀏覽量

61852

發(fā)布評論請先 登錄

相關推薦

PGA411輸入防護加入TVS后報故障怎么解決?

帶回掃TVS二極管優(yōu)點

汽車BMS浪涌靜電防護設計方案及保護器件選型

全芯片ESD防護網(wǎng)絡

ESD/EOS防護怎么做效果最好?為什么加了TVS的芯片IO口還是被浪涌燒了?

3.7V鋰電池浪涌靜電保護用TVS/ESD二極管

TVS Layout與系統(tǒng)對于ESD的防護能力探討

TVS Layout與系統(tǒng)對于ESD的防護能力探討

評論