HDLBits: 在線學習 SystemVerilog(十)-Problem 43-59

HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

網址如下:

https://hdlbits.01xz.net/

縮略詞索引:

SV:SystemVerilog

從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

今天更新整個Basic Gates一小節題目(Problem 43-59)。

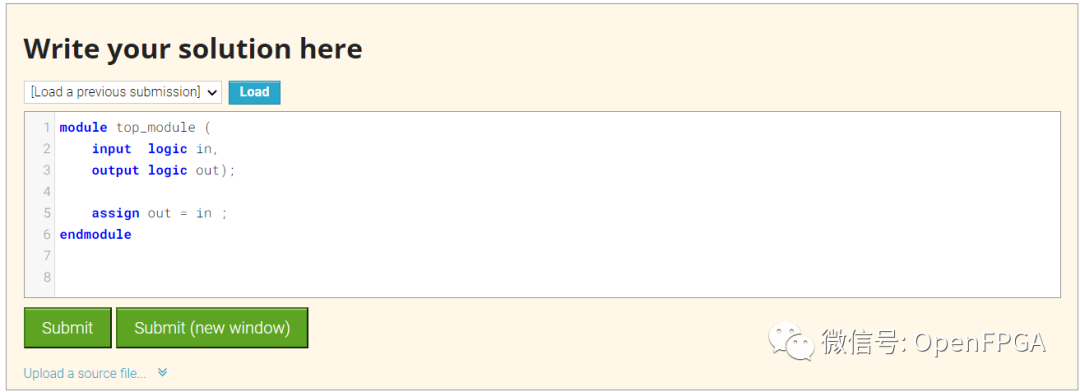

Problem 43-m2014_q4h

題目說明

實現如下電路:

圖片來源:HDLBits

模塊端口聲明

moduletop_module( inputin, outputout);

題目解析

這個題目沒什么難度,看下面參考代碼即可:

moduletop_module( inputlogicin, outputlogicout); assignout=in; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

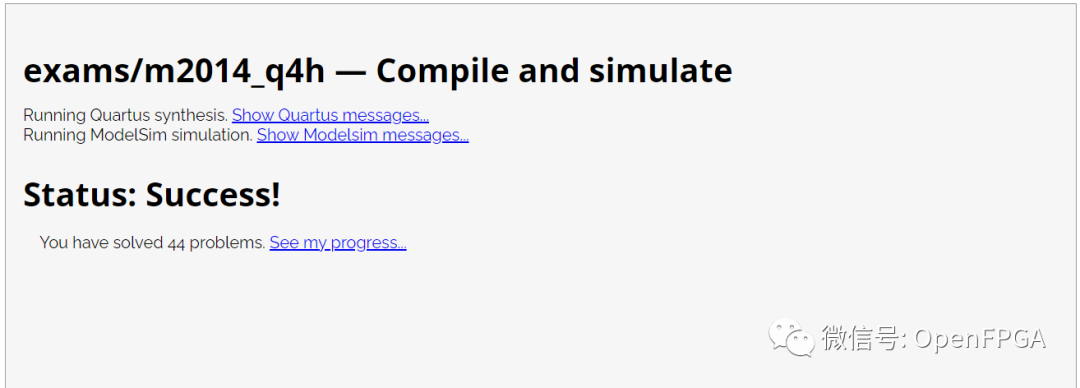

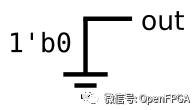

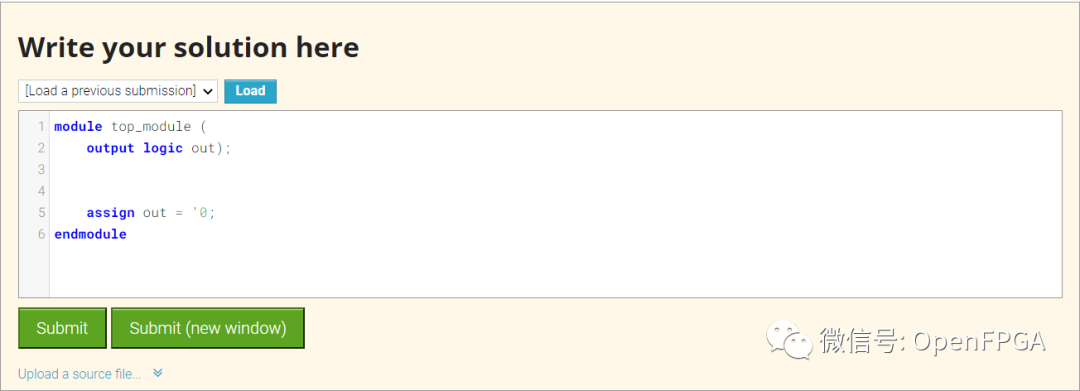

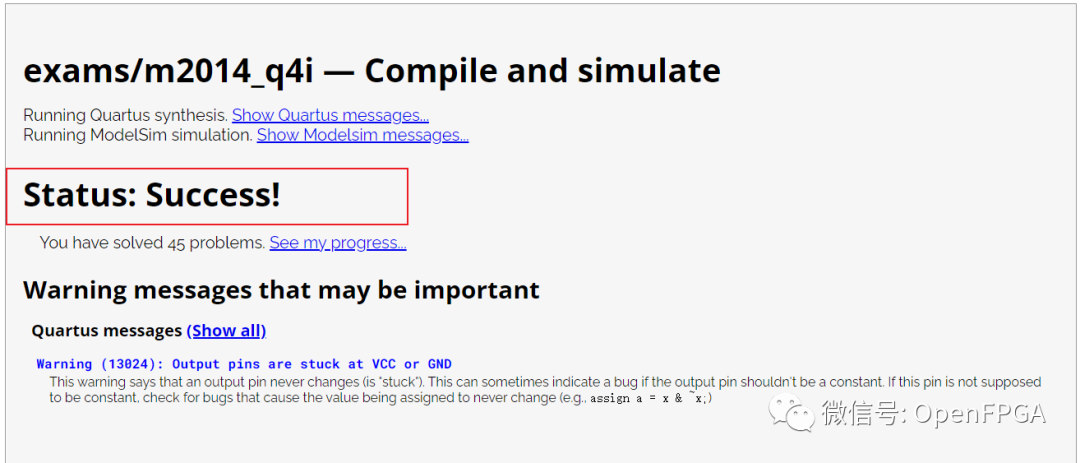

Problem 44-m2014 q4i

題目說明

實現下面電路:

圖片來源:HDLBits

模塊端口聲明

moduletop_module( outputout);

題目解析

這道題難度不大核心代碼只有一行。

簡單解答

moduletop_module( inputlogic[7:0]in, outputlogicparity ); assignparity=^in; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的無波形。

這一題就結束了。

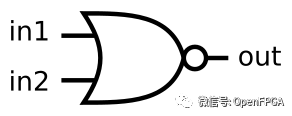

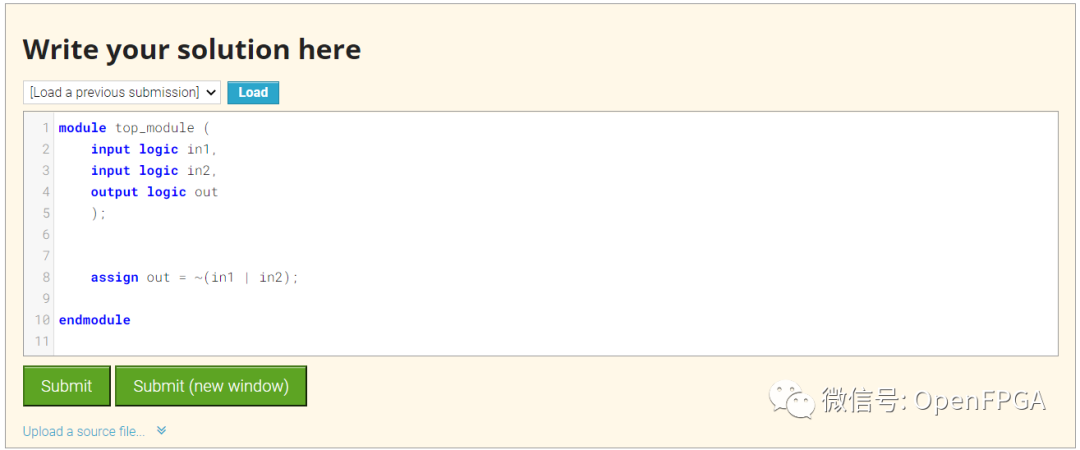

Problem 45-m2014_q4e

題目說明

實現以下電路:

圖片來源:HDLBits

模塊端口聲明

moduletop_module( inputin1, inputin2, outputout);

題目解析

還是看懂電路即可。

moduletop_module( inputlogicin1, inputlogicin2, outputlogicout ); assignout=~(in1|in2); endmodule

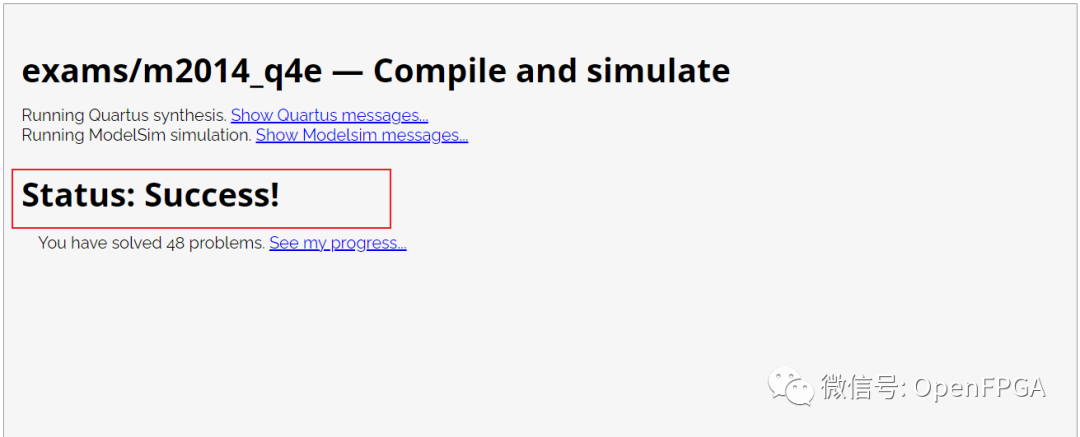

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

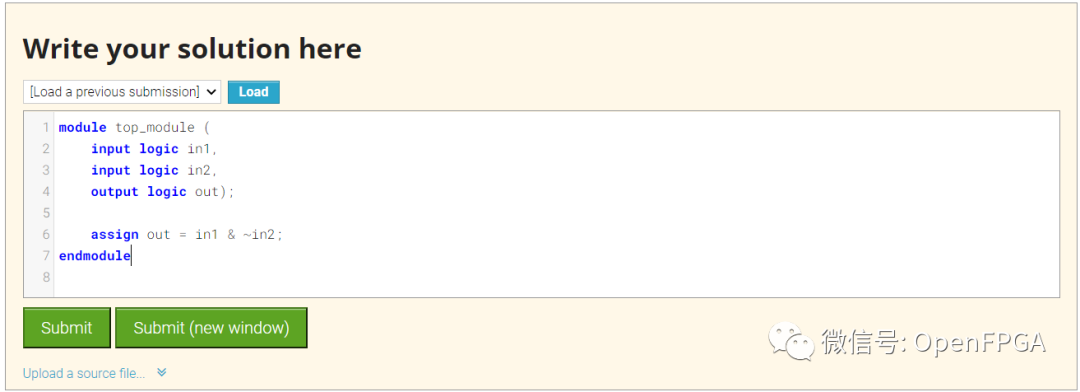

Problem 46-m2014_q4f

題目說明

實現以下電路

圖片來源:HDLBits

模塊端口聲明

moduletop_module( inputin1, inputin2, outputout);

題目解析

注意輸入端口前的非門。

moduletop_module( inputlogicin1, inputlogicin2, outputlogicout); assignout=in1&~in2; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

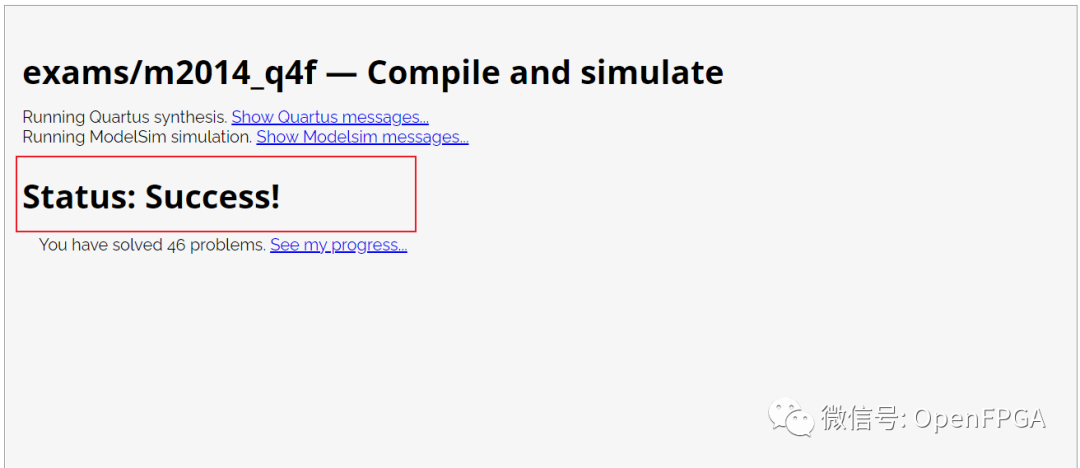

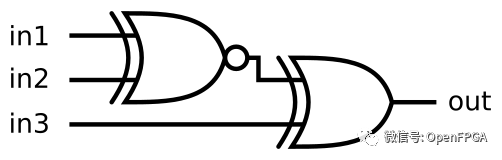

Problem 47-m2014_q4g

題目說明

實現以下電路:

圖片來源:HDLBits

圖片來源:HDLBits

模塊端口聲明

moduletop_module( inputin1, inputin2, inputin3, outputout);

題目解析

還是看懂電路即可。

moduletop_module( inputlogicin1, inputlogicin2, inputlogicin3, outputlogicout); assignout=(in1~^in2)^in3; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

Problem 48-Gates

題目說明

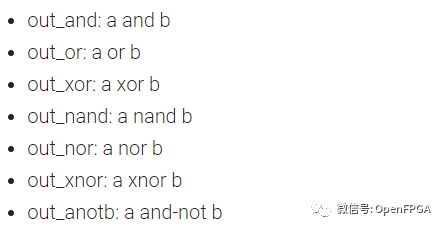

本題希望我們用兩輸入的組合電路來實現如下功能,該電路共用于7個輸出,具體情況如下:

模塊端口聲明

moduletop_module( inputa,b, outputout_and, outputout_or, outputout_xor, outputout_nand, outputout_nor, outputout_xnor, outputout_anotb );

題目解析

多種組合邏輯的實現。

moduletop_module( inputlogica,b, outputlogicout_and, outputlogicout_or, outputlogicout_xor, outputlogicout_nand, outputlogicout_nor, outputlogicout_xnor, outputlogicout_anotb ); assignout_and=a&b; assignout_or=a|b; assignout_xor=a^b; assignout_nand=~(a&b); assignout_nor=~(a|b); assignout_xnor=a~^b; assignout_anotb=a&~b; endmodule

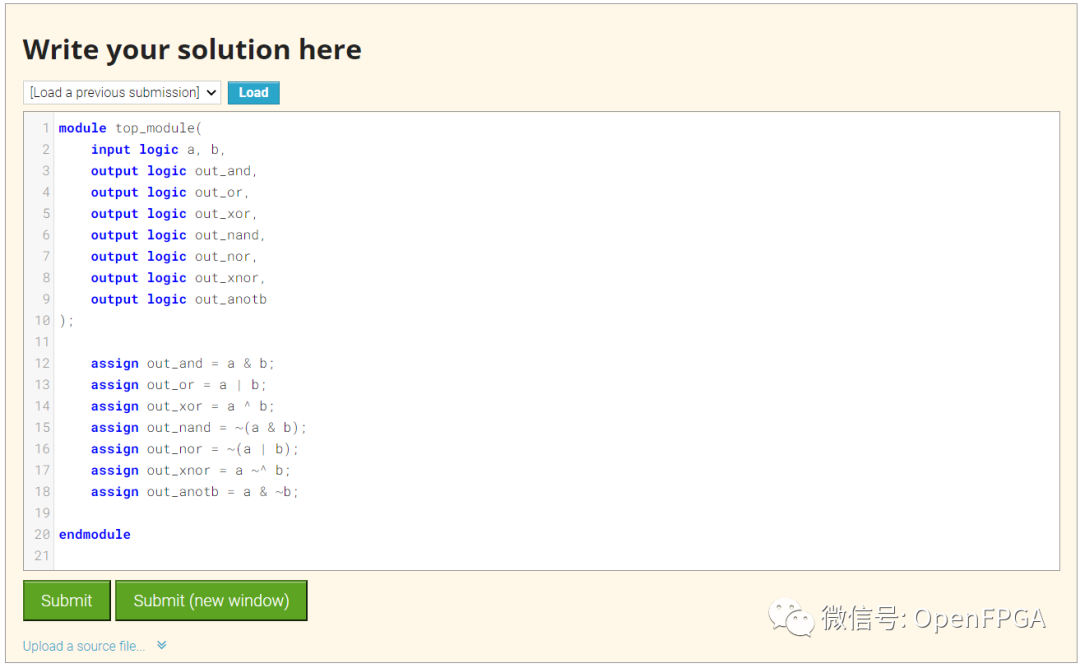

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

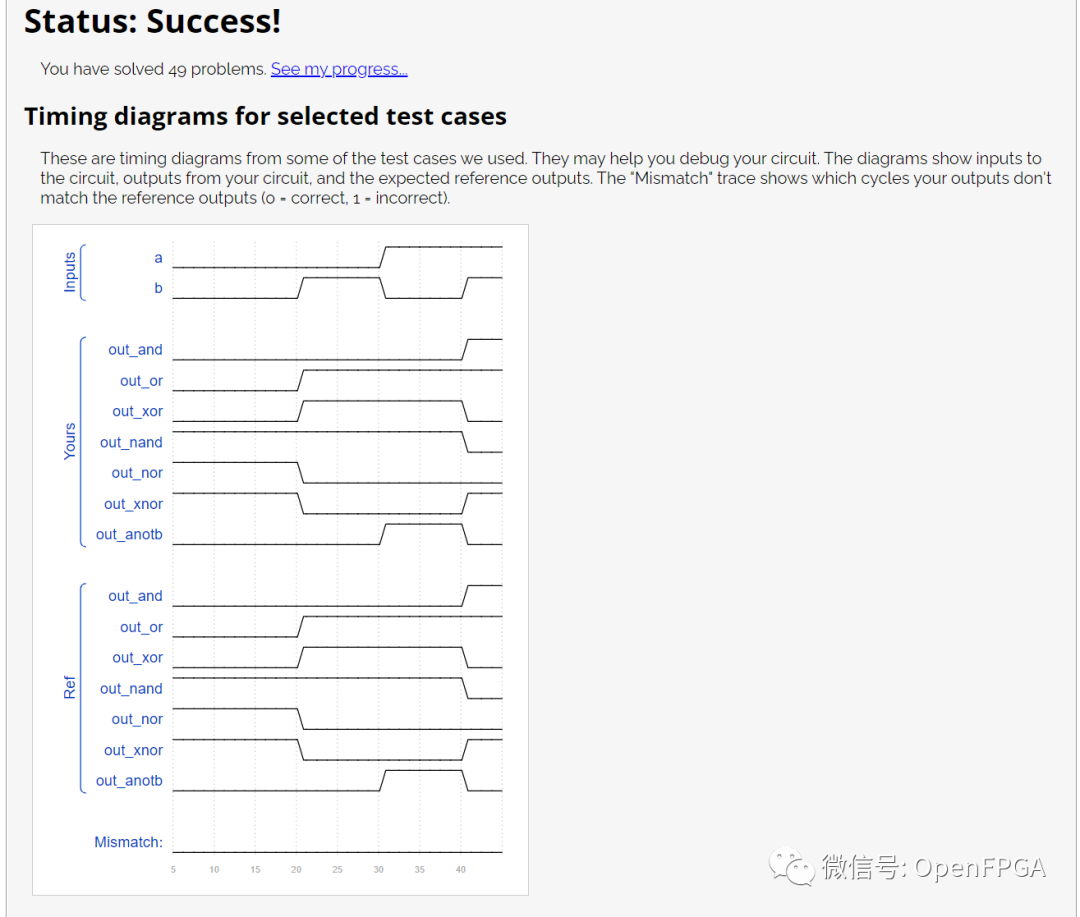

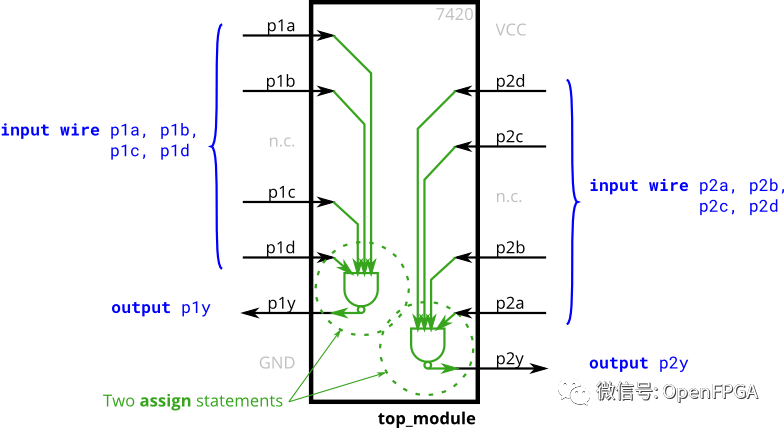

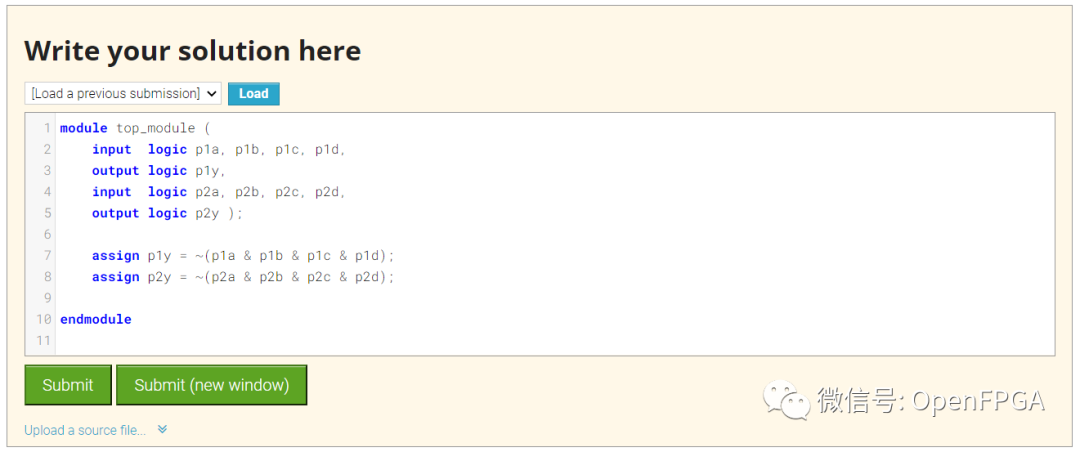

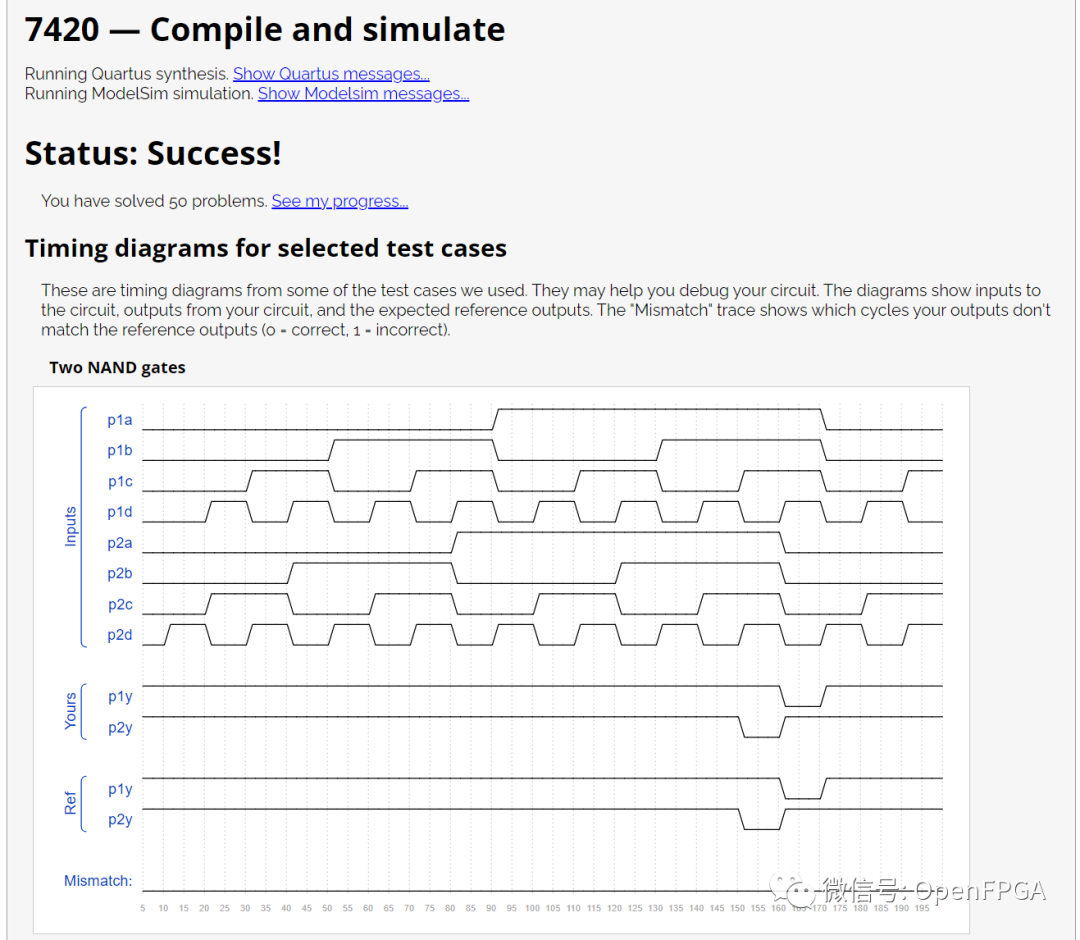

Problem 49-7420

題目說明

7420 chip是擁有兩組4輸入的與非門芯片,本練習需要構造一個與7420 chip功能一樣的電路,擁有8個輸入與2個輸出。

圖片來源:HDLBits

圖片來源:HDLBits

模塊端口聲明

moduletop_module( inputp1a,p1b,p1c,p1d, outputp1y, inputp2a,p2b,p2c,p2d, outputp2y);

題目解析

這個題目無需理解7420是干什么的,只需要按照圖中電路圖實現邏輯即可。

moduletop_module( inputlogicp1a,p1b,p1c,p1d, outputlogicp1y, inputlogicp2a,p2b,p2c,p2d, outputlogicp2y); assignp1y=~(p1a&p1b&p1c&p1d); assignp2y=~(p2a&p2b&p2c&p2d); endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

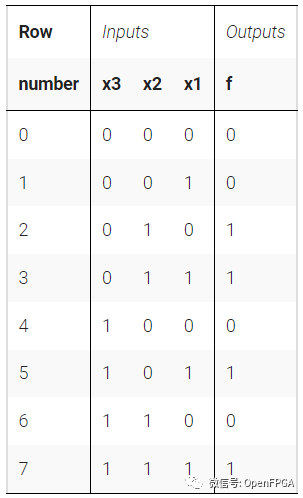

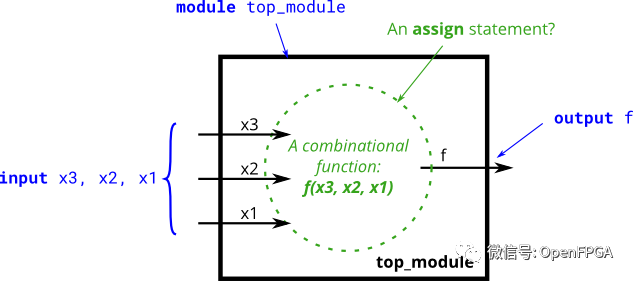

Problem 50-Truthtable1

開始練習真值表了,網站上有些實例講解,我就不翻譯了,學過數電的應該難度都不大。

題目說明

創建一個實現下述真值表的組合電路:

真值表如下:

圖片來源:HDLBits

圖片來源:HDLBits

最終實現的硬件框圖如下:

圖片來源:HDLBits

圖片來源:HDLBits

TIPS:約一行代碼解決問題

模塊端口聲明

moduletop_module( inputx3, inputx2, inputx1,//threeinputs outputf//oneoutput );

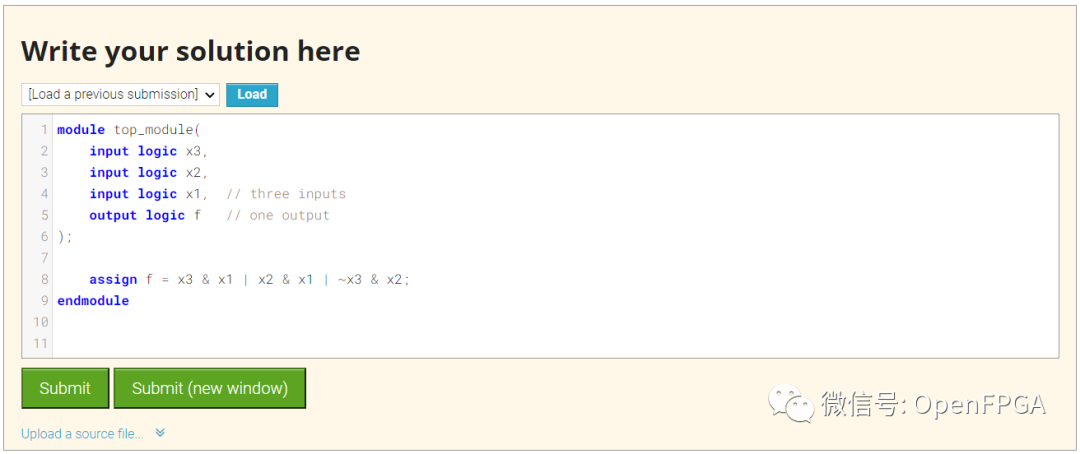

題目解析

這個題目重點是真值表化簡,將上面的真值表化簡成最小項表達式即可。具體可以看下數電書很容易得到結果。

moduletop_module( inputlogicx3, inputlogicx2, inputlogicx1,//threeinputs outputlogicf//oneoutput ); assignf=x3&x1|x2&x1|~x3&x2; endmodule

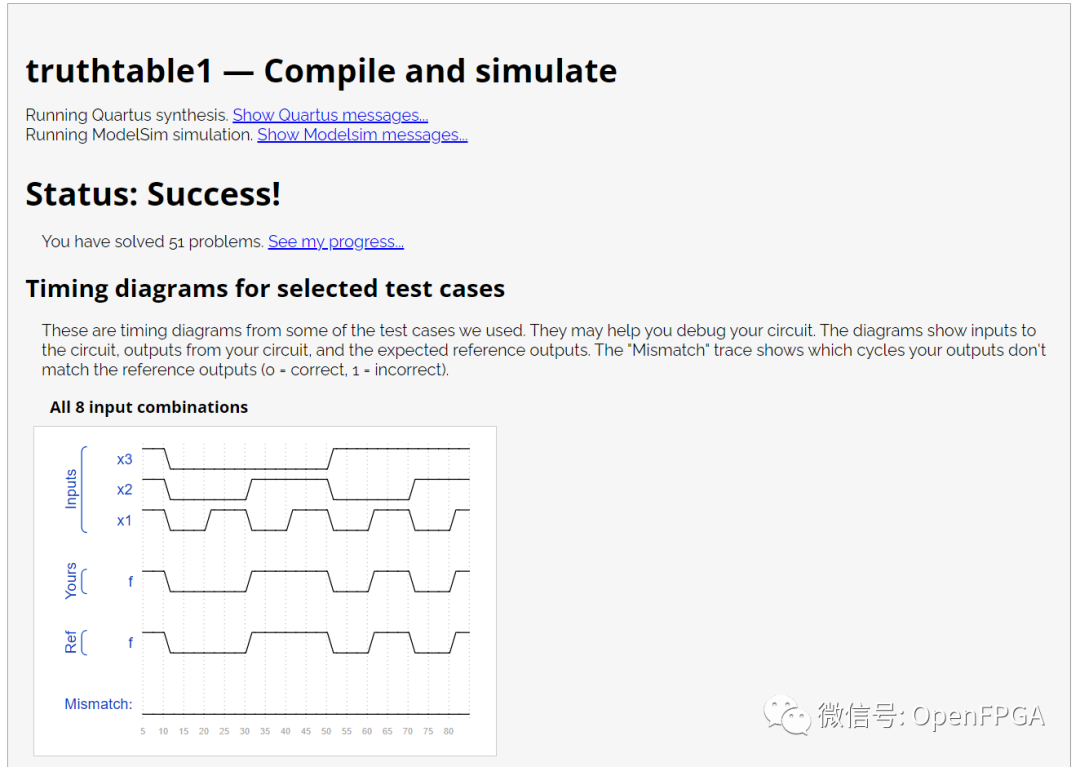

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 51-Mt2015_eq2

題目說明

創建一個具有兩個 2 位輸入A[1:0]和B[1:0]的電路,并產生一個輸出z。如果A = B ,則z的值應為 1 ,否則z應為 0。

模塊端口聲明

moduletop_module(input[1:0]A,input[1:0]B,outputz);

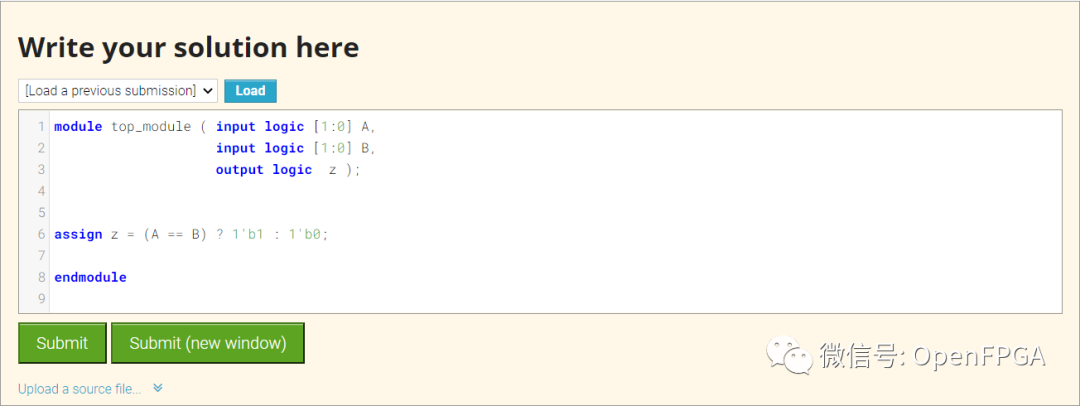

題目解析

這個題目重點是靈活使用三元運算符,因為這個語法比較簡單,所以大家注意一下使用方式即可~

moduletop_module(inputlogic[1:0]A, inputlogic[1:0]B, outputlogicz); assignz=(A==B)?1'b1:1'b0; endmodule

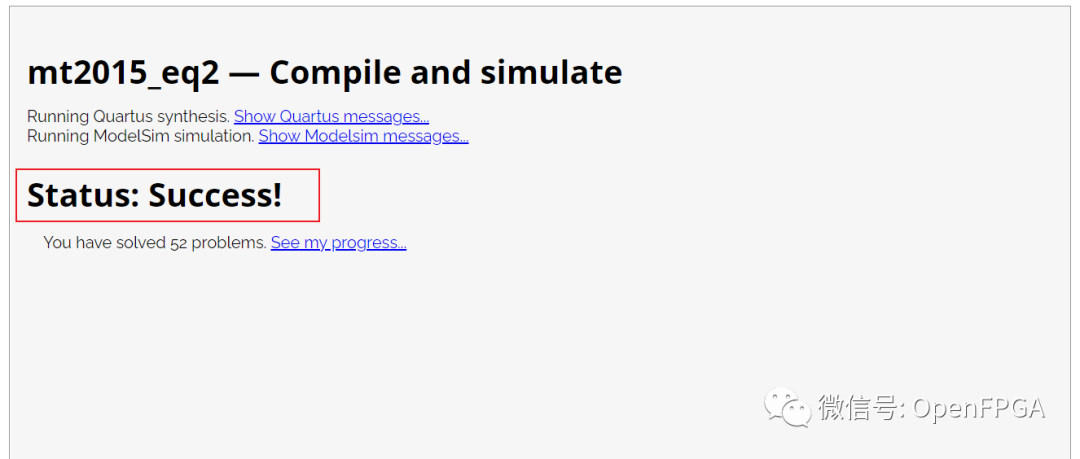

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

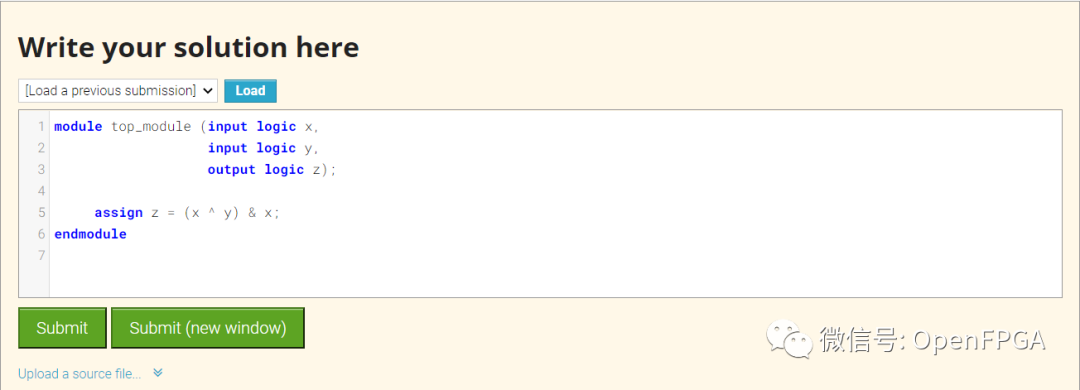

Problem 52-Mt2015_q4a

題目說明

實現模塊 A ,該模塊實現函數z = (x^y) & x。

模塊端口聲明

moduletop_module(inputx,inputy,outputz);

題目解析

moduletop_module(inputlogicx, inputlogicy, outputlogicz); assignz=(x^y)&x; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

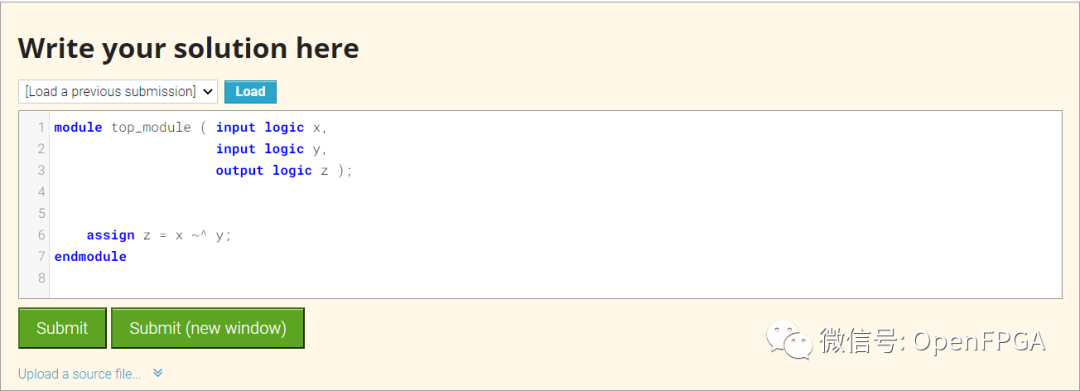

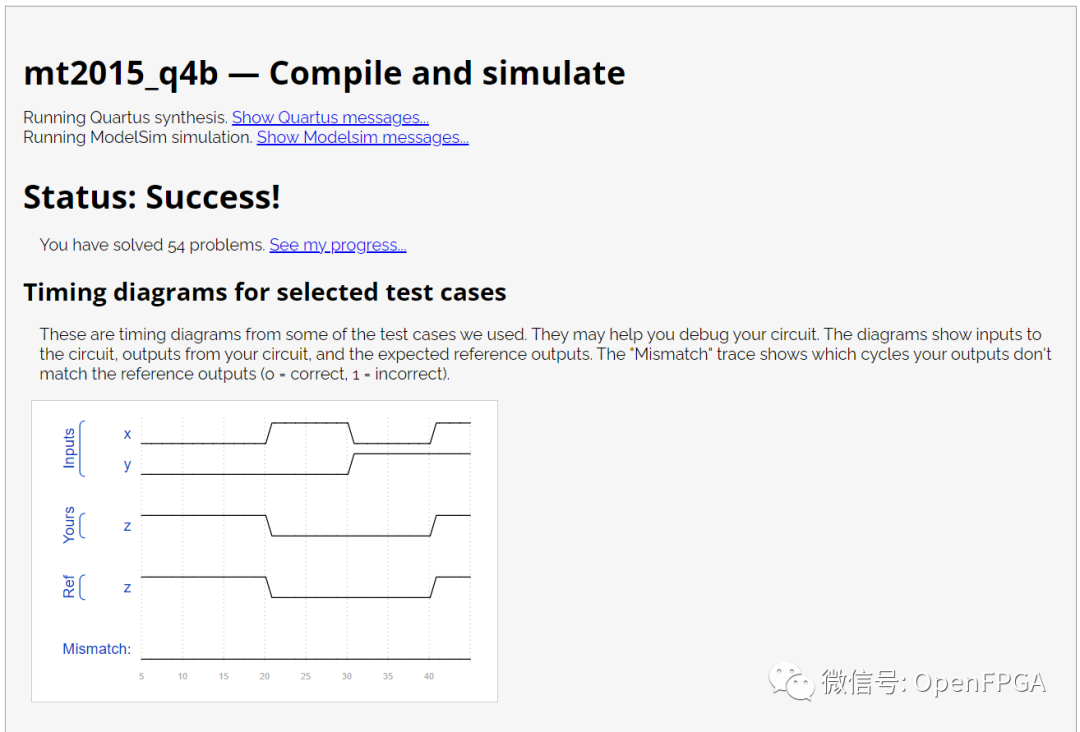

Problem 53-Mt2015_q4b

題目說明

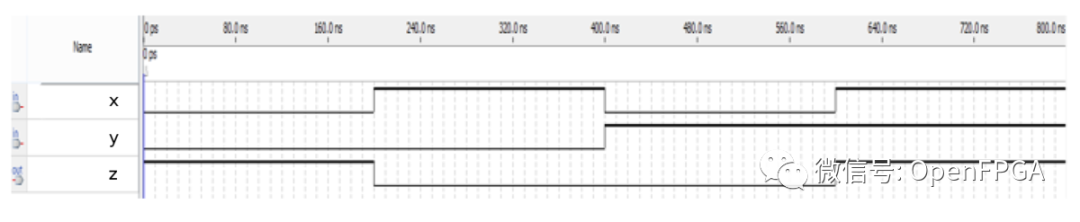

電路B可以用下面的仿真波形來描述:

圖片來源:HDLBits

圖片來源:HDLBits

模塊端口聲明

moduletop_module(inputx,inputy,outputz);

題目解析

這個題目可以使用采點的方式,選擇幾個特殊點,制作成真值表,然后化簡即可。

或者從波形上看特點:根據觀察所得輸出 z 為 x 與 y 的同或輸出,即相同為1, 不同為0;故實現代碼如下:

moduletop_module(inputlogicx, inputlogicy, outputlogicz); assignz=x~^y; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

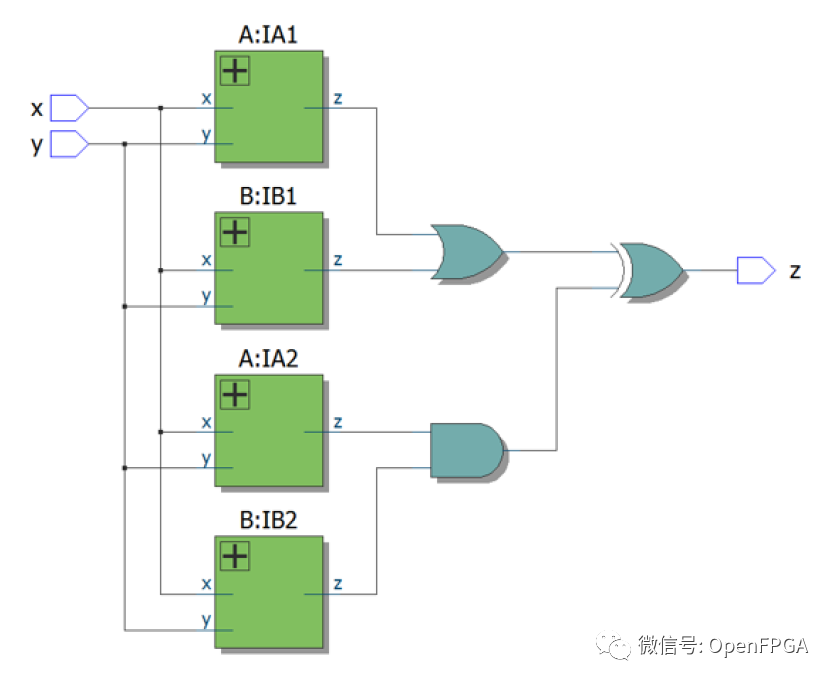

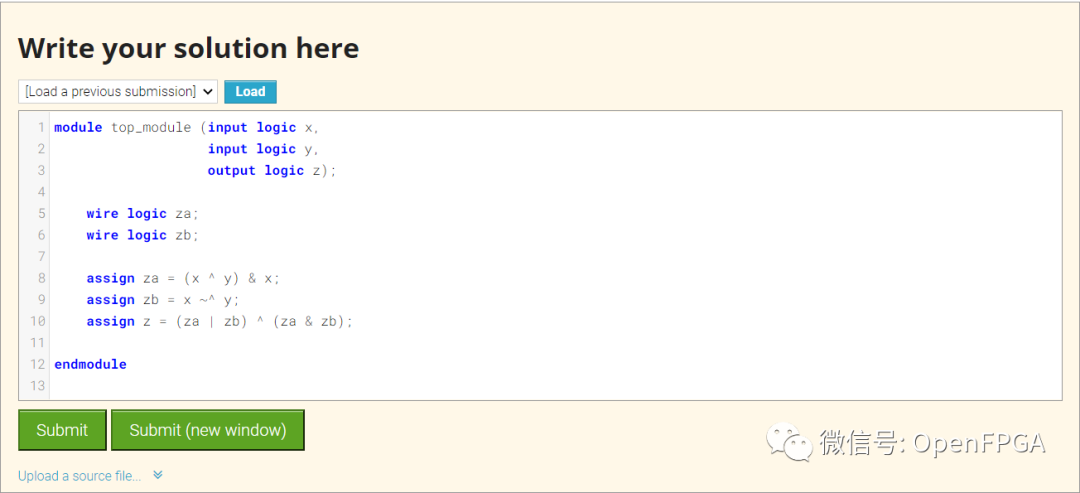

Problem 54-Mt2015_q4

題目說明

根據子模塊Problem 52 與 53 來實現如下電路:

圖片來源:HDLBits

圖片來源:HDLBits

模塊端口聲明

moduletop_module(inputx,inputy,outputz);

題目解析

這個題目重點知道題目中A、B代表什么,其實這兩個就是上面兩道題目實現的子模塊,然后在將這兩個模塊的輸出進行邏輯操作即可。

moduletop_module(inputlogicx, inputlogicy, outputlogicz); wirelogicza; wirelogiczb; assignza=(x^y)&x; assignzb=x~^y; assignz=(za|zb)^(za&zb); endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

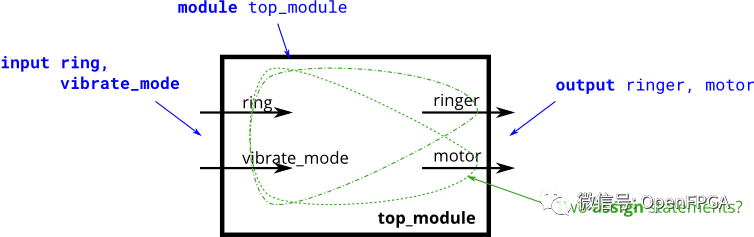

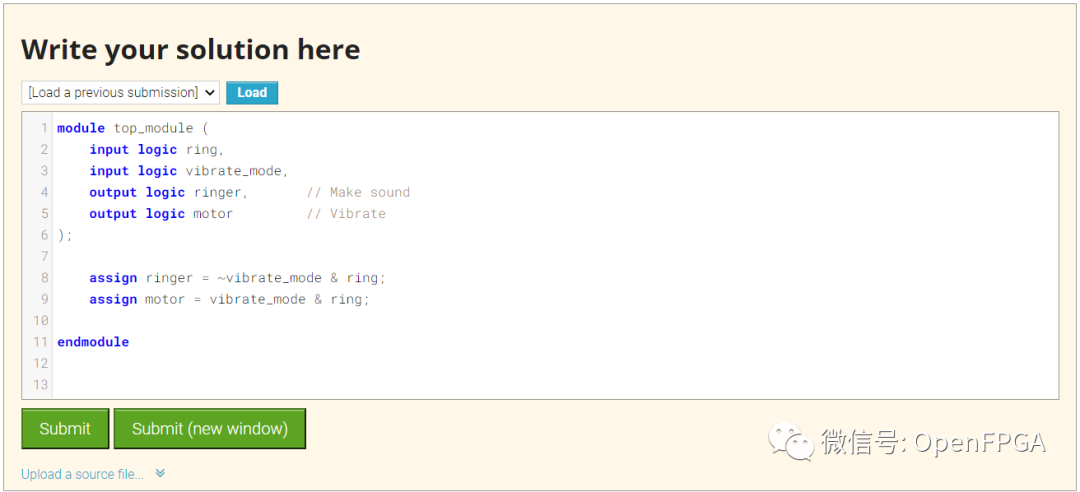

Problem 55-Ringer

題目說明

假設您正在設計一個手機的振鈴器和振動電機控制電路。每當電話需要從來電中振鈴 (input ring) 時,您的電路必須打開振鈴器 (output motor = 1 ) 或電機 (output ringer = 1),但不能同時打開這兩個。如果手機處于振動模式 (input vibrate = 1),請打開電機( output motor = 1 )。否則,打開鈴聲。

我們嘗試僅適用assign語句來實現該組合電路。

設計提示:在設計電路時,人們經常不得不“倒退”地考慮問題,從輸出開始,然后再向輸入倒退,這是屬于軟件編程思想。硬件電路的編程與軟件的編程是存在差異的,一般進行軟件編程時,我們是先關注輸入( if (input are _)),再關注輸出( then (output are ))。而在硬件編程時,我們需要轉變思維方式,在確保輸出是正確的情況下,再思考輸入。( The (output should be _) when (inputs are __))。

上面的問題描述是用適合軟件編程的命令式寫成的(if ring then do this),所以你必須把它轉換成更適合硬件實現的聲明式(assign ringer = ___)。能夠在兩種風格之間進行思考和轉換是硬件設計所需的最重要技能之一。

圖片來源:HDLBits

圖片來源:HDLBits

模塊端口聲明

moduletop_module( inputring, inputvibrate_mode, outputringer,//Makesound outputmotor//Vibrate );

題目解析

題目難度不大,重點是根據輸出的兩個信號,裁決輸入邏輯。

moduletop_module( inputlogicring, inputlogicvibrate_mode, outputlogicringer,//Makesound outputlogicmotor//Vibrate ); assignringer=~vibrate_mode˚ assignmotor=vibrate_mode˚ endmodule

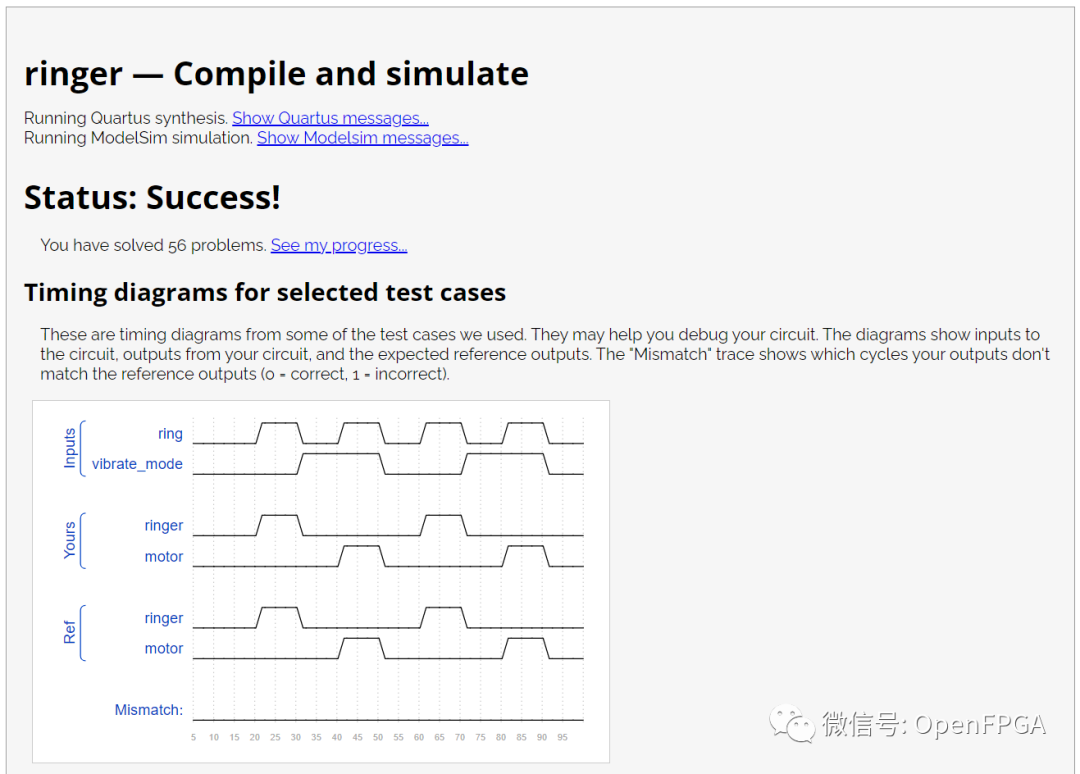

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

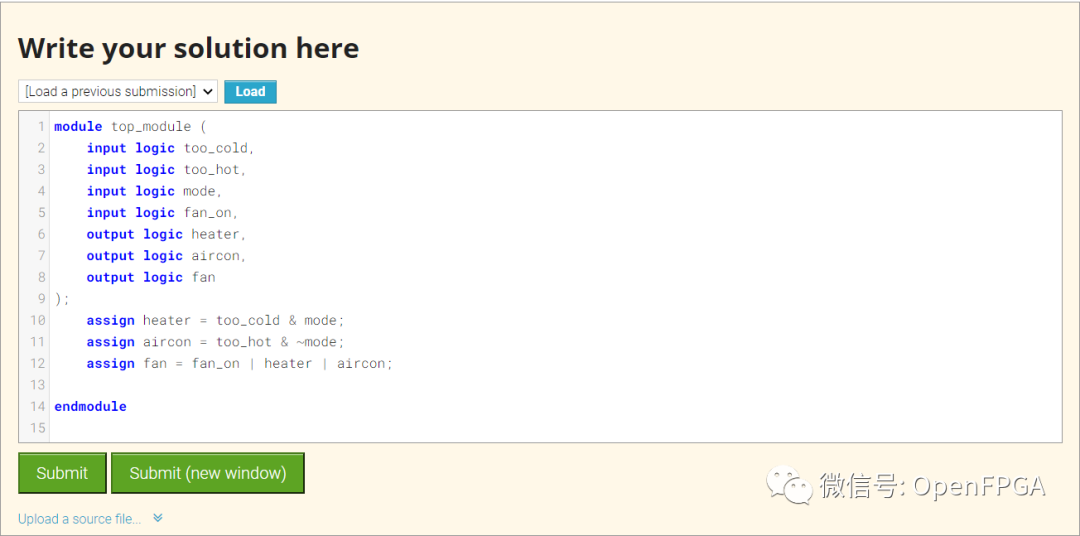

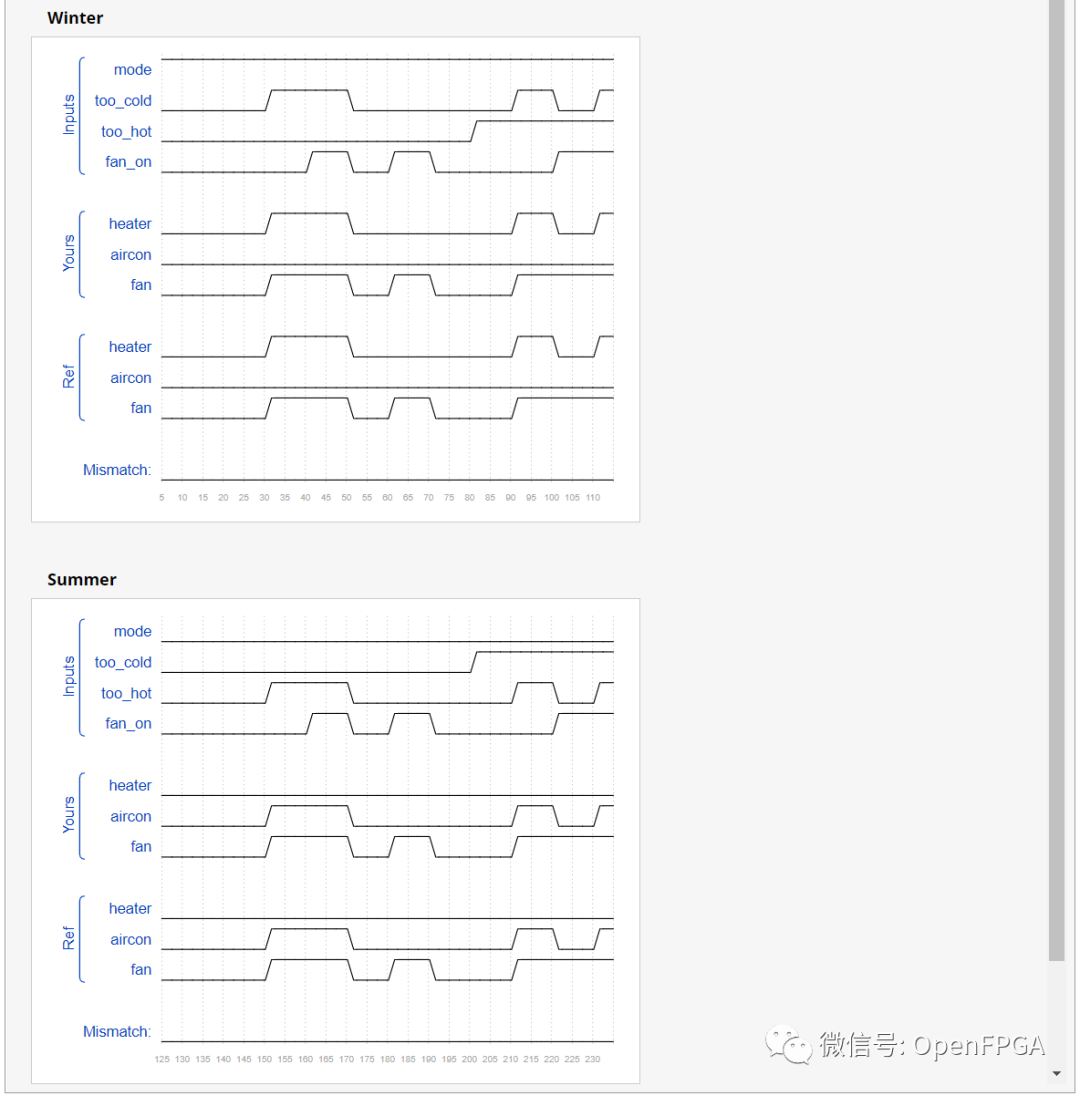

Problem 56-Thermostat

題目說明

一個冷/熱恒溫控制器可以同時在冬季和夏季對溫度進行調節。實現一個可以根據需要打開和關閉加熱器、空調和鼓風機的電路。

恒溫器可以處于以下兩種模式之一:加熱 ( mode = 1) 和冷卻 ( mode = 0)。在制熱模式下,當天氣太冷時打開加熱器(too_cold = 1),但不要使用空調。在制冷模式下,空調過熱時打開空調(too_hot = 1),但不要打開加熱器。當加熱器或空調打開時,還要打開風扇以循環空氣。此外,即使加熱器和空調關閉,用戶也可以請求將風扇打開(fan_on = 1)。

嘗試僅使用assign語句,看看是否可以將問題描述轉換為邏輯電路。

模塊端口聲明

moduletop_module( inputtoo_cold, inputtoo_hot, inputmode, inputfan_on, outputheater, outputaircon, outputfan );

題目解析

這個題目解決方式參考上一題。

moduletop_module( inputlogictoo_cold, inputlogictoo_hot, inputlogicmode, inputlogicfan_on, outputlogicheater, outputlogicaircon, outputlogicfan ); assignheater=too_cold&mode; assignaircon=too_hot&~mode; assignfan=fan_on|heater|aircon; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

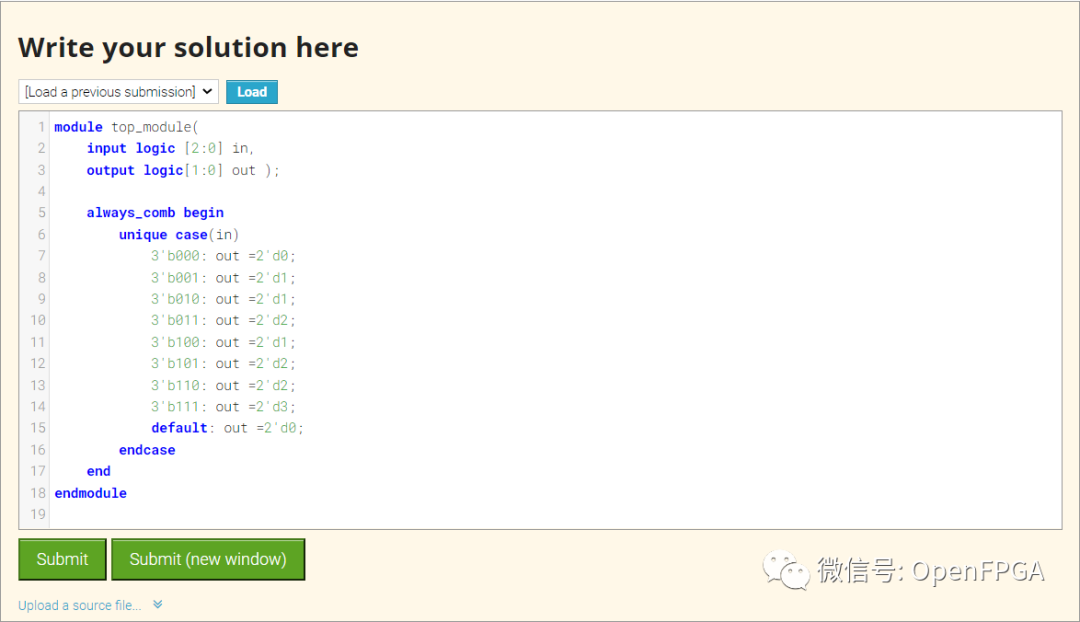

Problem 57-Conditional

題目說明

又是一道計“1”電路。

模塊端口聲明

moduletop_module( input[2:0]in, output[1:0]out);

題目解析

有很多種方式,我們使用組合電路實現,也可以使用for循環。

moduletop_module( inputlogic[2:0]in, outputlogic[1:0]out); always_combbegin uniquecase(in) 3'b000:out=2'd0; 3'b001:out=2'd1; 3'b010:out=2'd1; 3'b011:out=2'd2; 3'b100:out=2'd1; 3'b101:out=2'd2; 3'b110:out=2'd2; 3'b111:out=2'd3; default:out=2'd0; endcase end endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

PS:FOR循環

moduletop_module( input[2:0]in, output[1:0]out); always@(*) begin out=2'b00; for(integeri=0;i<3;?i++) ????????????????begin ????????????????????if(in[i]?==?1'b1) ????????????????????????out?=?out?+?1'b1; ????????????????end ????????end endmodule

這一題就結束了。

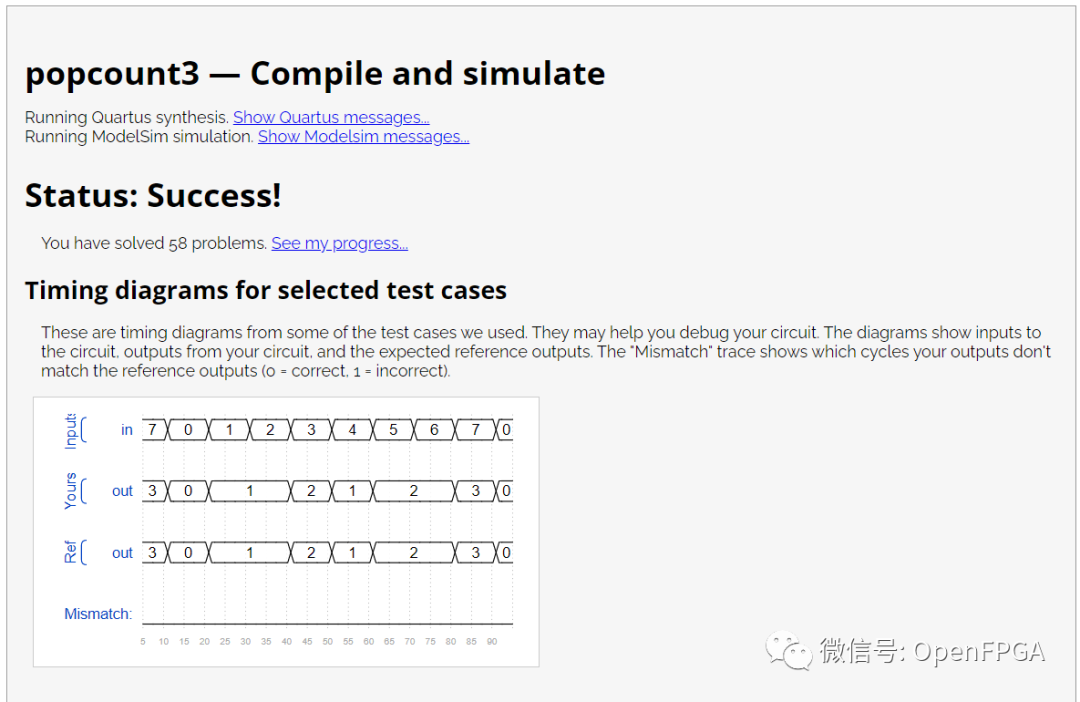

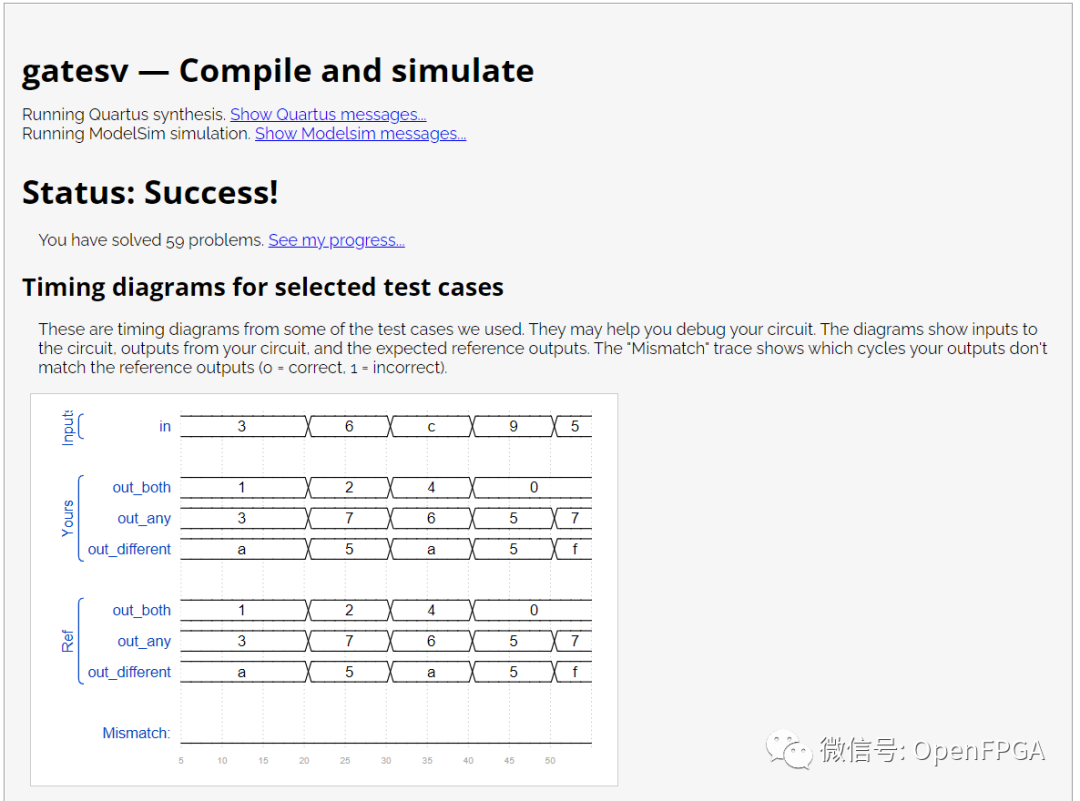

Problem 58-Gatesv

題目說明

在給定一個四位輸入向量[3:0]。我們想知道每個位與其相鄰的位之間的一些關系:

out_both:此輸出向量的每個位指示相應的輸入位及其左側的“鄰居”(較高的索引)是否都是“1” 。例如,out_both[2]表明in[2]和in[3]是否都為 1。由于in[3]左邊沒有“鄰居”,所以我們不需要知道out_both[3] .

out_any:此輸出向量的每個位指示相應的輸入位及其右側的“鄰居”是否為“1”。例如,out_any[2]指示in[2]或in[1]是否為 1。由于in[0]右側沒有鄰居,因此我們不需要知道out_any[0] .

out_different:此輸出向量的每個位指示相應的輸入位是否與其左側的“鄰居”不同。例如,out_diff[2]指示in[2]是否與in[3]不同。對于這部分,將向量視為環繞,因此in[3]左側的鄰居是in[0]。

模塊端口聲明

moduletop_module( input[3:0]in, output[2:0]out_both, output[3:1]out_any, output[3:0]out_different);

題目解析

這個題目重點理解這個相同或者不同之間的邏輯關系(就是與或非這三種關系,仔細思考,就沒什么問題了)。

moduletop_module( inputlogic[3:0]in, outputlogic[2:0]out_both, outputlogic[3:1]out_any, outputlogic[3:0]out_different); assignout_both[0]=in[1]&in[0]; assignout_both[1]=in[2]&in[1]; assignout_both[2]=in[3]&in[2]; assignout_any[1]=in[1]|in[0]; assignout_any[2]=in[2]|in[1]; assignout_any[3]=in[3]|in[2]; assignout_different[0]=in[1]^in[0]; assignout_different[1]=in[2]^in[1]; assignout_different[2]=in[3]^in[2]; assignout_different[3]=in[0]^in[3]; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

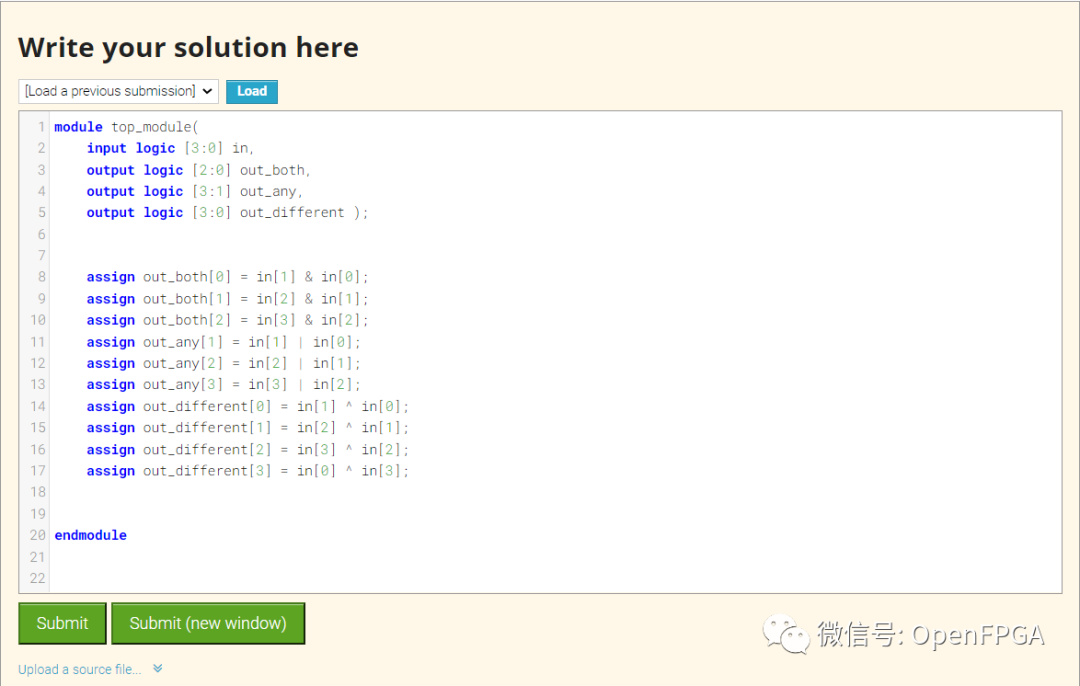

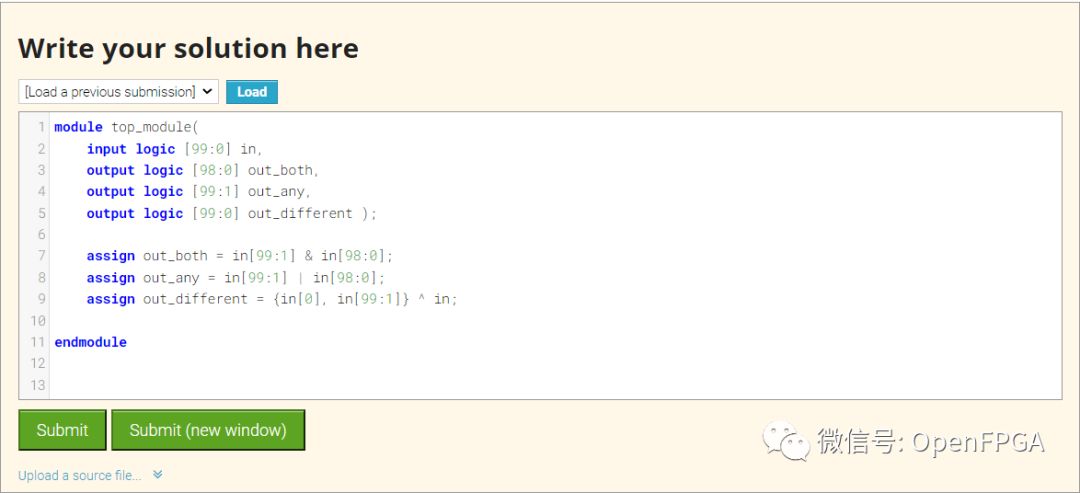

Problem 59-Gatesv100

題目說明

這一條道題和上一題完全相同,只不過輸入向量變成了[99:0],其他說明沒變。

模塊端口聲明

moduletop_module( input[99:0]in, output[98:0]out_both, output[99:1]out_any, output[99:0]out_different);

題目解析

這個題目的解決方式,就不能使用上面那種羅列所有可能情況的解決方式了(太多了),所以我們需要觀察上面那一題的規律來解決問題,這一題最簡單的方式不會超過三行語句,但是難度還是不大。

moduletop_module(

inputlogic[99:0]in,

outputlogic[98:0]out_both,

outputlogic[99:1]out_any,

outputlogic[99:0]out_different);

assignout_both=in[99:1]&in[98:0];

assignout_any=in[99:1]|in[98:0];

assignout_different={in[0],in[99:1]}^in;

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

總結

今天的幾道題就結束了,整體是從需求設計組合邏輯電路,再從波形圖設計,還有兩道從實際使用角度設計,對于組合電路的設計理解非常有幫助。

最后我這邊做題的代碼也是個人理解使用,有錯誤歡迎大家批評指正,祝大家學習愉快~

代碼鏈接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

審核編輯:湯梓紅

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42658 -

組合電器

+關注

關注

0文章

4瀏覽量

5974 -

Verilog

+關注

關注

28文章

1351瀏覽量

110181

原文標題:HDLBits: 在線學習 SystemVerilog(十)-Problem 43-59

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基本邏輯電路、時序電路、組合電路設計

基本邏輯電路、時序電路、組合電路設計

評論