前言

很多設計者都知道晶體振蕩器都是基于皮爾斯振蕩器,但不是所有人都知道具體是如何工作的,只有一部分人能掌握具體如何設計。在實踐中,對振蕩器設計的關注有限,直到發現它不能正常運行(通常是在最終產品已經在生產時),這會導致項目延遲。

振蕩器必須在設計階段,即在轉向制造之前,得到適當的關注,以避免產品在應用中失敗的噩夢場景。

本文介紹了皮爾斯振蕩器的基礎知識,并為其設計提供了指導方針。

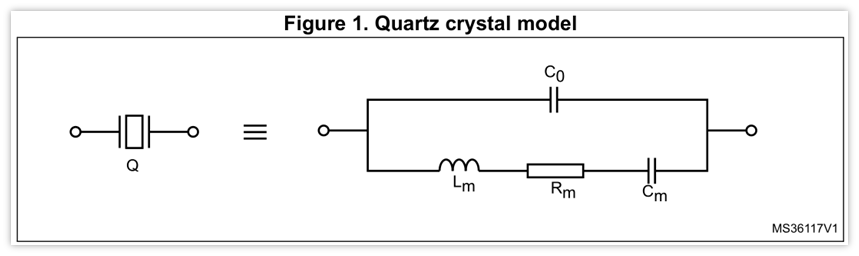

1、石英晶體的特性及模型

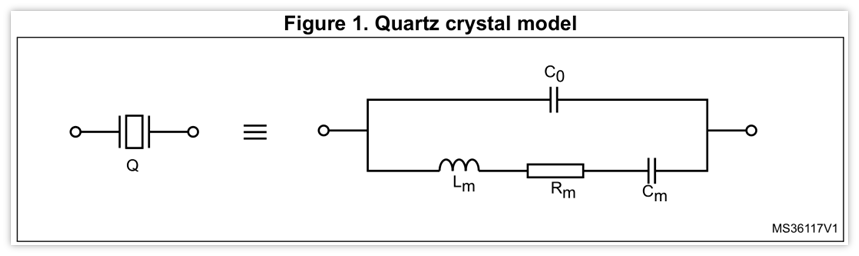

石英晶體可以將電能轉化為機械能的東西,也可以將機械能轉化為電能。這種轉化主要發生在諧振頻率上。石英晶體的等效模型可以用Figure1來表示:

C0并聯電容:兩個電極間形成的電容。

Lm動態等效電感:代表機型振動的慣性。

Cm動態等效電容:代表晶振的彈性。

Rm動態等效電阻:代表電路的損耗。

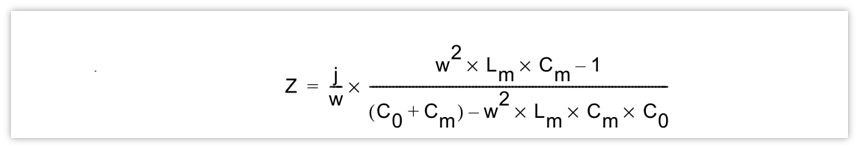

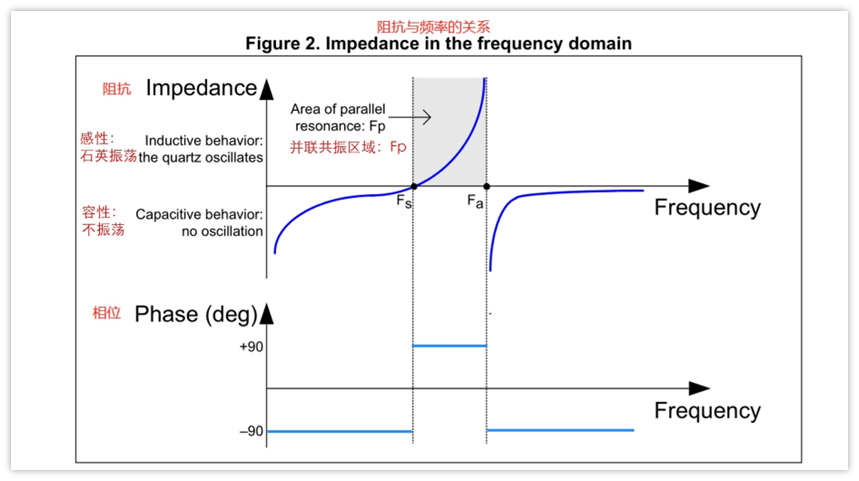

晶振的阻抗表達式如下(假設Rm可以忽略不記):

下圖Figure 2說明了晶振的阻抗與頻率的關系

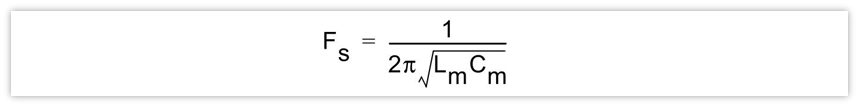

其中Fs是當Z=0時的串聯諧振頻率,其表達式如下:

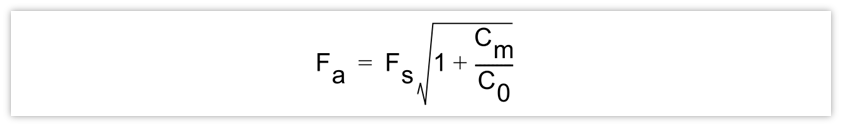

Fa是當電抗Z趨于無窮大時的并聯諧振頻率,假如Fs為已知量,那么其表達式如下:

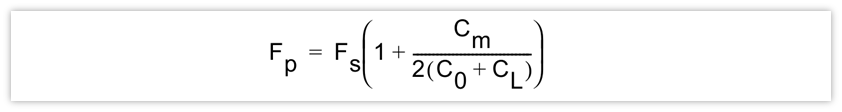

fs和fa之間的區域(圖2中的陰影區域)是并聯諧振的區域。在這一區域晶振工作在并聯諧振狀態,并且在此區域晶振呈電感特性,從而帶來了相當于180 °的相移。具體諧振頻率FP(可理解為晶振實際工作的頻率)表達式如下:

根據這個方程,可以通過改變負載電容CL來調整晶體的振蕩頻率。這就是為什么,在晶體規格書中,晶體制造商指出了使晶體在標稱頻率下振蕩所需的確切CL。

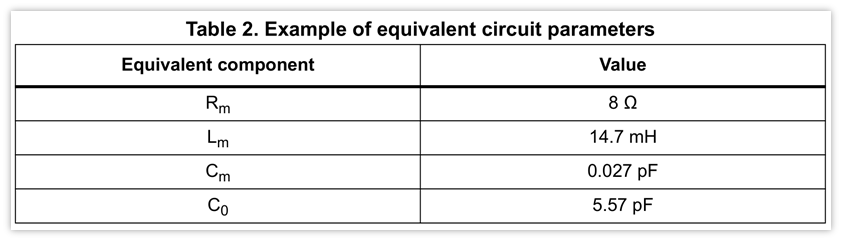

下面Table2給出了一個8Mhz標稱頻率的等效晶體電路元件值的示例:

使用前面的3個公式,可以計算出Fs和Fa:

Fs=7988768Hz

Fa=8008102Hz

如果負載電容CL=10pF,則其振蕩頻率為:FP = 7995695Hz。要使其達到準確的標稱振蕩頻率8MHz,CL應該為4.02pF。

2、振蕩器的原理

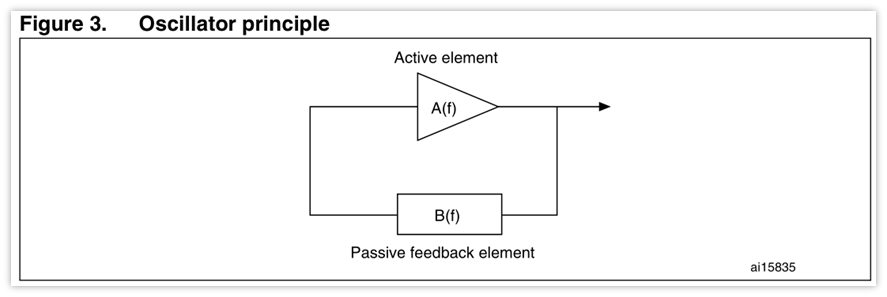

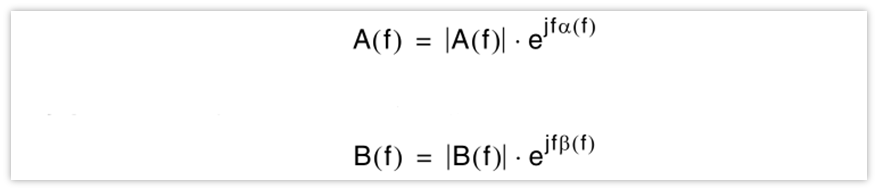

振蕩器由一個放大器和反饋網絡組成,反饋網絡起到頻率選擇的作用。Figure 3通過一個框圖來說明振蕩器的基本原理。

Figure 3振蕩器的基本原理

上圖中:

A(f)是放大器部分,給這個閉環系統提供能量以保持其振蕩。

B(f)是反饋網絡,它決定了振蕩器的頻率。

為了起振,以下的巴克毫森準則必須得到滿足。即閉環增益應大于1,并且總相移為360°。

振蕩需要初始能量才能啟動。通電瞬變和噪聲可以提供所需的能量。然而,能量需要足夠高才能在所需的頻率下觸發振蕩。

為了讓振蕩器穩定工作,實際A(f)*B(f)>>1,這意味著開環增益應該遠遠高于1。振蕩達到穩定狀態所需的時間取決于開環增益。

僅僅滿足振蕩條件也不足以解釋晶振為什么起振。實際過程是,在這種條件下的放大器是非常不穩定的,任何干擾進入這種正反饋閉環系統都會使其不穩定并引發振蕩啟動。干擾可能源于上電,晶振熱噪聲等。同時必須注意到,只有在晶振的工作頻率范圍內的噪聲才能被放大,這部分相對于噪聲的全部能量來說只是很小一部分,這也就是為什么晶體振蕩器需要很長時間才能啟動的原因。

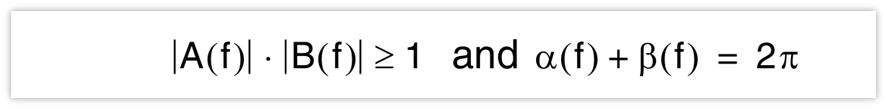

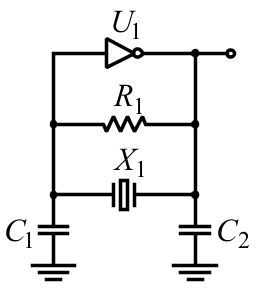

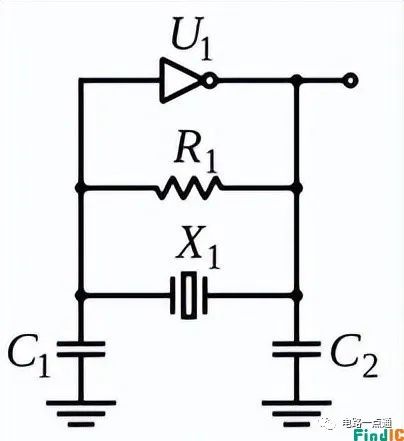

3、皮爾斯晶體振蕩器

皮爾斯晶體振蕩器有低功耗、低成本及良好的穩定性等特點,因此常見于應用中。

Inv:內部反相放大器。

Q:石英或陶瓷晶振。

RF:內部反饋電阻。

RExt:外部限流電阻,限制反相器輸出電流。

CL1和CL2:兩個外部負載電容。

Cs:寄生電容:PCB布線,OSC_IN和OSC_OUT管腳之間的效雜散電容

4、皮爾斯晶體振蕩器設計

本節講了不同的參數,以及如何確定它們的值,以便更好的進行皮爾斯振蕩器的設計。

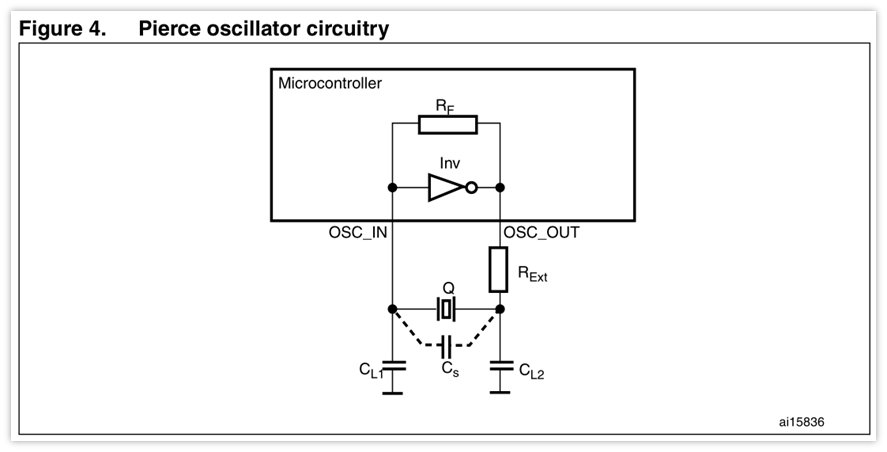

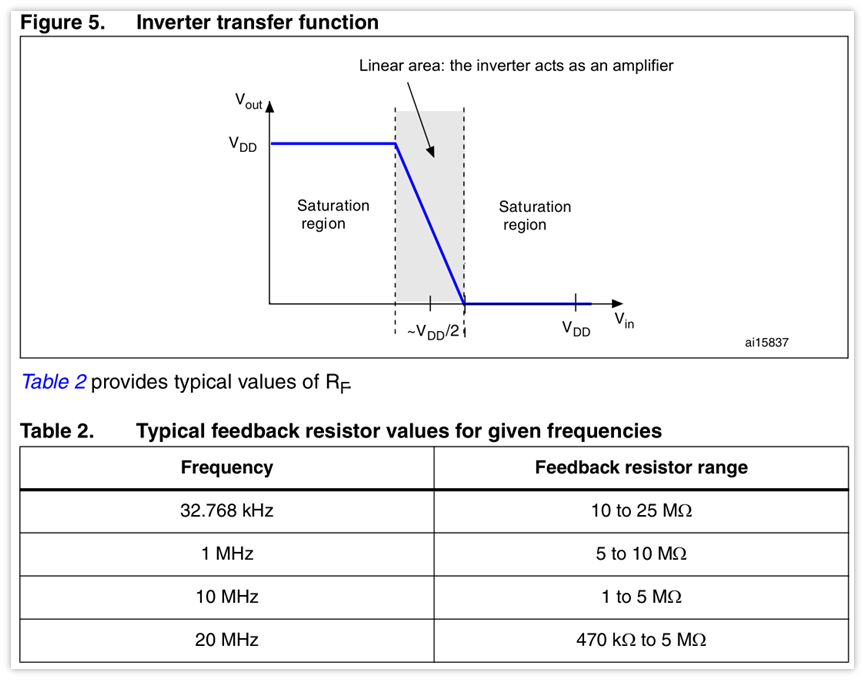

1、反饋電阻RF

在幾乎所有的ST的MCU中,RF是內嵌在芯片內的。它的作用是讓反相器作為一個放大器來工作。

Vin和Vout之間增加的反饋電阻使放大器在Vout= Vin時產生偏置,迫使反向器工作在線性區域(圖5中陰影區)。該放大器放大了晶振的正常工作區域內(Fs與Fa之間)的噪聲(例如晶振的熱噪聲),該噪聲從而引發晶振起振。在某些情況下,起振后去掉反饋電阻RF,振蕩器仍可以繼續正常工作。

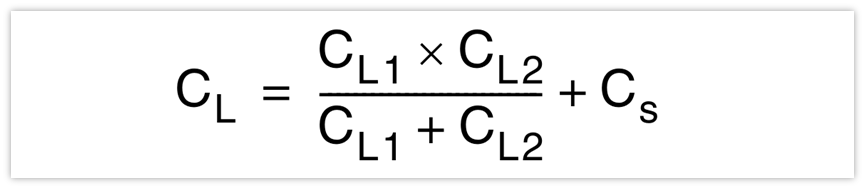

2、負載電容CL

負載電容CL是指連接到晶振上的終端電容。CL值取決于外部電容器CL1和CL2,雜散電容Cs。CL值由由晶振制造商給出。

振蕩頻率精度,主要取決于振蕩電路的實際負載電容與晶振制造商給出的CL值是否相同。振蕩頻率是否穩定則主要取決于負載電容值是否保持穩定不變。

調整外部電容器CL1和CL2,使振蕩電路實際的負載電容等于晶振制造商標定的負載值CL參數(晶振規格書一般會提供),可以獲得標定的振蕩頻率。

計算公式如下:

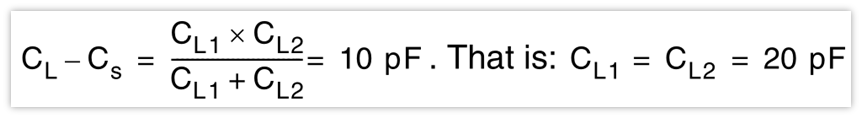

舉個計算的示例:

如果晶振規格書手冊中CL =15pF,并假定Cs = 5pF,則匹配電容CL1,CL2有:

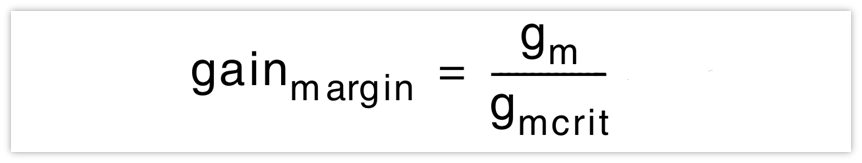

3、振蕩器的增益裕量

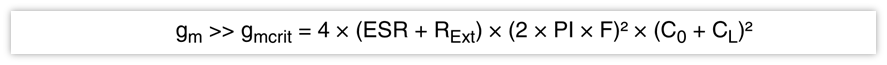

增益裕量是最重要的參數,它決定振蕩器是否能夠正常起振,其表達式如下:

其中:

a、gm是反相器的跨導(高頻時單位是mA/V,低頻時是μA/V,比如32Khz)。

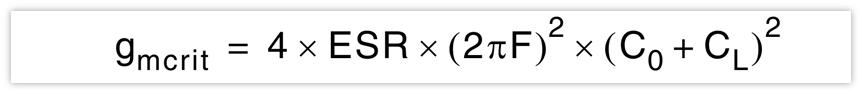

b、gmcrit (gm critical)的值取決于晶體參數。

假定CL1 = CL2,并假定電路實際的CL與制造商給定的CL值相同,則gmcrit表達式如下(其中ESR是指晶振的等效串聯電阻):

根據Eric Vittoz理論:晶體等效電路的阻抗由放大器和兩個外部電容的阻抗來補償。

為了滿足這個理論,gm必須滿足gm>gmcrit, 在這種情況下才滿足起振的振蕩條件。為保證可靠的起振,增益裕量gainmargin的最小值一般設為5。

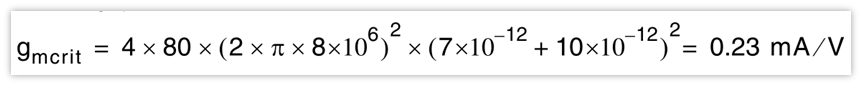

舉個例子,設計一個微控制器的振蕩器部分,其gm等于25mA/V。如果所選擇的石英晶振的參數如下:

頻率= 8MHz,C0 = 7pF,CL = 10pF,ESR = 80 Ω。那么該晶體能否與微控制器配合起振?

計算gmcrit:

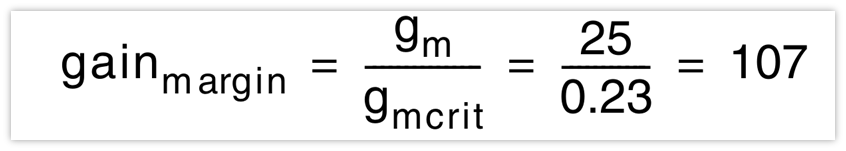

進一步計算增益裕量:

此增益裕量遠大于起振條件,即gainmargin>5,晶振將正常起振。

如果不能滿足增益裕量起振條件(即增益裕量gainmargin小于5),晶振無法正常起振,應嘗試選擇一種ESR較低,CL較低的晶振。

4、驅動功率DL和外部串阻Rext計算

驅動功率DL和串聯電阻Rext這兩個參數是相互聯系的,這也就是為什么在同一節中描述此二者的原因。

a、驅動功率DL的計算

驅動功率描述了晶振的功耗。晶振的功耗必須受到限制,否則石英晶體可能會由于過度的機械振動而導致不能正常工作。通常由晶振制造商給出晶振驅動功率的最大值,單位通常是毫瓦。超過這個值時,晶振可能就會損壞。

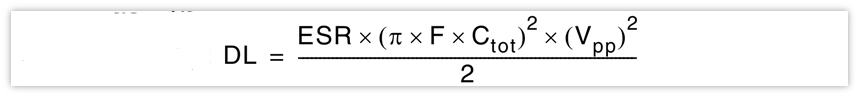

晶振的驅動功率DL滿足下面公式:

其中:

ESR:是指晶振的等效串聯電阻(其值由晶振制造商提供的晶振規格書手冊給出):

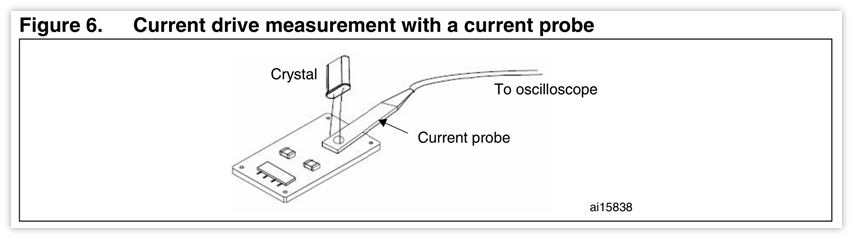

IQ:是流過晶振電流的有效值,使用示波器可觀測到其波形為正弦波。電流值可使用峰-峰值(IPP)。當使用電流探頭時(如Figure6),示波器的量程比例可能需要設置為1mA/1mV。

如前面描述,當使用電位器調整電流值,可使流過晶振的電流不超過最大電流有效值IQmaxrms(假設流過晶振的電流波形為正弦波)。

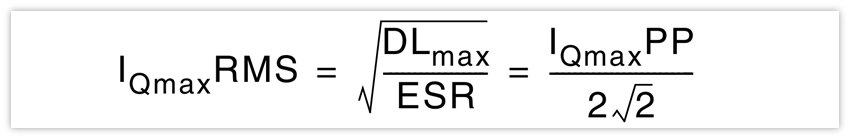

最大電流有效值IQmaxrms表達式如下:

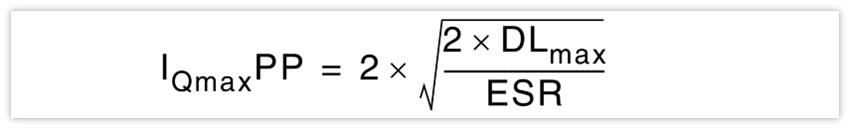

因此,流過晶振的電流峰峰值IPP(可從示波器讀到)不應超過IQmaxPP,IQmaxPP表達式如下:

這也就是為什么需要外部電阻Rext的原因。當IQ超過IQmaxPP時,Rext是必需的,并且RExt要加入到ESR中去參與計算IQmax。

b、另外一個測量驅動功率DL的方法

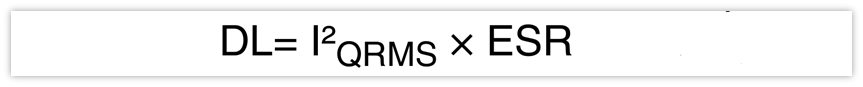

驅動功率可以由下式計算得出:

其中IQrms是交流電流的有效值。

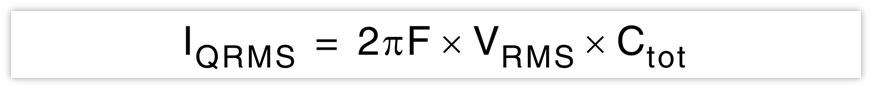

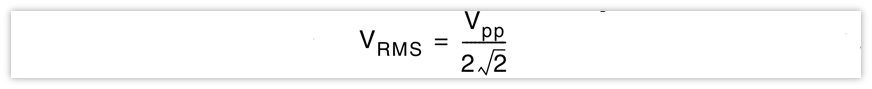

這個電流可以通過使用小電容(<1pF)示波器探頭在放大器的輸入端,測量電壓變化得到。相對于流經CL1的電流,放大器的輸入電流可以忽略不計,因此可以假定經過晶振的電流等于流經CL1的電流。這樣,電壓的有效值與電流的有效值有如下關系:

其中:

Vpp指的是測量的CL1兩端電壓的峰峰值。

Ctot = CL1 + (CS/2) + Cprobe

CL1:是放大器輸入端的外部電容

CS:是寄生電容

Cprobe:是示波器探頭的電容

這樣,最終驅動功率DL可以由下式子得出:

DL的測量值一定不能超過由晶體廠家提供的手冊中的DL數值。

c、外部串聯電阻Rext的計算

這個電阻的作用是限制晶振的功率,并且它與CL2組成一個低通濾波器,以確保振蕩器的起振點在基頻上,而不是在其他高次諧波頻率點上(避免3次,5次,7次諧波頻率)。

如果晶振的功耗超過晶振制造商的給定值,外部電阻Rext是必需的,用以避免晶振被過分驅動。如果晶振的功耗小于晶振制造商的給定值,就不推薦使用Rext了,它的值可以是0Ω。

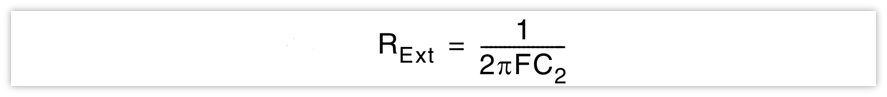

對Rext值的預估可以通過考慮由Rext和CL2構成了一個濾波器,通帶寬度應不小于振蕩器頻率,當振蕩頻率正好等于濾波器截止頻率時,有下面公式:

舉例,當:

振蕩器頻率F = 8MHz

CL2 = 15pF

得到:Rext = 1326Ω

優化RExt值的方法推薦如下:

首先根據前面的介紹確定好CL1和CL2的值,其次使用電位器來代替Rext,Rext值可預設為CL2的阻抗,然后調整電位器的阻值直到它滿足晶振驅動功率要求。

在計算完Rext值后要重新計算gainmargin的值(參考前面內容)以確保Rext值對起振條件沒有影響。Rext值的值需要加入到ESR中參與gmcrit的計算,同時要保證gm >>gmcrit。

如果Rext值太小,晶振上可能會承擔太多的功耗。如果Rext值太大,振蕩器起振條件將得不到滿足從而無法正常工作。

d、啟動時間

啟動時間是指振蕩器啟動并達到穩定所需的時間。石英晶體振蕩器的啟動時間要比陶瓷晶體振蕩器的時間要長。

啟動時間受外部CL1和CL2電容影響,同時它隨著晶振頻率的增加而減少。不同種類的晶振對啟動時間影響也很大,石英晶振的啟動時間比陶瓷晶振的啟動時間長得多。

起振失敗通常和gainmargin有關,過大或過小的CL1和CL2,以及過大的ESR值均可引起gainmargin不能滿足起振條件。

頻率為MHz級的晶振的啟動時間是毫秒級的,而32kHz的晶振的啟動時間一般要1~5秒。

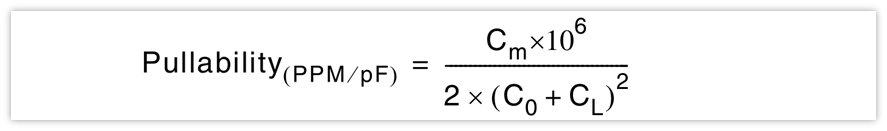

e、晶體牽引度

晶振的牽引度是指工作在正常并聯諧振區的晶振頻率的變化率。這也用于衡量隨負載電容變化而導致的頻率變化,負載電容的減少會導致頻率的增加,反之負載電容的增加會導致頻率的減小。晶振的牽引度表達式如下:

晶振選型及外部器件的簡易指南

本節給出了一個挑選合適的晶振及外部器件的簡易指南,一共可分為3個主要步驟:

1、計算增益裕量gainmargin

首先選擇一個晶振(根據MCU需求及晶振手冊)

然后計算晶振的增益裕量(gainmargin)并檢查其是否大于5:如果gainmargin < 5,說明這不是一個合適的晶振,應當換一個低ESR值或低CL值的晶振,知道滿足大于5的條件。

2、計算外部負載電容

計算CL1和CL2的值(計算方法見前面章節),并檢查標定為該計算值的電容是否能在市場上獲得。

如果能找到容值為計算值的電容,則晶振可以在期望的頻率正常起振。

如果找不到容值為計算值的電容,在對頻率的要求不是特別苛刻時,選擇市場上能獲得的電容中容值距計算值最近的電容,然后轉到第三步。

3、驅動功率及Rext的計算

計算驅動功率DL并檢查其是否大于晶振的DL參數要求DLcrystal:

如果DL < DLcrystal,沒必要使用外部電阻,祝賀你,你找到了合適的晶振。

如果DL > DLcrystal,應該計算Rext使其確保DL< DLcrystal并據此重新計算Gainmargin。如果Gainmargin> 5,祝賀你,你找到了合適的晶振。如果Gainmargin< 5,需要再重新挑選另外一個晶振,然后重新回到第一步。

-

振蕩器

+關注

關注

28文章

3832瀏覽量

139096 -

晶振

+關注

關注

34文章

2866瀏覽量

68039 -

負載電容

+關注

關注

0文章

139瀏覽量

10441

原文標題:一份超級nice的晶振電路設計指南!

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

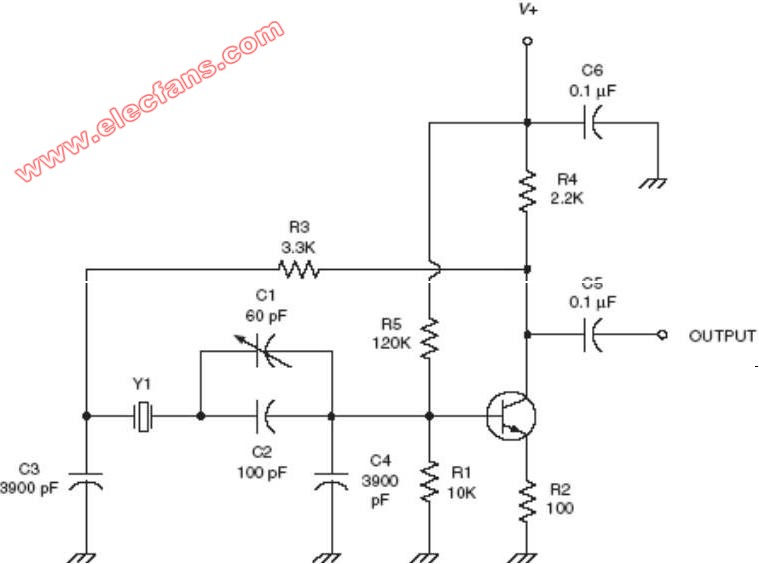

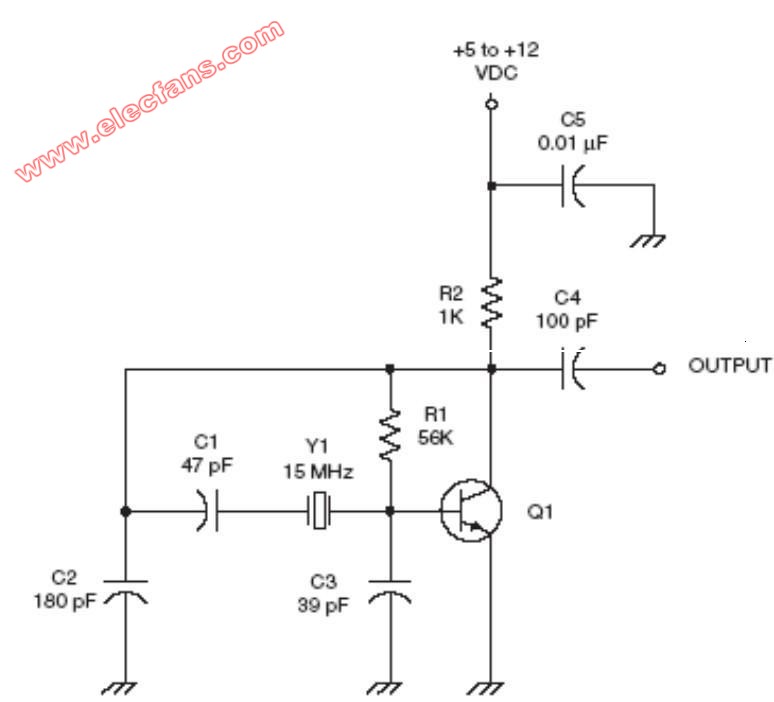

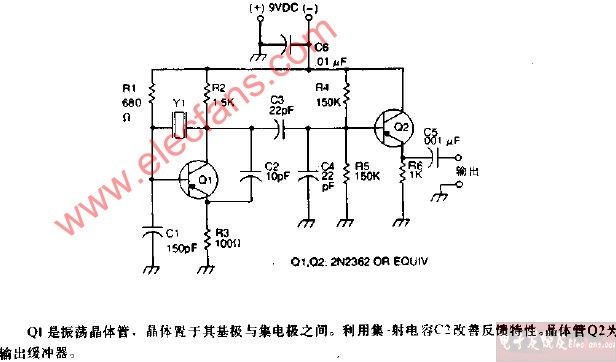

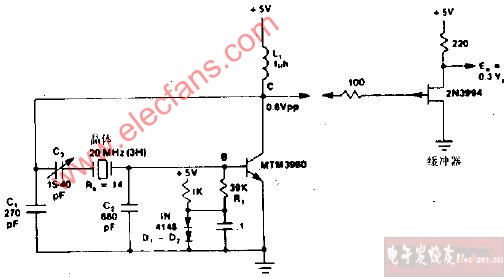

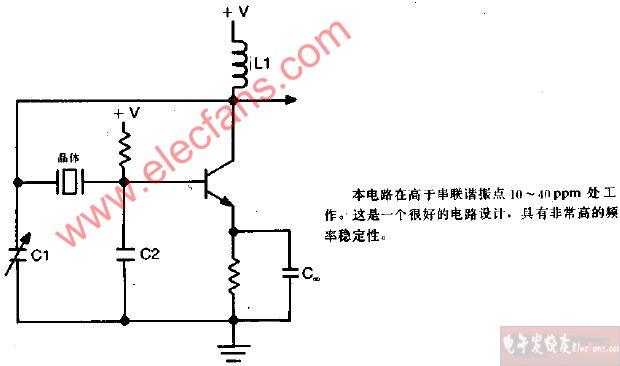

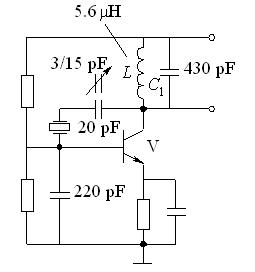

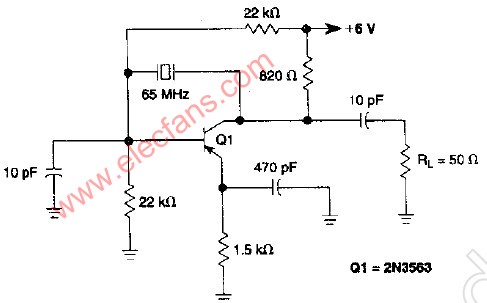

唱片皮爾斯振蕩器射頻電路(LP Pierce oscilla

皮爾斯振蕩器的基礎知識

皮爾斯晶體振蕩器的原理與設計

晶振設計指南:皮爾斯振蕩器的基礎知識

皮爾斯振蕩器的基礎知識

皮爾斯振蕩器的基礎知識

評論