1. 芯片和系統(tǒng)架構的趨勢

近年來,隨著云計算、大數(shù)據(jù)、物聯(lián)網(wǎng)、人工智能等技術的快速發(fā)展和傳統(tǒng)產(chǎn)業(yè)數(shù)字化轉(zhuǎn)型,數(shù)據(jù)量呈現(xiàn)指數(shù)式上升。據(jù)互聯(lián)網(wǎng)數(shù)據(jù)中心(Internet Data Center,簡稱IDC)2018年預測,全球數(shù)據(jù)總量在2020年將達到44個ZB,我國數(shù)據(jù)量將達到8060個EB(1EB=260bit),占全球數(shù)據(jù)總量的18%。但實際上,2020年全球數(shù)據(jù)總量已經(jīng)接近60個ZB,遠遠超過了2018年的預期。2020年初全球暴發(fā)的新冠肺炎疫情,更是促使了數(shù)字經(jīng)濟的快速發(fā)展。

據(jù)中國信通院測算,2020年我國數(shù)字經(jīng)濟規(guī)模達到了39.2萬億元,占GDP的比重達到38.6%。國家“十四五”規(guī)劃中提出“加快數(shù)字化發(fā)展,建設數(shù)字中國”的發(fā)展戰(zhàn)略。數(shù)字技術與實體經(jīng)濟深度融合,賦能傳統(tǒng)產(chǎn)業(yè)的轉(zhuǎn)型升級,顯示出數(shù)字經(jīng)濟在國民經(jīng)濟和社會發(fā)展中的核心地位。數(shù)字經(jīng)濟帶來的數(shù)據(jù)爆發(fā)式發(fā)展必定需要更多的主機板硬件支撐,這也為覆銅板行業(yè)帶來了前所未有的機遇。

1965年英特爾的聯(lián)合創(chuàng)始人戈登·摩爾(Gordon Moore)提出的摩爾定律在過去50年內(nèi)成為半導體行業(yè)遵循的準則,準確預言了集成電路尺寸微縮化對半導體行業(yè)的技術發(fā)展。但摩爾定律是一條經(jīng)濟定律,當實際半導體工藝能力達不到經(jīng)濟效率的時候,投資回報就會越來越低。當2017年半導體工藝節(jié)點進入7nm之后,尺度物理限制使得工藝改進帶來的效益逐漸降低。尤其是在未來2~3nn的工藝節(jié)點上,導線寬度將僅有幾個原子直徑大小。量子力學的不確定原理使得晶體管不再可靠。因此,摩爾定律終將很難維持下去。Intel生產(chǎn)的CPU多年停留在14nm制程,新一代產(chǎn)品也只進行了結構優(yōu)化。Intel一直堅持的IDM模式(Integrated Device Manufacture,即垂直整合制造模式)決定其必須選擇低制程出貨。

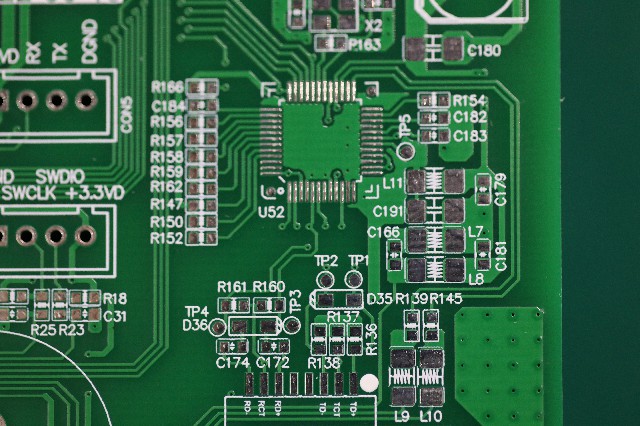

除了半導體工藝的物理極限約束性,信息交互和傳遞的需求也對半導體芯片制程提出了更高要求。從芯片封裝來看,在大芯片和高精尖的制程不符合經(jīng)濟規(guī)律的情況下,封裝就成首先的主攻對象。芯片制造廠家對于3nm之后的制程領域?qū)⒉辉俅罅ν度耄嚓P的應對技術轉(zhuǎn)向了超越摩爾定律的芯片后端架構,包括從傳統(tǒng)2維(2D)芯片到2.5維(2.5D)/3維(3D)芯片、從同質(zhì)集成到異質(zhì)整合等。

系統(tǒng)級芯片(System on Chip, SoC)與系統(tǒng)級封裝(System in Package, SiP)是實現(xiàn)芯片向更高性能、更低成本發(fā)展的方式,其中以三維(3D)堆疊技術為代表的先進封裝技術成為后摩爾時代的核心驅(qū)動力之一。2.5D封裝是在Interposer上并排互連芯片,而3D互連層是將芯片進行堆疊,即互連結構在彼此的頂部。

無論是業(yè)界的設計者還是晶圓廠都在大力發(fā)展2.5D/3D封裝的相關技術。目前高端CPU、AI、GPU等高端芯片的封裝成本已經(jīng)超過硅片(die)的成本,芯片和封裝的性能提升帶來巨大的成本壓力,工程師們的研發(fā)重點越來越趨向于PCB材料和設計。另外一種趨向就是用SiP類小系統(tǒng),介于封裝和PCB之間來兼顧各方面的優(yōu)缺點,但封裝基板的成本較高。

所以,當目前系統(tǒng)性能的提升不能再依靠芯片制程的時候,封裝、PCB等后端工藝和設計就變得越來越重要。從這個角度上分析,芯片、封裝和系統(tǒng)的未來需求對覆銅板或者IC基板行業(yè)帶來了前所未有的機遇!

2. ICT系統(tǒng)功耗對覆銅板的影響

信息與通信技術(Information and Communications Technology,ICT)是信息技術和通信技術相融合而形成的一個新的技術領域。以智能手機為核心的消費電子和以大數(shù)據(jù)云計算為核心的高性能計算機成為驅(qū)動ICT系統(tǒng)電子制造技術的主要來源。ICT系統(tǒng)為覆銅板、PCB產(chǎn)業(yè)發(fā)展帶來機遇的同時,也帶來了很多挑戰(zhàn)。首先是針對芯片間、芯片和封裝體間的微電子封裝技術,即互連技術。互連技術中的PCB對于ICT系統(tǒng)的影響主要體現(xiàn)在供電互連和信號傳輸。

互連技術工藝設計需要考慮到單芯片或者多芯片之間的布線、與PCB節(jié)距的匹配、封裝體的散熱等情況。隨著半導體工藝的進步,芯片內(nèi)的電路密度成倍提高,并且以較高頻率運行,且片上連線越來越細,片上供電網(wǎng)絡必須將更多的電力以更少的連線資源送至每個單元,保證芯片的穩(wěn)定性和預定工作頻率。

芯片元件的供電通過PCB傳送。由于電路功耗器件的存在,因此必定產(chǎn)生功耗損失和溫度升高。IR壓降和供電網(wǎng)絡消耗的大量布線資源成為困擾后端設計者的重要問題。目前大芯片的功耗可達到900W,有的接近于1000W。僅在PCB上的功耗損失會高達500W!

數(shù)據(jù)顯示,2018年全國數(shù)據(jù)中心總耗電量1500億千瓦時,占社會總用電量的2%。預計到2025年,這一占比將增加一倍達到4.05%。電費成為能耗大戶“數(shù)據(jù)中心”的最大運行成本,約占整體運行成本的70%。而從電源到芯片的供電過程中,PCB或者覆銅板就浪費掉整個功耗的70%。

雖然工程師們通過將電源和芯片靠得更近、增加PCB的銅厚、增加供電層數(shù),以及包括PCB設計優(yōu)化等方案來降低浪費功耗,但都不能從根本上解決此問題。所以如何實現(xiàn)芯片的供電是一個大學問,對PCB的性能要求也越來越高。

電源模塊封裝最終決定了ICT系統(tǒng)的功率及電流密度。隨著系統(tǒng)變得越來越密集和功率元件更接近負載點,散熱問題成為嚴重問題。沒有封裝技術的根本性進展,功率密度和散熱密度就無法繼續(xù)提升。Vicor率先推出功率元件封裝平臺—轉(zhuǎn)換器級封裝(Converter housed in Package,簡稱ChiP),可以實現(xiàn)更小、更靈活的元件尺寸,簡化設計流程,并顯著降低了能源成本。

合封電源是一項支持耗電極高的人工智能處理器和48V自動駕駛系統(tǒng)的關鍵技術。Vicor合封電源系統(tǒng)提供高達1000A的峰值電流。合封電源不僅可消除“最后一英寸”問題,為處理器高效供電,而且還可通過支持48V輸入實現(xiàn)為整個機架的處理器高效供電[8]。

在ChiP封裝的應用中,PCB銅箔電源層的配電損耗已成為一個占主導地位的損耗項,并制約性能。電源模塊最大限度降低阻抗的最佳位置是直接位于處理器下方,并將電源模塊的輸出功率引腳與上面處理器的電源引腳陣列精確匹配。但這也是儲能所需大量旁路電容器的最佳位置,以滿足瞬態(tài)處理器的電源需求,從而會造成PCB布局沖突。

垂直供電(VPD)的難題已經(jīng)使用多層堆疊技術解決。實現(xiàn)高密度三維集成的主要手段包括:多功能芯片、多功能基板、立體組裝和三維板間垂直互連等。此外,在功耗不變情況下,提升電壓則電流下降。目前Intel和AMD已經(jīng)采用此技術,即在功耗不變的情況下,提升電壓來降低電流。在PCB上用高壓,在芯片里面再將高壓轉(zhuǎn)成低壓。通過這種方式,電路上的功率損耗就小了。但這種架構對于覆銅板行業(yè)來說是一個挑戰(zhàn)。因為所采用PCB的層數(shù)顯著下降,覆銅板使用量有所減少。

高密系統(tǒng)是ICT的趨勢,但大量的無源器件無法實現(xiàn)主板小型化。采用無源器件內(nèi)置技術后,被動器件(如:電阻、電容)將會被集成在PCB內(nèi)部,而外部不會留下任何無源器件,這樣PCB的空間和尺寸會被壓縮至最小!

隨著SiP封裝技術的不斷發(fā)展,越來越多的元器件被埋入IC載板。越來越多的科技工作者認為,直接將IC等主動元件和其他被動元件在PCB大拼板加工過程中直接埋入,將大大縮短整個電子制造產(chǎn)業(yè)鏈。所以如果覆銅板PCB能集成更多的電容、電感、電阻,這個將會給行業(yè)帶了很大的優(yōu)勢,同時也是覆銅板廠商的機遇。

電源模塊是指可以直接裝置在PCB上的電源供給器,這類電源稱為使用點電源供給系統(tǒng)或負載點電源供給系統(tǒng)。由于該類電源模塊優(yōu)點較多,因此廣泛應用于設備交換、電信通訊、光電傳輸以及路由器等各大領域。

3. ICT高速對覆銅板的影響

互連技術中的PCB對于ICT系統(tǒng)的影響還表現(xiàn)在信號的無損傳輸上。信號損失表現(xiàn)在從發(fā)射端到接收端的信號能量丟失。能量丟失越多,誤碼率越高。而損失最大的是PCB傳輸線部分。近年來新發(fā)展起來的光、電纜、無線射頻等技術或許取代傳統(tǒng)的高速PCB傳輸線,這些都直接取代用PCB蝕刻的傳輸線來傳輸信號的方法,對CCL和PCB廠商來說是一個很大的挑戰(zhàn)。

在不改變傳統(tǒng)架構基礎上,就需要將覆銅板做得性能很好、成本很低。比如@16GHz,根據(jù)仿真和測試的數(shù)據(jù)來看,low etch技術因為其優(yōu)質(zhì)的低損耗性能,使得端到端的整個鏈路功耗降低12%。在高頻化的PCB和CCL中信號的傳送是沿著銅箔的輪廓曲線進行傳輸?shù)模鋫魉途嚯x與表面粗糙度(Rz)的大小密切相關。

當銅箔的輪廓大時,由信號傳送的距離增長,而造成信號傳送速度的減慢,并傳送損失也增加。因此減少傳輸路徑和減少表面銅瘤是緩解趨膚效應的有效手段。但銅箔與樹脂間的高抗剝離強度要求銅箔表面具有合適的銅瘤結構。因此,對銅箔進行適當?shù)谋砻嫣幚韺τ诟层~板行業(yè)來說也至關重要。

ICT系統(tǒng)間的信號傳輸速度不是由一條線的速度決定,而是取決于整個帶寬。帶寬由信號傳輸速度和互連線密度決定。類似于高速公路,單通道的速度起不來,但可以修多條通道,那么整個道路的汽車流通量就大了。所以高速信號傳輸系統(tǒng)在討論速度的時候,通常考慮布線密度。

為了實現(xiàn)這個目的,人們就必須在PCB上實現(xiàn)高密布線。高密布線要求CCL、PCB和IC載板制造工藝的同步提升。由于傳統(tǒng)蝕刻不能保證很小的線距和線寬,所以一種新的方法被提出來。即先拉好銅絲,或者其他更好的金屬絲,再埋在PP片上,直接壓合成“帶線”的微波形態(tài)。這樣在增加密度的同時,可以提升損耗和工差。極小的工程誤差帶來巨大的設計裕量,具有很大的性能提升能力。H公司等正在開發(fā)量產(chǎn)能力。這個對于PCB和覆銅板行業(yè)來說是一個很好提升的機會。

4. 小結

ICT系統(tǒng)互連架構持續(xù)發(fā)展帶給覆銅板、PCB、IC載板很大的挑戰(zhàn)和很多的機遇。一個很大的特點是PCB中一些電的功能有移向封裝和硅片的趨向,減少了PCB的重要性,這個對于覆銅板行業(yè)來說是一個很大的挑戰(zhàn)。覆銅板和PCB行業(yè)需加大力度投入研發(fā),以保持其對于ICT產(chǎn)業(yè)的作用和貢獻。

審核編輯:郭婷

-

云計算

+關注

關注

39文章

7848瀏覽量

137636 -

物聯(lián)網(wǎng)

+關注

關注

2911文章

44849瀏覽量

375363 -

大數(shù)據(jù)

+關注

關注

64文章

8902瀏覽量

137599

原文標題:【學習園地】集成電路和ICT互連架構演變帶給覆銅板行業(yè)的機遇與挑戰(zhàn)

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

產(chǎn)業(yè)"內(nèi)卷化"下磁性元件面臨的機遇與挑戰(zhàn)

芯片和封裝級互連技術的最新進展

智能駕駛的挑戰(zhàn)與機遇

TE推出AMPMODU互連系統(tǒng)產(chǎn)品特色是什么?-赫聯(lián)電子

國產(chǎn)光電耦合器2024年的機遇與挑戰(zhàn)

5G時代下,無機填料氧化鋁導熱粉在覆銅板市場的發(fā)展趨勢與重要性

設計制作PCB覆銅板的五種種常見方法

中軟國際攜手華海智匯共同探索智慧ICT市場新機遇

國產(chǎn)光耦2024:發(fā)展機遇與挑戰(zhàn)全面解析

國產(chǎn)光電耦合器:2024年蓬勃發(fā)展的機遇與挑戰(zhàn)

ICT系統(tǒng)互連架構帶給覆銅板行業(yè)的挑戰(zhàn)與機遇

ICT系統(tǒng)互連架構帶給覆銅板行業(yè)的挑戰(zhàn)與機遇

評論