D觸發器也稱為“延遲觸發器”或“數據觸發器”,主要用于存儲1位二進制數據,是數字電子產品中廣泛使用的觸發器之一。除了作為數字系統中的基本存儲元件外,D觸發器也被視為延遲線元件和零階保持元件。

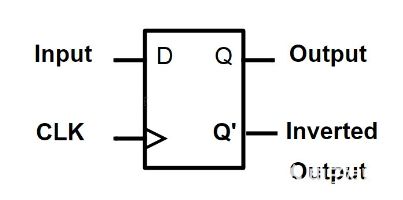

D觸發器有兩個輸入,一個時鐘(CLK)輸入和一個數據(D)輸入。此外,D觸發器也有兩個輸出,一個是用Q表示的主輸出,另一個是用Q'表示的Q的補碼。D觸發器的符號如下所示:

結構特點

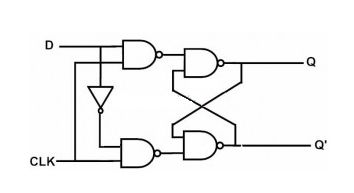

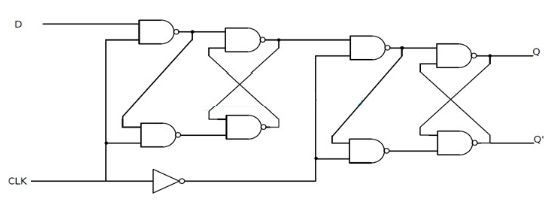

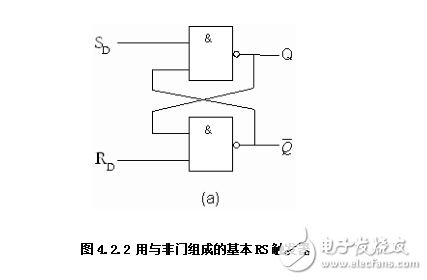

D觸發器是通過修改SR觸發器來構造的。其中,S輸入由D輸入給出,R輸入由反相D輸入給出。因此,D觸發器類似于SR觸發器,其中兩個輸入相互補充,所以不會出現任何中間狀態。SR觸發器的主要缺點是在D觸發器中消除了競態條件(由于反相輸入)。D觸發器的電路圖如下圖所示:

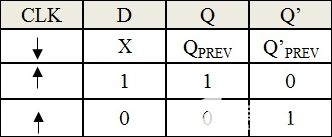

當不向D觸發器施加任何時鐘輸入或在時鐘信號的負邊沿(下降沿)期間,輸出不會發生變化。它將在輸出Q處保留其先前的值。如果時鐘信號為高電平(更準確地說是上升沿/正邊沿)并且如果D輸入為高電平,則輸出也為高電平,如果D輸入為低電平,則輸出將變為低的。因此,在存在時鐘信號的情況下,輸出Q跟隨輸入D,其真值表如下:

簡單地說,對于時鐘信號的正向轉換:

如果D = 0 => Q = 0,則觸發器復位。

如果D = 1 => Q = 1,則觸發器置位。

注意: ↑ 表示時鐘的正邊沿,↓ 表示時鐘信號的負邊沿。

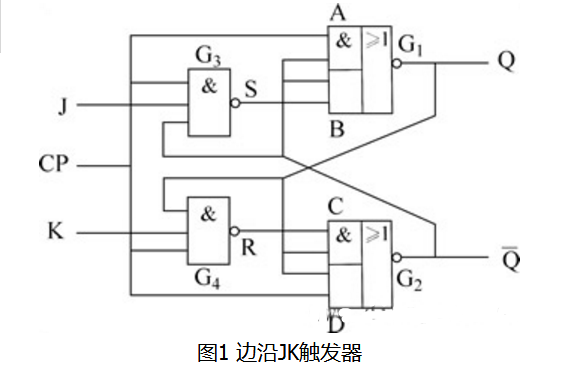

邊沿觸發D觸發器

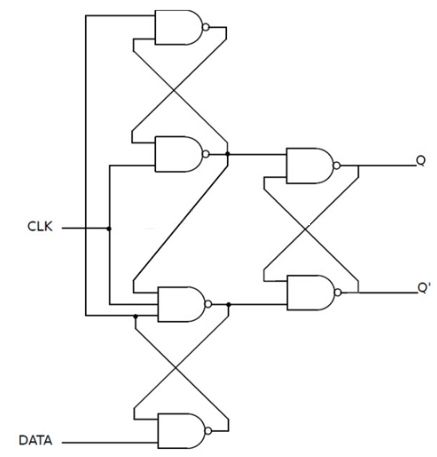

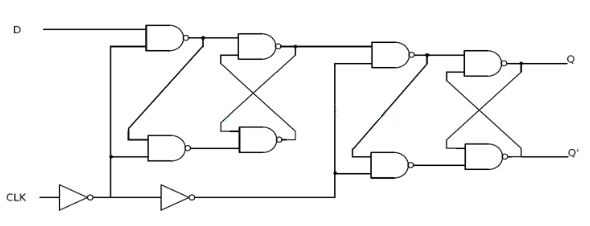

正邊沿觸發的D觸發器由三個SR NAND鎖存器構成。輸入級由兩個鎖存器組成,輸出級由一個鎖存器組成。在輸入級,數據輸入連接到其中的一個NAND鎖存器,時鐘信號 (CLK) 并行連接到兩個SR鎖存器。

當時鐘信號為低時,輸入級的輸出為高邏輯,而與數據輸入上的值無關。因此,它存儲的先前數據。當時鐘經過正向轉換(從低到高)時,輸入級的輸出負責最終輸出的設置或復位操作,并取決于數據信號。

如果數據輸入為高電平,則上鎖存器的輸出變為低電平,從而將鎖存器輸出設置為1;如果數據輸入為低電平,則下鎖存器的輸出變為低電平,從而將輸出復位為 0。如果時鐘為對于多個數據信號持續高電平,僅考慮第一個數據輸入,而通過強制輸出鎖存器到其先前狀態來忽略剩余的數據輸入,因為只要時鐘信號為高電平,低輸入就處于活動狀態。

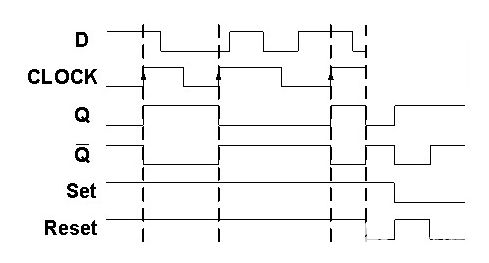

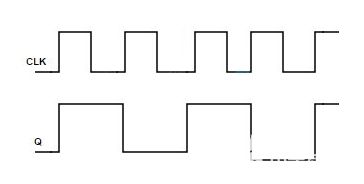

因此,外部鎖存器僅在時鐘為低邏輯時才存儲數據。邊沿觸發D觸發器的主要作用是保持輸出直到時鐘脈沖從低電平變為高電平,其時序圖如下所示。

主從D觸發器

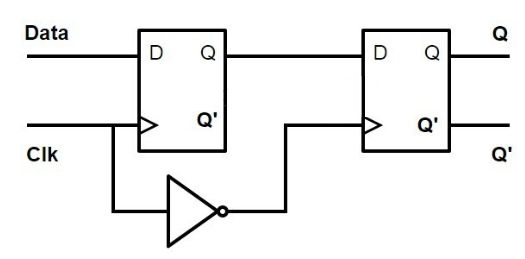

主從D觸發器可以通過串聯兩個門控D鎖存器并將反相使能輸入連接到兩個鎖存器中的任一個來設計,只有主鎖存器的變化會帶來從鎖存器的變化,所以這些被稱為主從觸發器。

根據設計,主從觸發器的整個電路要么在時鐘信號的上升沿觸發,要么在時鐘信號的下降沿觸發。主從D觸發器的符號表示,它在其下降沿響應時鐘,如下圖所示:

下圖所示的主從D觸發器是一個上升沿觸發器件,這意味著它將在時鐘輸入有上升沿時工作。第一個觸發器(主觸發器)連接負時鐘信號,即反相,第二個觸發器(從觸發器)與時鐘信號的雙反向連接,即正常時鐘信號。

下面簡單解釋上升沿觸發的主從D觸發器的操作過程。

如果時鐘為低電平,則主觸發器的使能信號為高電平。當時鐘信號由低變高時,主觸發器存儲來自D輸入的數據。同時在第二個觸發器,由于雙反相,使能信號隨著時鐘信號從低到高。在上升沿期間被主觸發器鎖定的數據被傳遞到從觸發器。

當時鐘信號從高電平變為低電平時,從觸發器將接收主觸發器輸出作為其輸入并改變其狀態。主觸發器將在下一個上升沿接受來自輸入的最新值。

主從D觸發器的時序圖如下所示。

另外,一個簡單的修改可以把上述設備變成下降沿觸發設備。通過消除沿時鐘信號路徑的第一個反相器,形成一個下降沿觸發的主從D觸發器即可,如下圖所示:

主要應用

D觸發器是使用最廣泛的觸發器之一。D觸發器的應用有許多,下面列出一部分:

數據存儲寄存器。

作為移位寄存器的數據傳輸。

分頻電路。

1、數據存儲寄存器

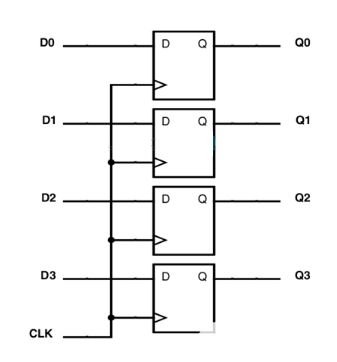

在數字電路中,數據通常存儲為一組比特,以數字和代碼表示。因此很容易在并行線上獲取數據并將數據同時存儲在一組觸發器中,按特定順序排列。寄存器是基本的多位數據設備。它們由連接數個D觸發器構成,從而可以存儲多位數據。

每個D觸發器都與各自的數據輸入相連。應用的時鐘輸入與所有觸發器相同,因此當應用正沿觸發時鐘信號時,所有觸發器都會同時存儲來自各自D輸入的數據。

2、數據傳輸寄存器

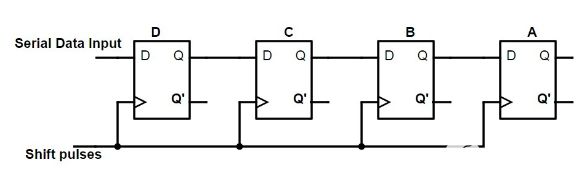

D觸發器也廣泛用于數據傳輸。為了傳輸數據,連接D觸發器以形成移位寄存器。具有相同時鐘信號的D觸發器級聯將形成移位寄存器。移位寄存器可以在不改變位序列的情況下移位數據。當施加時鐘脈沖時,一位數據被移位或傳輸。所以,移位寄存器可以臨時存儲數據。

使用D觸發器的4位存儲移位寄存器如下圖所示:

移位寄存器用于串行到并行和并行到串行的數據轉換。此外,它們還用作脈沖擴展器和延遲電路。

3、分頻電路

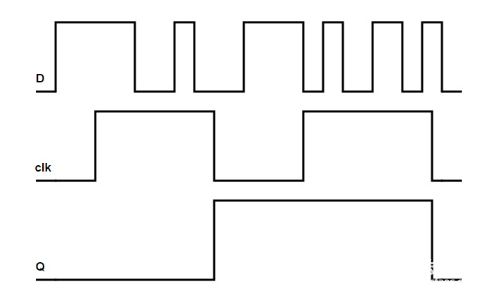

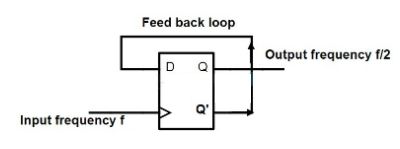

分頻電路是使用D觸發器開發的。這是D觸發器最重要的應用。在分頻電路中,D觸發器 (Q') 的狀態輸出作為閉環連接到數據輸入(D)。每兩個時鐘周期,兩個連續的CLK脈沖將使觸發器翻轉。

顧名思義,分頻器電路用于產生正好是輸入頻率一半的數字信號輸出。分頻電路一般用于異步計數器的設計。

電路的操作非常簡單。輸入數據信號由時鐘輸入信號計時。該電路將通過使用反饋回路(即連接到來自Q'的數據輸入)來執行輸入頻率的分頻。分頻器電路每兩個時鐘脈沖將輸入頻率除以2。

其實,可以通過將輸出與時鐘信號進行比較來解釋。

在某種情況下,當Q輸出為1時,Q' 輸出為0,然后來自D輸入的數據在時鐘輸入信號的下一個上升沿通過Q輸出計時。在這種情況下,輸出從高變為低。這里輸出保持不變,直到出現下一個正時鐘信號。類似地,Q' 輸出也被計時。由于時鐘輸入再次為1,這將改變觸發器的輸出狀態。

另外還可以觀察到,分頻器電路的輸出僅隨著輸入時鐘信號的上升沿而變化。由于每個上升沿在一個完整的時鐘周期內出現一次。因此,根據時鐘的上升沿,D觸發器將使輸入脈沖減半,即將時鐘脈沖除以2。

總結

簡單來說,D觸發器是一個具有存儲功能,且具有兩個穩定狀態的信息存儲元件,它是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。

此外,D觸發器在數字系統和計算機中有著廣泛的應用,其重要性不言而喻。需要記住的是,觸發器具有兩個穩定狀態,即"0"和"1",在一定的外界信號作用下,可以從一個穩定狀態翻轉到另一個穩定狀態。

-

寄存器

+關注

關注

31文章

5394瀏覽量

122173 -

D觸發器

+關注

關注

3文章

164瀏覽量

48258 -

觸發器

+關注

關注

14文章

2027瀏覽量

61591

發布評論請先 登錄

相關推薦

施密特觸發器電路及工作原理詳解_施密特觸發器特點_施密特觸發器的作用

常用邊沿觸發器電路結構和工作原理

評論