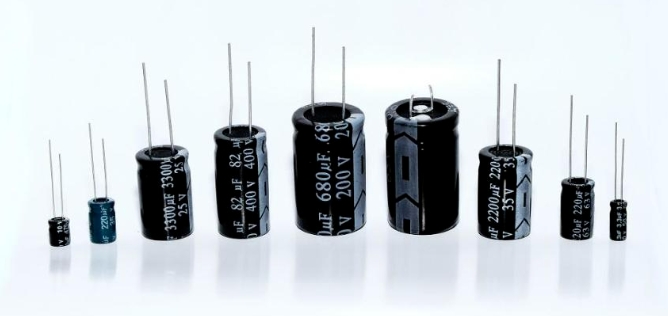

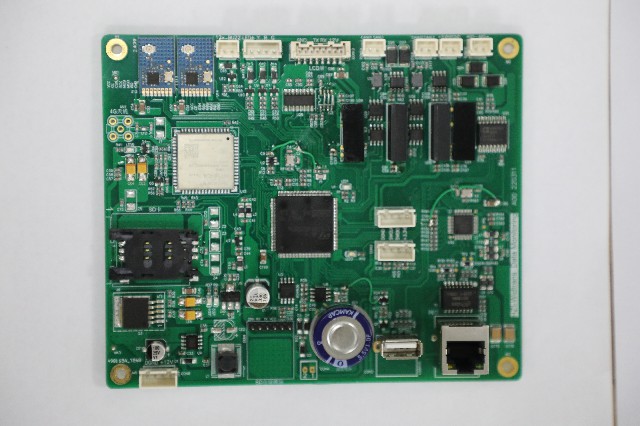

在PCBA打樣中,在滿足電路功能要求的前提下,應盡量使用敏感電壓閾值高的元器件。因為一個線路板的靜電、放電敏感度,取決于該線路板內敏感電壓閾值最低的元器件。

PCBA打樣使用元器件應注意的問題

1、限制輸出電流,能避免CMOS電路產生鎖定效應

鎖定效應是指在CMOS電路的內部結構上存在著寄生的PNP晶體管和NPN晶體管,而它們之間又恰好構成了一個寄生的PNPN可控硅結構。這種互鎖的正反饋結構可能因外部因素(如靜電放電)的觸發,就會在PNP管(或NPN管)上流過電流,再經過另一只寄生的NPN管(或PNP管)使電流放大,并且由于正反饋作用使電流越來越大而最終燒毀。可見,限制電流使其不能達到維持鎖定狀態的水平,是PCBA打樣時對CMOS器件要考慮的問題之一。

常用的解決辦法是用一只電阻器來把每一個輸出端同其電纜線隔開,并且用兩只高速開關二極管用電纜線鉗位到VDD(漏極電源)和VSS(源極電源)上。

在CMOS電路系統和機械接點之間有時需要長的輸入電纜線,這時便增加了受電磁干擾的可能性,應考慮使用濾波器網絡。同時,長的輸入線路必然伴隨著較大的分布電容和分布電感,很容易形成LC自激振蕩,導致保護網絡的二極管燒損。解決的方法是在輸入端串接一個電阻器,其阻值可按公式R=VDD/1mA選定。

3、RC網絡

在確實可行的地方,對于雙極性器件的敏感輸入端,使用電阻值較大的電阻器和至少100pF的電容器組成的RC網絡,可以降低靜電放電的影響。

4、避免CMOS器件輸入管腳懸空

在PCBA打樣中,要避免已焊接到線路板上的CMOS器件的輸入端被懸空。同時,要注意CMOS器件上所有不用的多余輸入引線不允許懸空。這是因為輸入端一旦懸空,輸入電位將處于不穩定狀態,不但會破壞電路的正常邏輯關系,而且易產生靜電擊穿、外界噪聲干擾等現象。對于多余輸入端要根據電路的功能分別處理。

審核編輯:湯梓紅

-

CMOS

+關注

關注

58文章

5724瀏覽量

235707 -

元器件

+關注

關注

112文章

4729瀏覽量

92510 -

PCBA

+關注

關注

23文章

1530瀏覽量

51645

發布評論請先 登錄

相關推薦

縮短SMT打樣交期,這些技巧你必須掌握!

SMT打樣揭秘:工藝邊如何確保加工精度與效率?

PCBA打樣必備:了解這些流程,輕松搞定電路板生產

PCB電路板元器件種類繁多,如何快速識別?

不得不知的pcba加工規則:確保元器件安全可靠

PCBA加工打樣流程詳解,看這一篇就夠了

如何有效減少PCBA的打樣時間

PCBA加工生產時需要注意哪些相關事項?

PCBA打樣元器件使用應該注意的4大問題

PCBA打樣元器件使用應該注意的4大問題

評論