以前看到過官網提供excel類型的IO BANK的示意圖,但是后來找不到了,就自己從軟件里面生成吧,看上去都差不多,而且還附帶解釋圖,挺好的。

FPGA Type: Cyclone V - 5CEFA7F27C6

Software: Quartus II 13.0 sp1

Steps

目前為前期評估階段,需要對I/O的資源按照不同的BANK處理,針對一些I/O的特殊功能,及數量需求,對PCB板子布局等進行整體的規劃。

PIN PLANNER

按照新建工程的向導,新建工程。這里默認已經選好指定FPGA型號了,在新建工程中選擇已選型號的FPGA。

選擇菜單欄Assignments

選擇Pin Planner

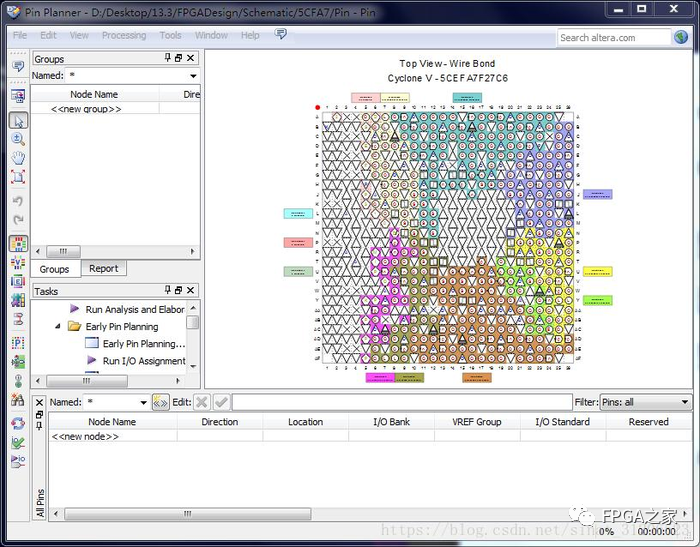

出現Pin Planner 對話框:

最大區域中的 Top View - Wire Bond 即為標注有不同BANK的IO區域分布。

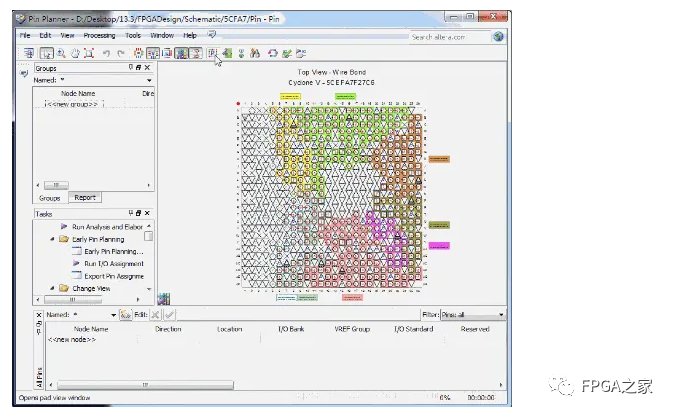

Tool Bar

工具欄中有顯示的選項以供點擊,也可通過菜單欄View--> show進行選擇,詳情見如下示意:

簡單介紹幾個Tool Bar 的按鈕:

Show Differential Pin Pair Connection: 可以觀察差分線的使用情況

Pin Legend Window:可以看到不同符號Pin對應的功能定義,一般的圓形為用戶IO;三角形向上為power,向下為GND;正方形為clock;五邊形為special configure;叉號為no connect。

Enable Live I/O check:可以檢查IO的電氣特征

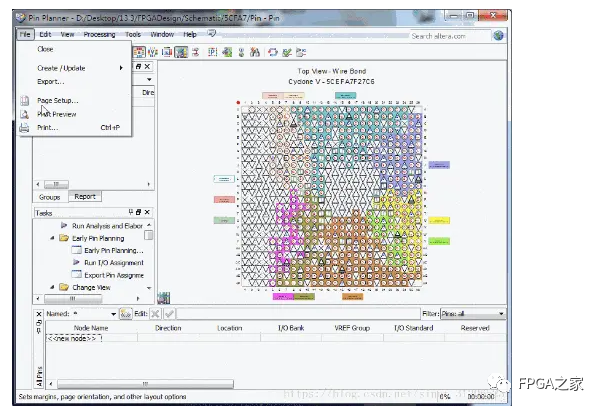

可以把IO BANK VIEW打印出來,注意打印的時候設置,這里頁面默認為A3的,需要根據打印機的設備進行調整,打印出來包含Pin Legend的List:

也可以打印為PDF檔,供在PC上進行查看,需要注意黑白打印出來的顏色等級可能會混在一起,所以不好看到IO BANK的分界,如果有條件,建議彩色打印。

IO COUNT

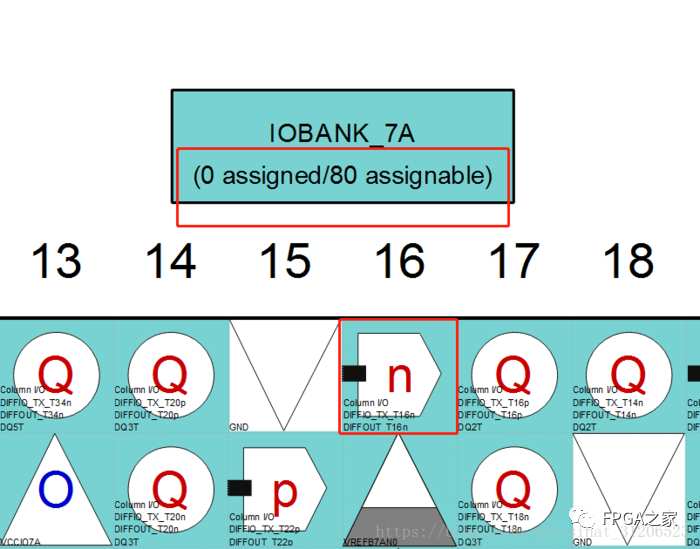

放大IO BANK VIEW會看到對于每個BANK 還會有詳細的已使用和未使用的IO 計數。

再仔細一看,在每一個Pin上還會有Pin Assignment,這個軟件設計時非常到位的。

I/O Distribute

因為每個BANK的Pin COUNT 并不是一致的,而且功能也是有特殊限制的,需要根據設計使用的資源,來對IO BANK進行合理的分配。

先從I/O COUNT上進行考慮,比如本設計需要使用3顆SDRAM,地址線復用,數據線不復用;這樣計算地址線一共16,數據線一共 12*3 ,這一起就52個IO了,再加上其他控制PIN 10*3 ,一共80 PIN +,這樣就只能選擇BANK 7或者BNAK 4了;

根據PLL的分布區域,要適當的選擇的區域,需要倍頻的模塊優先使用;

需要mini LVDS信號輸出,那么要看IO口定義,哪些可以輸出差分信號,需要注意差分信號的時鐘分布是固定的,需要結合差分時鐘來進行差分輸出的BANK;

需要注意每個BANK的電壓是該BANK內的VCCIO來決定的,結合IO輸出能力,需要對不同BANK提供不同的VCCIO;

After All

IO 分配問題還需要單獨列出來,這里主要講述怎么使用 Pin Planner 工具。

-

FPGA

+關注

關注

1630文章

21783瀏覽量

605018 -

pcb

+關注

關注

4324文章

23153瀏覽量

399089 -

軟件

+關注

關注

69文章

4999瀏覽量

87894

原文標題:FPGA IO BANK VIEW

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用Altera Interface Planner高效設計FPGA引腳布局

Quartus II打開Pin Planner后在管腳分配時有一項Reserved不知道里面列表的含義

例說FPGA連載32:PLL例化配置與LED之使用Pin Planner進行引腳分配

在quartus 15.0中如何將PPF文件導入到Pin Planner中

Quartus的pin planner 變成了只讀屬性

為ROS navigation功能包添加自定義的全局路徑規劃器(Global Path Planner)

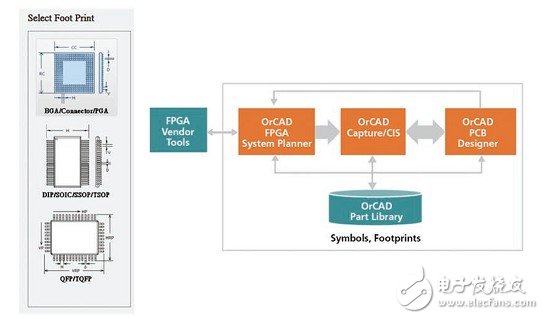

Allegro FPGA System Planner中文介紹

怎么使用 Pin Planner 工具

怎么使用 Pin Planner 工具

評論