現象

就是一個endpoint既有setup違反,又有hold違反;如果去修hold可能setup惡化;如果去修setup可能hold惡化。

成因

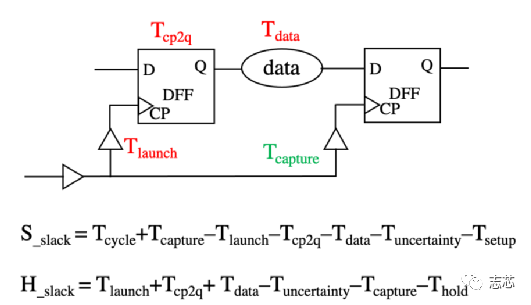

1、不同PVT條件下的cell delay variation較大;

2、某些cell的library setup time或library hold time特別大;

3、setup與hold的uncertainty或者derate約束較為嚴格或悲觀;

4、launch clock和capture clock的skew較大,OCV導致setup和hold都較難收斂;

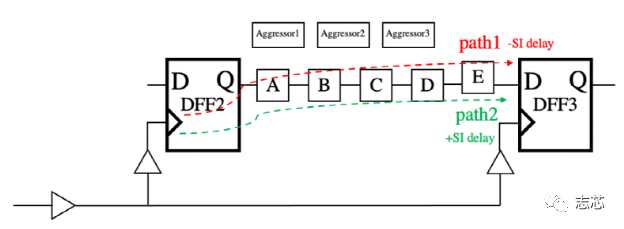

5、Timing path具有較大的cross-talk,因為串擾對setup和hold都是惡化的。

path種類

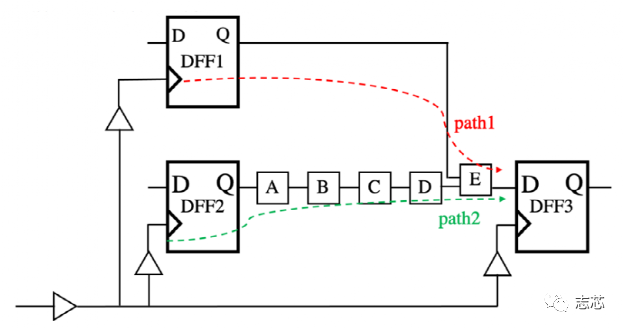

1、endpoint相同,startpoint不同:

Path1容易出現hold問題,path2容易出現setup問題;如果在path1和path2的commen part修timing就會導致另外一個path的惡化;所以應該分別在path1的非commen part修hold,在path2的非commen part修setup。

2、endpoint相同,startpoint相同,Launch clock和capture clock的skew較大:

Launch clock和capture clock的非commen part會吃掉大量OCV,使得setup和hold都惡化;所以需要思考一是是否可以做短非commen part,二是非commen part選用一些在不同PVT下cell delay variation較小的CK cell。

3、endpoint相同,startpoint相同,timing path上串擾較大:

串擾對setup和hold都是惡化的,可以使用“NDR rule” “shielding” “size drive-cell” “insert buffer”等方法fix cross-talk。

4、endpoint相同,startpoint相同,也沒有cross-talk等問題,但是有互卡:

首先看約束(包括uncertain、derate)是否合理,如果不合理需要校正。看看不同PVT library中setup/hold time是否差異很大,是否可以考慮換一下不同的lib cell。看看path上不同PVT條件下的cell delay variation是否巨大。如果是可以考慮:1換VT,一般LVT的cell在不同PVT下delay差異較小;2、換corner,是否可以考慮換收斂的corner;3換lib cell,換cell delay variation的cell。

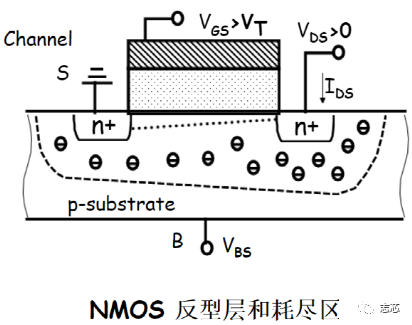

不同VTcell的delay差異

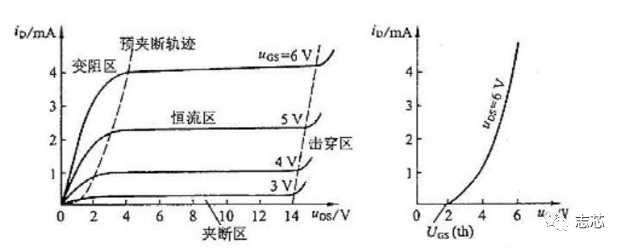

VT指的是MOS管的閾值電壓(threshold voltage)。當柵源電壓(Vgs)由0逐漸增大,直到MOS管溝道形成反型層(圖中的三角形)所需要的電壓為閾值電壓。

影響VT有如下因素。金半接觸電勢差:和柵極金屬方塊電阻以及襯底摻雜濃度有關;氧化層中的電荷密度;半導體費米勢;柵氧化層厚度;襯底摻雜濃度。源襯電壓。

在一般工藝中,一般是通過控制襯底摻雜濃度來實現不同VT的。

如果MOS管閾值電壓小,那么其飽和電流小,一般MOS管開啟瞬間在飽和區,飽和電流小意味著需要的逃逸掉的載流子更少;對于低VT的cell,顯然是更容易導通,而且其導通速度受PVT影響更小。

真的可以考慮換收斂corner

如下案例來自網友,原文鏈接如下,作者是“mnluan”。https://bbs.eetop.cn/thread-616584-1-1.html

說保hold,這樣的回答是對的,傳統思路就是保hold然后setup降頻。但是我想說,如果不允許降頻,你又會怎么辦呢?

分享一下我們當時做出的不一樣決定。在我們的案例中,有個800M的clock gate路徑,同時出現了hold和setup的violation。如果保hold,setup勢必要降頻,而我們的降頻無法做到從800M降頻到750M,要降頻就是直接降到了400M。而一旦降到400M,不要說性能了,功能都錯了。

因為對于送入芯片的數據根本處理不過來。這樣一來,即使保住了hold,也是個廢品。所以當時我們分析了整個產品,不單純是我們自己設計的芯片,查看板上其他芯片的文檔。發現有個芯片工作溫度最低是0度,而不是我們的-40度,于是首先調整了我們自己分析hold的corner,換成0度的庫分析,hold violation減少了一些,但還是violation。接著又從客戶那邊了解到,實際使用時,會給產品進行一段時間的預熱,所以我們大膽的把分析hold的corner調整到了TT下,hold check是過去的。

然后我們對工藝廠這些年生產我們芯片時的良率進行了分析,得出結論是,他家的Process大概率不在FF上,可以用TT分析。最后,我們保證了SS corner下的setup,用TT corner下的hold check代替了傳統FF corner下的hold check。

-

MOS管

+關注

關注

108文章

2418瀏覽量

66837 -

電壓

+關注

關注

45文章

5607瀏覽量

115790 -

Delay

+關注

關注

0文章

10瀏覽量

10894

原文標題:setup和hold互卡情況和解決辦法

文章出處:【微信號:數字ICer,微信公眾號:數字ICer】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Matlab的cell數組的問題

5 Cell to 10 Cell Li Protecto

BM209 Series Two-cell Li Batte

VIA/ 威盛 VT6410 /VT6420/ VT6421

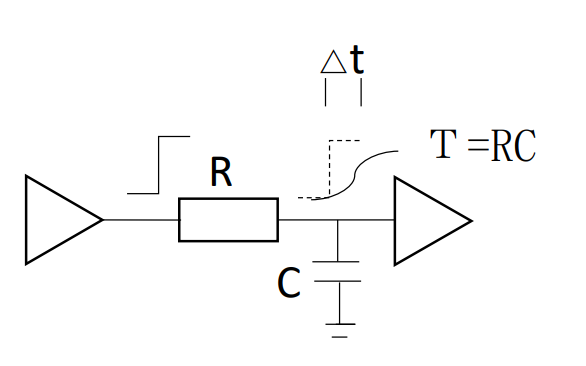

How Delay Lines Work

in-cell panel_In-Cell觸摸屏原理

全貼合In-Cell/On-Cell/OGS三種屏幕技術之間存在哪些差別

芯片延遲Delay測試的學習課件PDF文件免費下載

stm32 delay文件總結

不同VT cell的delay差異

不同VT cell的delay差異

評論