1、同步電路和異步電路的區(qū)別是什么?

同步電路:存儲(chǔ)電路中所有觸發(fā)器的時(shí)鐘輸入端都接同一個(gè)時(shí)鐘脈沖源,因而所有觸發(fā)器的狀態(tài)的變化都與所加的時(shí)鐘脈沖信號(hào)同步。

異步電路:電路沒有統(tǒng)一的時(shí)鐘,有些觸發(fā)器的時(shí)鐘輸入端與時(shí)鐘脈沖源相連,這有這些觸發(fā)器的狀態(tài)變化與時(shí)鐘脈沖同步,而其他的觸發(fā)器的狀態(tài)變化不與時(shí)鐘脈沖同步。

2、什么是"線與"邏輯,要實(shí)現(xiàn)它,在硬件特性上有什么具體要求?

將兩個(gè)門電路的輸出端并聯(lián)以實(shí)現(xiàn)與邏輯的功能成為線與。在硬件上,要用OC門來實(shí)現(xiàn),同時(shí)在輸出端口加一個(gè)上拉電阻。由于不用OC門可能使灌電流過大,而燒壞邏輯門。

3、解釋setup和hold time violation,并說明解決辦法?

Setup/hold time是測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。建立時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間。

輸入信號(hào)應(yīng)提前時(shí)鐘上升沿(如上升沿有效)T時(shí)間到達(dá)芯片,這個(gè)T就是建立時(shí)間-Setup time。如不滿足setup time,這個(gè)數(shù)據(jù)就不能被這一時(shí)鐘打入觸發(fā)器,只有在下一個(gè)時(shí)鐘上升沿,數(shù)據(jù)才能被打入觸發(fā)器。

保持時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間。如果hold time不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器。

建立時(shí)間(Setup Time)和保持時(shí)間(Hold time)。建立時(shí)間是指在時(shí)鐘邊沿前,數(shù)據(jù)信號(hào)需要保持不變的時(shí)間。

保持時(shí)間是指時(shí)鐘跳變邊沿后數(shù)據(jù)信號(hào)需要保持不變的時(shí)間。

如果數(shù)據(jù)信號(hào)在時(shí)鐘沿觸發(fā)前后持續(xù)的時(shí)間均超過建立和保持時(shí)間,那么超過量就分別被稱為建立時(shí)間裕量和保持時(shí)間裕量。

4、什么是競(jìng)爭(zhēng)與冒險(xiǎn)現(xiàn)象?怎樣判斷?如何消除?

在組合邏輯中,由于門的輸入信號(hào)通路中經(jīng)過了不同的延時(shí),導(dǎo)致到達(dá)該門的時(shí)間不一致叫競(jìng)爭(zhēng)。產(chǎn)生毛刺叫冒險(xiǎn)。

判斷方法:代數(shù)法、圖形法(是否有相切的卡諾圈)、表格法(真值表)。如果布爾式中有相反的信號(hào)則可能產(chǎn)生競(jìng)爭(zhēng)和冒險(xiǎn)現(xiàn)象。

冒險(xiǎn)分為偏“1”冒險(xiǎn)和偏“0”冒險(xiǎn)。

解決方法:一是添加布爾式的消去項(xiàng);二是在芯片外部加電容;三是加入選通信號(hào)。

SRAM:靜態(tài)隨機(jī)存取存儲(chǔ)器(Static Random-Access Memory,SRAM)是隨機(jī)存取存儲(chǔ)器的一種。

SSRAM:Synchronous Static Random Access Memory 的縮寫,即同步靜態(tài)隨機(jī)存取存儲(chǔ)器。

SDRAM:同步動(dòng)態(tài)隨機(jī)存取內(nèi)存(synchronous dynamic random-access memory,簡(jiǎn)稱SDRAM)是有一個(gè)同步接口的動(dòng)態(tài)隨機(jī)存取內(nèi)存(DRAM)。

SSRAM的所有訪問都在時(shí)鐘的上升/下降沿啟動(dòng)。地址、數(shù)據(jù)輸入和其它控制信號(hào)均與時(shí)鐘信號(hào)相關(guān)。這一點(diǎn)與異步SRAM不同,異步SRAM的訪問獨(dú)立于時(shí)鐘,數(shù)據(jù)輸入和輸出都由地址的變化控制。SDRAM:Synchronous DRAM同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器。

FPGA是可編程ASIC。

ASIC,專用集成電路,它是面向?qū)iT用途的電路,專門為一個(gè)用戶設(shè)計(jì)和制造的。根據(jù)一個(gè)用戶的特定要求,能以低研制成本,短、交貨周期供貨的全定制,半定制集成電路。

與門陣列等其它ASIC(Application Specific IC)相比,它們又具有設(shè)計(jì)開發(fā)周期短、設(shè)計(jì)制造成本低、開發(fā)工具先進(jìn)、標(biāo)準(zhǔn)產(chǎn)品無需測(cè)試、質(zhì)量穩(wěn)定以及可實(shí)時(shí)在線檢驗(yàn)等優(yōu)點(diǎn)。

7、單片機(jī)上電后沒有運(yùn)轉(zhuǎn),首先要檢查什么?

(1)首先應(yīng)該確認(rèn)電源電壓是否正常。用電壓表測(cè)量接地引腳跟電源引腳之間的電壓,看是否是電源電壓,例如常用的5V。

(2)接下來就是檢查復(fù)位引腳電壓是否正常。分別測(cè)量按下復(fù)位按鈕和放開復(fù)位按鈕的電壓值,看是否正確。

(3)然后再檢查晶振是否起振了,一般用示波器來看晶振引腳的波形;經(jīng)過上面幾點(diǎn)的檢查,一般即可排除故障了。

如果系統(tǒng)不穩(wěn)定的話,有時(shí)是因?yàn)殡娫礊V波不好導(dǎo)致的。在單片機(jī)的電源引腳跟地引腳之間接上一個(gè)0.1uF的電容會(huì)有所改善。如果電源沒有濾波電容的話,則需要再接一個(gè)更大濾波電容,例如220uF的。遇到系統(tǒng)不穩(wěn)定時(shí),就可以并上電容試試(越靠近芯片越好)。

8、什么是同步邏輯和異步邏輯?

同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。

9、你知道哪些常用邏輯電平?TTL與COMS電平可以直接互連嗎?

常用邏輯電平:12V,5V,3.3V。

TTL和CMOS不可以直接互連,由于TTL是在0.3-3.6V之間,而CMOS則是有在12V的有在5V的。CMOS輸出接到TTL是可以直接互連。TTL接到CMOS需要在輸出端口加一上拉電阻接到5V或者12V。

10、如何解決亞穩(wěn)態(tài)?

亞穩(wěn)態(tài)是指觸發(fā)器無法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既無法預(yù)測(cè)該單元的輸出電平,也無法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。

在亞穩(wěn)態(tài)期間,觸發(fā)器輸出一些中間級(jí)電平,或者可能處于振蕩狀態(tài),并且這種無用的輸出電平可以沿信號(hào)通道上的各個(gè)觸發(fā)器級(jí)聯(lián)式傳播下去。

解決方法主要有:

降低系統(tǒng)時(shí)鐘;

用反應(yīng)更快的觸發(fā)器(FF),鎖存器(LATCH);

引入同步機(jī)制,防止亞穩(wěn)態(tài)傳播;

改善時(shí)鐘質(zhì)量,用邊沿變化快速的時(shí)鐘信號(hào);

使用工藝好、時(shí)鐘周期裕量大的器件。

11、鎖存器、觸發(fā)器、寄存器三者的區(qū)別?

觸發(fā)器:能夠存儲(chǔ)一位二值信號(hào)的基本單元電路統(tǒng)稱為“觸發(fā)器”。

鎖存器:一位觸發(fā)器只能傳送或存儲(chǔ)一位數(shù)據(jù),而在實(shí)際工作中往往希望一次傳送或存儲(chǔ)多位數(shù)據(jù)。為此可把多個(gè)觸發(fā)器的時(shí)鐘輸入端CP連接起來,用一個(gè)公共的控制信號(hào)來控制,而各個(gè)數(shù)據(jù)端口仍然是各處獨(dú)立地接收數(shù)據(jù)。這樣所構(gòu)成的能一次傳送或存儲(chǔ)多位數(shù)據(jù)的電路就稱為“鎖存器”。

寄存器:在實(shí)際的數(shù)字系統(tǒng)中,通常把能夠用來存儲(chǔ)一組二進(jìn)制代碼的同步時(shí)序邏輯電路稱為寄存器。由于觸發(fā)器內(nèi)有記憶功能,因此利用觸發(fā)器可以方便地構(gòu)成寄存器。由于一個(gè)觸發(fā)器能夠存儲(chǔ)一位二進(jìn)制碼,所以把n個(gè)觸發(fā)器的時(shí)鐘端口連接起來就能構(gòu)成一個(gè)存儲(chǔ) n位二進(jìn)制碼的寄存器。

區(qū)別:從寄存數(shù)據(jù)的角度來看,寄存器和鎖存器的功能是相同的,它們的區(qū)別在于寄存器是同步時(shí)鐘控制,而鎖存器是電位信號(hào)控制。

可見,寄存器和鎖存器具有不同的應(yīng)用場(chǎng)合,取決于控制方式以及控制信號(hào)和數(shù)據(jù)信號(hào)之間的時(shí)間關(guān)系:若數(shù)據(jù)信號(hào)有效一定滯后于控制信號(hào)有效,則只能使用鎖存器;若數(shù)據(jù)信號(hào)提前于控制信號(hào)到達(dá)并且要求同步操作,則可用寄存器來存放數(shù)據(jù)。

12、IC設(shè)計(jì)中同步復(fù)位與異步復(fù)位的區(qū)別?

異步復(fù)位是不受時(shí)鐘影響的,在一個(gè)芯片系統(tǒng)初始化(或者說上電)的時(shí)候需要這么一個(gè)全局的信號(hào)來對(duì)整個(gè)芯片進(jìn)行整體的復(fù)位,到一個(gè)初始的確定狀態(tài)。而同步復(fù)位需要在時(shí)鐘沿來臨的時(shí)候才會(huì)對(duì)整個(gè)系統(tǒng)進(jìn)行復(fù)位。

13、多時(shí)域設(shè)計(jì)中,如何處理信號(hào)跨時(shí)域?

不同的時(shí)鐘域之間信號(hào)通信時(shí)需要進(jìn)行同步處理,這樣可以防止新時(shí)鐘域中第一級(jí)觸發(fā)器的亞穩(wěn)態(tài)信號(hào)對(duì)下級(jí)邏輯造成影響,其中對(duì)于單個(gè)控制信號(hào)可以用兩級(jí)同步器,如電平、邊沿檢測(cè)和脈沖,對(duì)多位信號(hào)可以用FIFO、雙口RAM、握手信號(hào)等。

跨時(shí)域的信號(hào)要經(jīng)過同步器同步,防止亞穩(wěn)態(tài)傳播。例如:時(shí)鐘域1中的一個(gè)信號(hào),要送到時(shí)鐘域2,那么在這個(gè)信號(hào)送到時(shí)鐘域2之前,要先經(jīng)過時(shí)鐘域2的同步器同步后,才能進(jìn)入時(shí)鐘域2。

這個(gè)同步器就是兩級(jí)d觸發(fā)器,其時(shí)鐘為時(shí)鐘域2的時(shí)鐘。這樣做是怕時(shí)鐘域1中的這個(gè)信號(hào),可能不滿足時(shí)鐘域2中觸發(fā)器的建立保持時(shí)間,而產(chǎn)生亞穩(wěn)態(tài),因?yàn)樗鼈冎g沒有必然關(guān)系,是異步的。

這樣做只能防止亞穩(wěn)態(tài)傳播,但不能保證采進(jìn)來的數(shù)據(jù)的正確性。所以通常只同步很少位數(shù)的信號(hào)。比如控制信號(hào),或地址。當(dāng)同步的是地址時(shí),一般該地址應(yīng)采用格雷碼,因?yàn)楦窭状a每次只變一位,相當(dāng)于每次只有一個(gè)同步器在起作用,這樣可以降低出錯(cuò)概率,象異步FIFO的設(shè)計(jì)中,比較讀寫地址的大小時(shí),就是用這種方法。

如果兩個(gè)時(shí)鐘域之間傳送大量的數(shù)據(jù),可以用異步FIFO來解決問題。

我們可以在跨越ClockDomain時(shí)加上一個(gè)低電平使能的LockupLatch以確保Timing能正確無誤。

14、給了reg的setup、hold時(shí)間,求中間組合邏輯的delay范圍?

Setup/hold time 是測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。建立時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間。

輸入信號(hào)應(yīng)提前時(shí)鐘上升沿(如上升沿有效)T時(shí)間到達(dá)芯片,這個(gè)T就是建立時(shí)間-Setup time.如不滿足setup time,這個(gè)數(shù)據(jù)就不能被這一時(shí)鐘打入觸發(fā)器,只有在下一個(gè)時(shí)鐘上升沿,數(shù)據(jù)才能被打入觸發(fā)器。

保持時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間。時(shí)hold time不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器。即delay

15、時(shí)鐘周期為T,觸發(fā)器D1的建立時(shí)間最大為T1max,最小為T1min,組合邏輯電路最大延遲為T2max,最小為T2min。觸發(fā)器D2的建立時(shí)間T3和保持時(shí)間應(yīng)滿足什么條件?

建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿被打入觸發(fā)器;保持時(shí)間(hold time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果保持時(shí)間不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器。

Tffpd:觸發(fā)器輸出的響應(yīng)時(shí)間,也就是觸發(fā)器的輸出在clk時(shí)鐘上升沿到來之后多長的時(shí)間內(nèi)發(fā)生變化并且穩(wěn)定,也可以理解為觸發(fā)器的輸出延時(shí)。

Tcomb:觸發(fā)器的輸出經(jīng)過組合邏輯所需要的時(shí)間,也就是題目中的組合邏輯延遲。Tsetup:建立時(shí)間Thold:保持時(shí)間Tclk:時(shí)鐘周期。

建立時(shí)間容限:相當(dāng)于保護(hù)時(shí)間,這里要求建立時(shí)間容限大于等于0。保持時(shí)間容限:保持時(shí)間容限也要求大于等于0。

16、說說靜態(tài)、動(dòng)態(tài)時(shí)序模擬的優(yōu)缺點(diǎn)?

靜態(tài)時(shí)序分析是采用窮盡分析方法來提取出整個(gè)電路存在的所有時(shí)序路徑,計(jì)算信號(hào)在這些路徑上的傳播延時(shí),檢查信號(hào)的建立和保持時(shí)間是否滿足時(shí)序要求,通過 對(duì)最大路徑延時(shí)和最小路徑延時(shí)的分析,找出違背時(shí)序約束的錯(cuò)誤。

它不需要輸入向量就能窮盡所有的路徑,且運(yùn)行速度很快、占用內(nèi)存較少,不僅可以對(duì)芯片設(shè)計(jì) 進(jìn)行全面的時(shí)序功能檢查,而且還可利用時(shí)序分析的結(jié)果來優(yōu)化設(shè)計(jì),因此靜態(tài)時(shí)序分析已經(jīng)越來越多地被用到數(shù)字集成電路設(shè)計(jì)的驗(yàn)證中。

動(dòng)態(tài)時(shí)序模擬就是通常的仿真,因?yàn)椴豢赡墚a(chǎn)生完備的測(cè)試向量,覆蓋門級(jí)網(wǎng)表中的每一條路徑。因此在動(dòng)態(tài)時(shí)序分析中,無法暴露一些路徑上可能存在的時(shí)序問題。

17、LATCH和DFF的概念和區(qū)別?

(1)概念

電平敏感的存儲(chǔ)器件稱為鎖存器;分高電平鎖存器和低電平鎖存器,用于不同時(shí)鐘間的同步。

有交叉耦合的門構(gòu)成的雙穩(wěn)態(tài)存儲(chǔ)器件稱為觸發(fā)器,分為上升沿觸發(fā)和下降沿觸發(fā),可認(rèn)為是兩個(gè)不同電平敏感的鎖存器串聯(lián)而成,前一個(gè)鎖存器決定了觸發(fā)器的建立時(shí)間,后一個(gè)鎖存器決定了觸發(fā)器的保持時(shí)間。

(2)區(qū)別

latch由電平觸發(fā),非同步控制。在使能信號(hào)有效時(shí)latch相當(dāng)于通路,在使能信號(hào)無效時(shí)latch保持輸出狀態(tài)。DFF由時(shí)鐘沿觸發(fā),同步控制。

latch容易產(chǎn)生毛刺(glitch),DFF則不易產(chǎn)生毛刺。

如果使用門電路來搭建latch和DFF,則latch消耗的門資源比DFF要少,這是latch比DFF優(yōu)越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因?yàn)镕PGA中沒有標(biāo)準(zhǔn)的latch單元,但有DFF單元,一個(gè)LATCH需要多個(gè)LE才能實(shí)現(xiàn)。

latch將靜態(tài)時(shí)序分析變得極為復(fù)雜。

一般的設(shè)計(jì)規(guī)則是:在絕大多數(shù)設(shè)計(jì)中避免產(chǎn)生latch。它會(huì)讓您設(shè)計(jì)的時(shí)序完蛋,并且它的隱蔽性很強(qiáng),非老手不能查出。latch最大的危害在于不能過濾毛刺。這對(duì)于下一級(jí)電路是極其危險(xiǎn)的。所以,只要能用D觸發(fā)器的地方,就不用latch。

有些地方?jīng)]有時(shí)鐘,也只能用latch了。比如現(xiàn)在用一個(gè)clk接到latch的使能端(假設(shè)是高電平使能),這樣需要的setup時(shí)間,就是數(shù)據(jù)在時(shí)鐘的下降沿之前需要的時(shí)間,但是如果是一個(gè)DFF,那么setup時(shí)間就是在時(shí)鐘的上升沿需要的時(shí)間。

這就說明如果數(shù)據(jù)晚于控制信號(hào)的情況下,只能用 latch,這種情況就是,前面所提到的latch timing borrow。基本上相當(dāng)于借了一個(gè)高電平時(shí)間。也就是說,latch借的時(shí)間也是有限的。

18、latch與register的區(qū)別,為什么現(xiàn)在多用register?行為級(jí)描述中l(wèi)atch如何產(chǎn)生的?

Latch(鎖存器)是電平觸發(fā),Register(寄存器)是邊沿觸發(fā),register在同一時(shí)鐘邊沿觸發(fā)下動(dòng)作,符合同步電路的設(shè)計(jì)思想,而latch則屬于異步電路設(shè)計(jì),往往會(huì)導(dǎo)致時(shí)序分析困難,不適當(dāng)?shù)膽?yīng)用latch則會(huì)大量浪費(fèi)芯片資源。

19、什么是鎖相環(huán)(PLL)?鎖相環(huán)的工作原理是什么?

鎖相環(huán)是一種反饋電路,其作用是使得電路上的時(shí)鐘和某一外部時(shí)鐘的相位同步。PLL通過比較外部信號(hào)的相位和由壓控晶振(VCXO)的相位來實(shí)現(xiàn)同步的,在比較的過程中,鎖相環(huán)電路會(huì)不斷根據(jù)外部信號(hào)的相位來調(diào)整本地晶振的時(shí)鐘相位,直到兩個(gè)信號(hào)的相位同步。

在數(shù)據(jù)采集系統(tǒng)中,鎖相環(huán)是一種非常有用的同步技術(shù),因?yàn)橥ㄟ^鎖相環(huán),可以使得不同的數(shù)據(jù)采集板卡共享同一個(gè)采樣時(shí)鐘。

因此,所有板卡上各自的本地80MHz和20MHz時(shí)基的相位都是同步的,從而采樣時(shí)鐘也是同步的。因?yàn)槊繅K板卡的采樣時(shí)鐘都是同步的,所以都能嚴(yán)格地在同一時(shí)刻進(jìn)行數(shù)據(jù)采集。

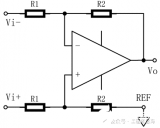

20、基本放大電路的種類及優(yōu)缺點(diǎn),廣泛采用差分結(jié)構(gòu)的原因?

基本放大電路按其接法的不同可以分為共發(fā)射極放大電路、共基極放大電路和共集電極放大電路,簡(jiǎn)稱共基、共射、共集放大電路。

共射放大電路既能放大電流又能放大電壓,輸入電阻在三種電路中居中,輸出電阻較大,頻帶較窄。常做為低頻電壓放大電路的單元電路。

共基放大電路只能放大電壓不能放大電流,輸入電阻小,電壓放大倍數(shù)和輸出電阻與共射放大電路相當(dāng),頻率特性是三種接法中最好的電路。常用于寬頻帶放大電路。

共集放大電路只能放大電流不能放大電壓,是三種接法中輸入電阻最大、輸出電阻最小的電路,并具有電壓跟隨的特點(diǎn)。常用于電壓放大電路的輸入級(jí)和輸出級(jí),在功率放大電路中也常采用射極輸出的形式。

審核編輯 黃昊宇

-

電路

+關(guān)注

關(guān)注

172文章

5936瀏覽量

172481

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電橋電路的常見錯(cuò)誤分析

從暴雨到積水,地埋式路面檢測(cè)儀實(shí)時(shí)掌握路面情況

Redis使用重要的兩個(gè)機(jī)制:Reids持久化和主從復(fù)制

【面試題】人工智能工程師高頻面試題匯總:機(jī)器學(xué)習(xí)深化篇(題目+答案)

【面試題】人工智能工程師高頻面試題匯總:Transformer篇(題目+答案)

人工智能工程師高頻面試題匯總——機(jī)器學(xué)習(xí)篇

硬件面試電路分析(含拓展電路分享)

路面施工攤鋪壓實(shí)監(jiān)測(cè)管理系統(tǒng)

面試嵌入式工作,會(huì)被問什么問題?

常見串口通信的幾個(gè)問題請(qǐng)教?

干貨 | 電路設(shè)計(jì)中如何減少ESD?

差分放大電路的缺點(diǎn),你知道幾個(gè)?

嵌入式領(lǐng)域面試挑戰(zhàn):這7個(gè)問題,你能答對(duì)幾個(gè)?

干貨 | 常見電路面試題20道,試試你能答對(duì)幾個(gè)!

干貨 | 常見電路面試題20道,試試你能答對(duì)幾個(gè)!

評(píng)論